Downloaded from UvA-DARE, the institutional repository of the University of Amsterdam (UvA) http://hdl.handle.net/11245/2.160789

File ID uvapub:160789

Filename Thesis Version final

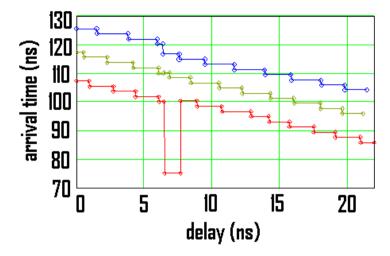

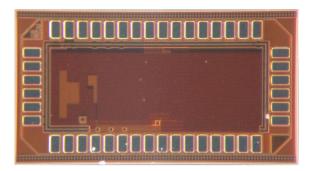

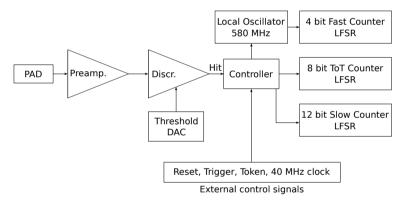

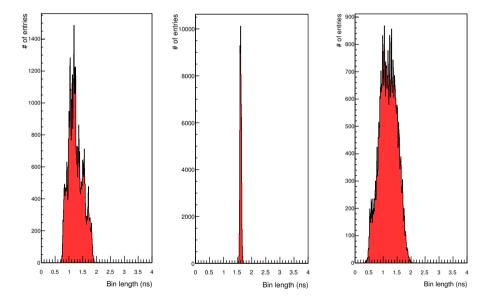

#### SOURCE (OR PART OF THE FOLLOWING SOURCE):

Type PhD thesis

Title It is about time: Design and test of a per-pixel high-resolution TDC

Author(s) F. Zappon Faculty FNWI Year 2015

#### FULL BIBLIOGRAPHIC DETAILS:

http://hdl.handle.net/11245/1.474707

#### Copyright

It is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), other than for strictly personal, individual use, unless the work is under an open content licence (like Creative Commons).

# It is about time

Design and test of a per-pixel high-resolution TDC

# It is about time

Design and test of a per-pixel high-resolution TDC

Francesco Zappon

# It is about time

Design and test of a per-pixel high-resolution TDC

#### ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad van doctor

aan de Universiteit van Amsterdam

op gezag van de Rector Magnificus

prof. dr. D.C. van den Boom

ten overstaan van een door het college voor promoties ingestelde

commissie, in het openbaar te verdedigen in de Aula der

Universiteit

op Vrijdag 5 Juni 2015, te 11.00 uur

door

Francesco Zappon

geboren te Noventa Vicentina, Italië.

#### Promotiecommissie:

Promotor: prof. dr. ir. E.N. Koffeman Supervisor: dr. M.G. van Beuzekom

Overige Leden: prof. dr. A. Pellegrino

prof. dr. J.F.J. van den Brand

ir. V. Gromov prof. dr. F.L. Linde prof. dr. ir. P.J. de Jong prof. dr. P.M. Kooijman

Faculteit der Natuurwetenschappen, Wiskunde en Informatica

This work was supported by the Marie Curie Particle Detector (MC-PAD) Initial Training Network (ITN) which is part of the European Union's Research and Innovation funding program FP7 and by the Foundation for Fundamental Research on Matter (FOM). It was carried out at the National Institute for Subatomic Physics (Nikhef) in Amsterdam, the Netherlands.

Copyright © 2015 by Francesco Zappon

Typeset by LATEX.

Printed and Lay Out by: Proefschriftmaken.nl | | Uitgeverij BOXPress

Published by: Uitgeverij BOXPress, 's-Hertogenbosch

# **Contents**

| In | trodu | uction                                                                | 7        |

|----|-------|-----------------------------------------------------------------------|----------|

| 1  | Pixe  | el detectors in particle physics                                      | 9        |

|    | 1.1   | Introduction                                                          | 9        |

|    | 1.2   | Tracking silicon detector: overview                                   | 10       |

|    | 1.3   | Modern silicon detectors at the LHC                                   | 14       |

|    | 1.4   | The Atlas pixel detector                                              | 16       |

|    |       | 1.4.1 Atlas upgrade                                                   | 17       |

|    | 1.5   | The CMS pixel detector                                                | 19       |

|    | 1.6   | The LHCb Vertex Locator                                               | 21       |

|    |       | 1.6.1 VELO upgrade: VeloPix                                           | 23       |

|    | 1.7   | The Medipix family                                                    | 24       |

|    | 1.8   | The Timepix chip                                                      | 25       |

|    | 1.9   | Conclusion                                                            | 27       |

| 2  | Cas   | conservate and high recolution time measurements                      | 29       |

| 2  | 2.1   | seous pixels and high resolution time measurements  GridPix detectors | 29<br>29 |

|    |       |                                                                       | 32       |

|    | 2.2   | Gas properties                                                        | 32       |

|    |       | 0                                                                     | 34       |

|    |       |                                                                       | 37       |

|    |       |                                                                       | 38       |

|    | 2.2   | 2.2.4 Signal development                                              | 39       |

|    | 2.3   | Basic frontend characteristics                                        | 39<br>40 |

|    |       | 2.3.1 Charge sensitive amplifier                                      | 40       |

|    |       | 2.3.2 Shaper                                                          |          |

|    | 2.4   | 2.3.3 Discriminator                                                   | 41<br>42 |

|    | 2.4   | GridPix at work: an example                                           |          |

|    | 2.5   | High precision time measurements                                      | 43       |

|    |       | 2.5.1 Ramp interpolate                                                | 44       |

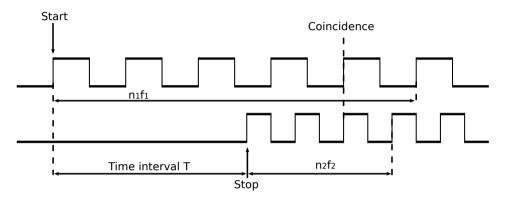

|    |       | 2.5.2 Vernier line                                                    | 44       |

4 CONTENTS

|   |      | 2.5.3   | Delay line                                       | 45  |

|---|------|---------|--------------------------------------------------|-----|

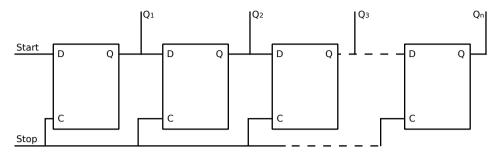

|   |      | 2.5.4   | Counter method                                   | 46  |

|   |      | 2.5.5   | Nutt technique                                   | 47  |

| 3 | Prot | otype   | TDC: Gossipo-3                                   | 49  |

|   | 3.1  | Introd  | duction                                          | 49  |

|   | 3.2  | GOSS    | SIPO chips: overview                             | 49  |

|   | 3.3  | Single  | e pixel logic                                    | 51  |

|   |      | 3.3.1   | Analog frontend                                  | 52  |

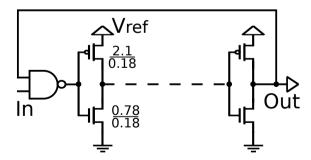

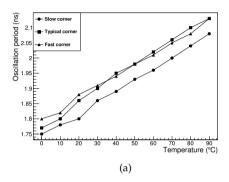

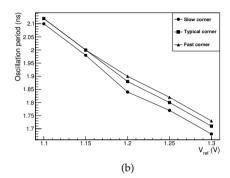

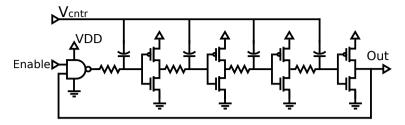

|   |      | 3.3.2   | Oscillator                                       | 56  |

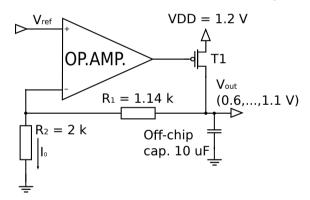

|   |      | 3.3.3   | Low Drop Out regulators                          | 57  |

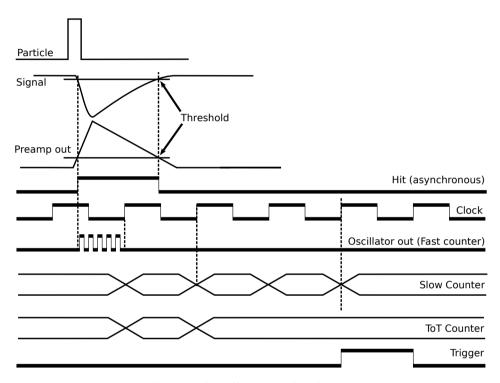

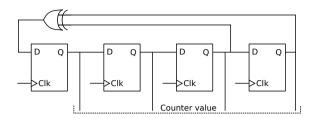

|   |      | 3.3.4   | Counters                                         | 59  |

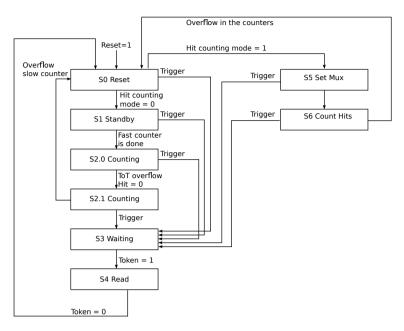

|   |      | 3.3.5   | Controller                                       | 61  |

|   | 3.4  | Conve   | erter characterization                           | 63  |

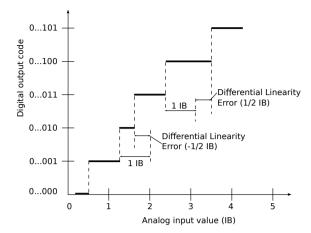

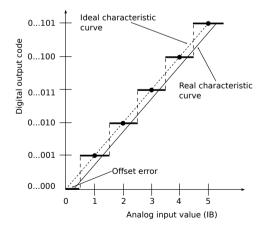

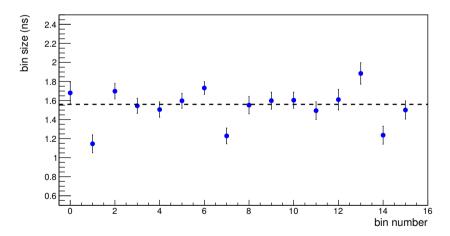

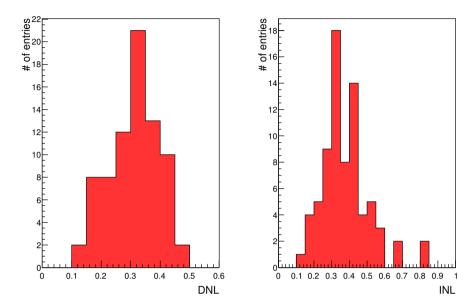

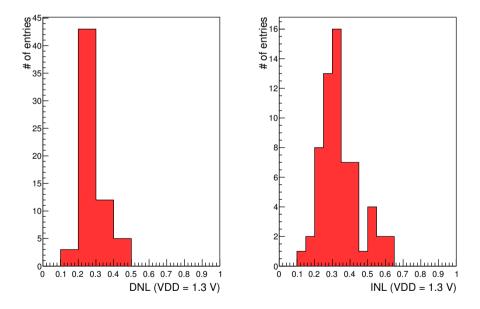

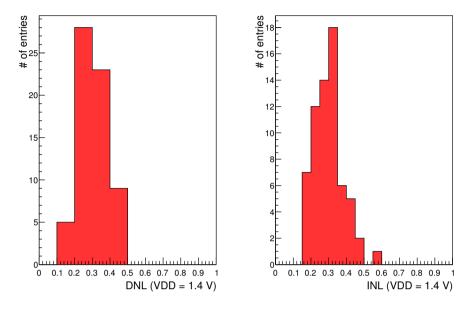

|   |      | 3.4.1   | Differential Non Linearity                       | 63  |

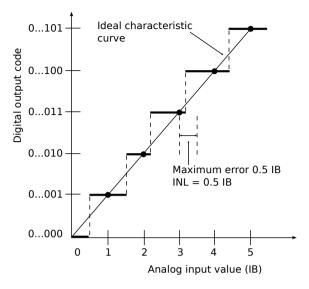

|   |      | 3.4.2   | Integral Non Linearity                           | 64  |

|   |      | 3.4.3   | Offset error                                     | 65  |

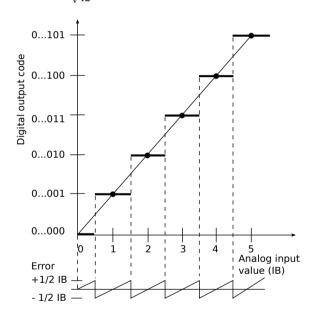

|   |      | 3.4.4   | Quantization effects                             | 66  |

|   | 3.5  | Error   | function                                         | 66  |

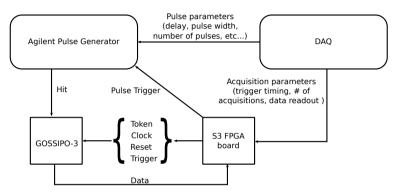

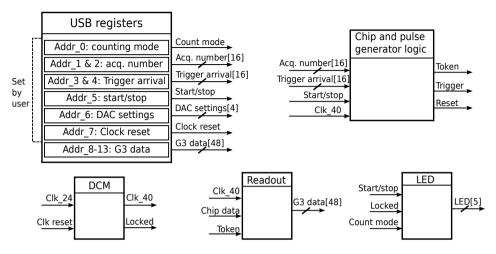

|   | 3.6  | Test e  | environment                                      | 67  |

|   | 3.7  | Test re | esults                                           |     |

|   |      | 3.7.1   | Analog frontend                                  | 69  |

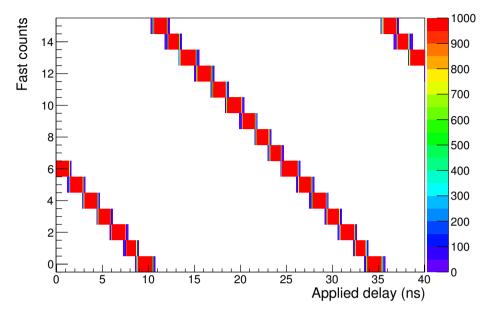

|   |      | 3.7.2   | Time to Digital Converter (TDC) characterization | 77  |

|   |      | 3.7.3   | Low Drop Out regulators                          | 82  |

|   | 3.8  | Concl   | lusion                                           | 84  |

| 4 | Prot | otype   | TDC: Gossipo-4                                   | 87  |

|   | 4.1  |         | duction                                          |     |

|   | 4.2  | Super   | Pixel: specifications and design                 | 87  |

|   | 4.3  | Pixel . |                                                  | 89  |

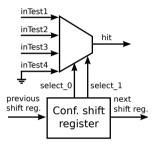

|   |      | 4.3.1   | Input selection                                  | 90  |

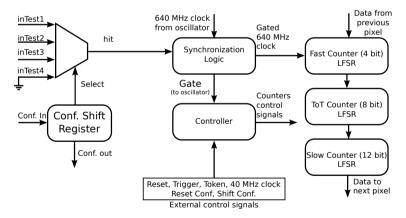

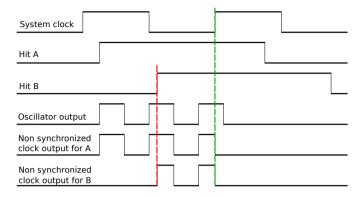

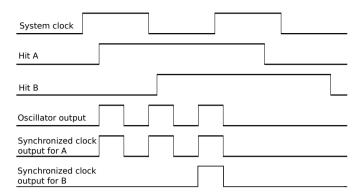

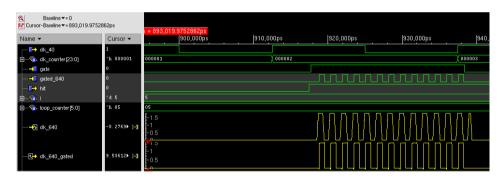

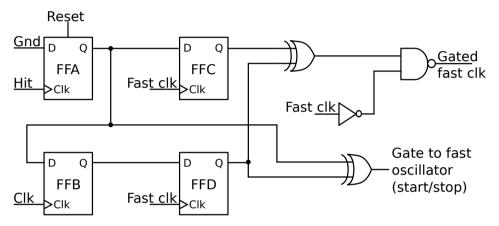

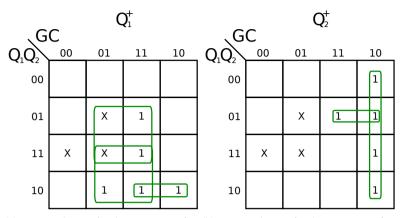

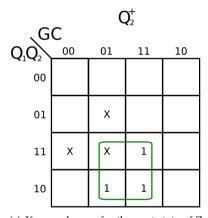

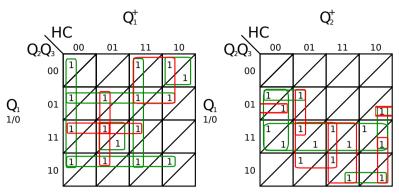

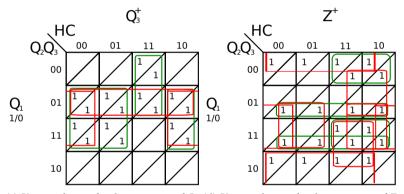

|   |      | 4.3.2   | Synchronization Logic                            | 90  |

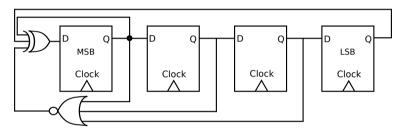

|   |      | 4.3.3   | Counters                                         | 92  |

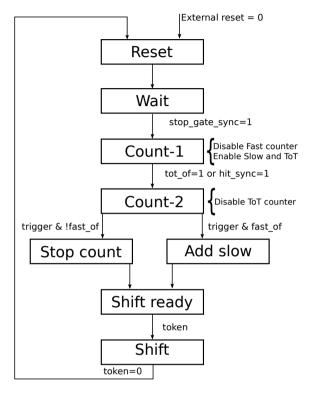

|   |      | 4.3.4   | Controller                                       |     |

|   | 4.4  | Oscill  | lator                                            | 96  |

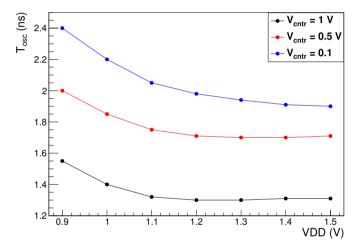

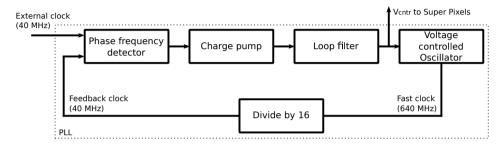

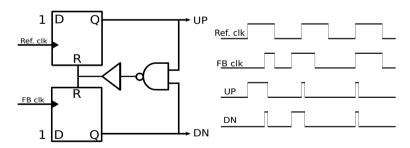

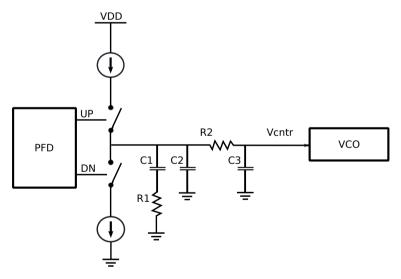

|   | 4.5  | Phase   | Locked Loop                                      | 97  |

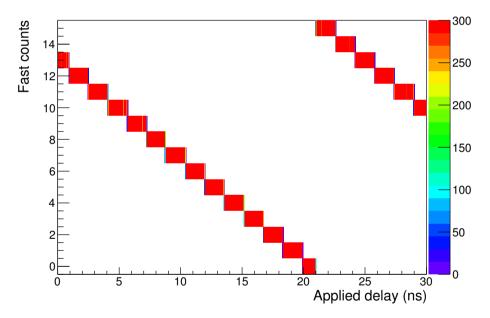

|   | 4.6  | GOSS    | SIPO-4 characterization                          |     |

|   |      | 4.6.1   | Single pixel characterization                    |     |

|   |      | 4.6.2   | Full Super Pixel response                        |     |

|   |      | 4.6.3   | Multiple hits test                               |     |

|   |      | 4.6.4   | Phase Locked Loop measurements                   | 106 |

CONTENTS 5

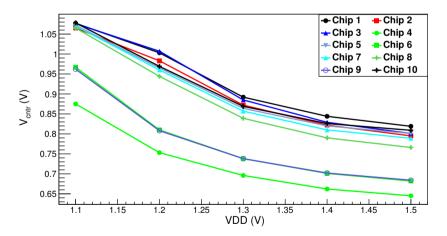

|    |                | 4.6.5    | Supply voltage dependence             |       |  |

|----|----------------|----------|---------------------------------------|-------|--|

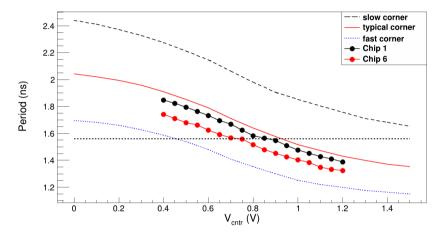

|    |                | 4.6.6    | Oscillator control voltage dependence | . 109 |  |

|    |                | 4.6.7    | Control voltage scan                  | . 111 |  |

|    | 4.7            | Concl    | usion                                 | . 113 |  |

| 5  | Tim            | epix3 f  | or a GridPix detector                 | 115   |  |

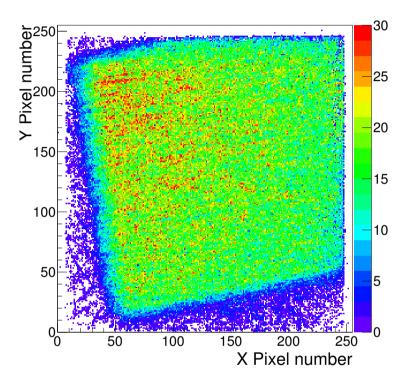

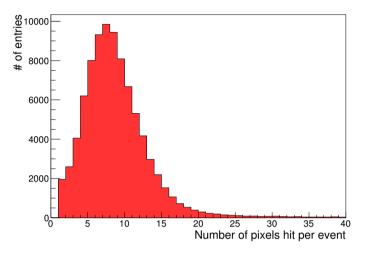

|    | 5.1            | •        | test setup                            | . 115 |  |

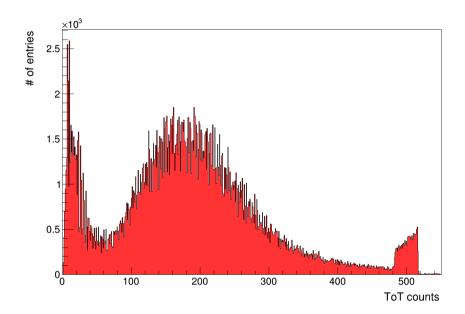

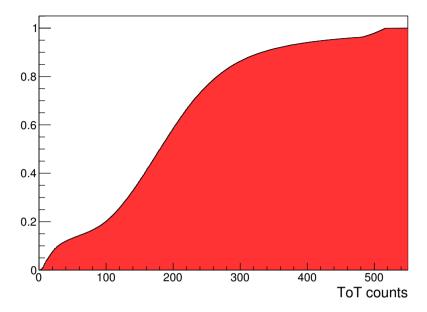

|    |                | 5.1.1    | Run characteristics                   |       |  |

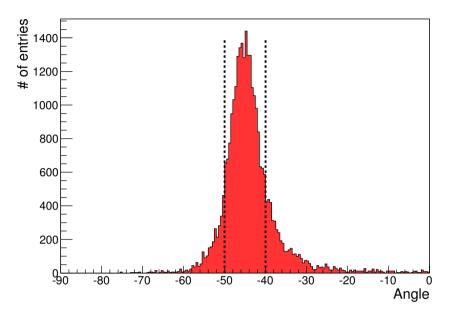

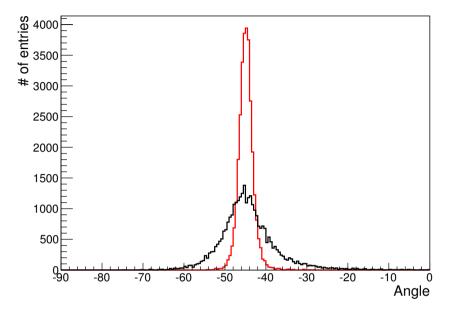

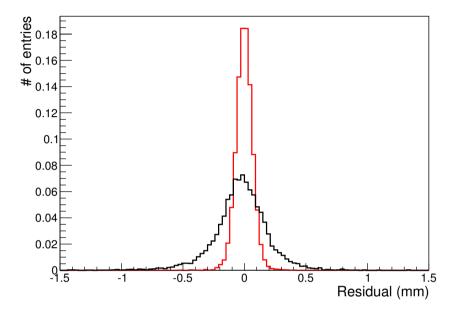

|    |                | 5.1.2    | Angle distribution                    |       |  |

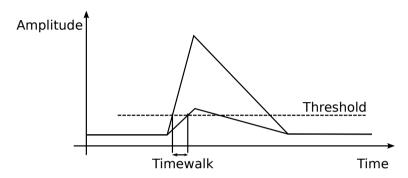

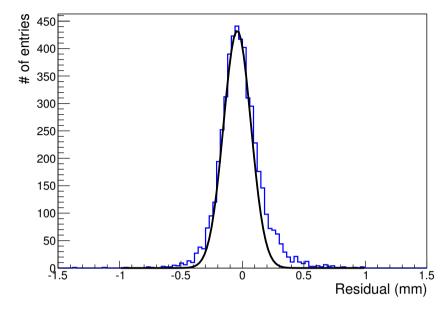

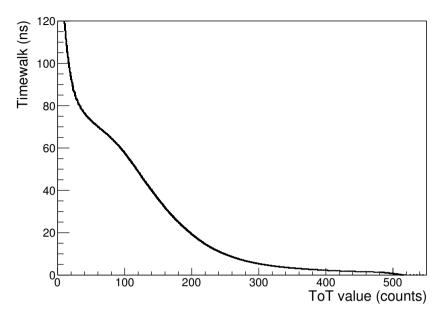

|    |                | 5.1.3    | Diffusion and timewalk                | . 119 |  |

|    |                | 5.1.4    | Simulations                           | . 124 |  |

|    |                | 5.1.5    | Simulations with ToT                  | . 125 |  |

|    | 5.2            | Timep    | vix3                                  | . 127 |  |

|    |                | 5.2.1    | Super pixel and pixel cell            | . 129 |  |

|    |                | 5.2.2    | Synchronization logic                 |       |  |

|    | 5.3            | Chara    | cterization of Timepix3               | . 132 |  |

|    | 5.4            | Concl    | usion                                 | . 134 |  |

| ΑĮ | peno           | lices    |                                       | 137   |  |

| A  | Syn            | chroniz  | zation logic design                   | 139   |  |

|    |                |          | Iz synchronizer                       | . 139 |  |

|    |                |          | Hz synchronizer                       |       |  |

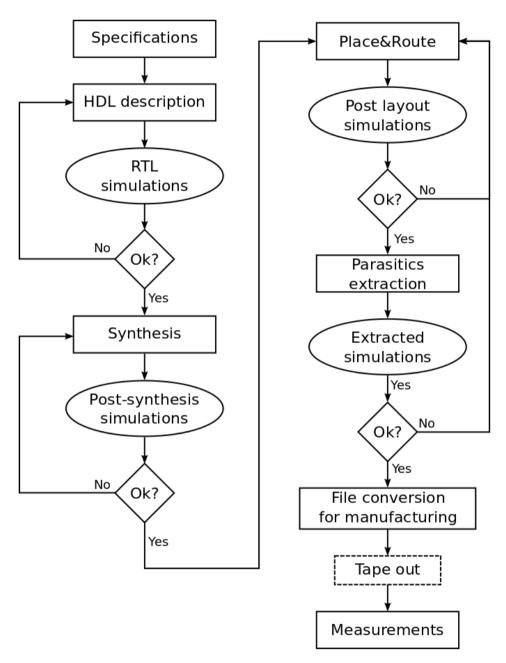

| В  | Digi           | ital des | ign work flow                         | 149   |  |

| D: | ۔<br>ماداما    |          |                                       | 152   |  |

| DΙ | biiog          | raphy    |                                       | 152   |  |

| Su | ımma           | ıry      |                                       | 159   |  |

| Sa | Samenvatting 1 |          |                                       |       |  |

| Ac | knov           | vledgei  | ments                                 | 171   |  |

6 CONTENTS

# Introduction

The beginning of modern science commonly is dated back in the 17th century with Galileo and his scientific method. Unlike the philosophers before him, Galileo trusted only things that could be proven by experiments. Later in the 20th century Karl Popper, a German philosopher, introduced the concept of falsifiability as demarcation between what is scientific and what is not. While no number of measurements can prove the absolute truth of a statement, a single measure can be enough to prove a theory false [1]. The ideal line which connects Galileo to Popper is the idea that the experiment is the crucial part of every scientific theory.

In the 20th century, physicists continued their search toward the infinitely small and, on the opposite side, to the infinitely big. Common to both directions of investigation is the need for sophisticated tools to be able to perform experiments required by the scientific method to prove theories true or false.

The last century radiation detectors have developed from the Geiger tube [2] in 1908 to the large experiments at accelerators as the Large Hadron Collider (LHC). Gas, liquids and solids all became available as detector medium in particle physics, every one of them with their own advantages and disadvantages. A common feature of all the detectors is that they have to be read out to make use of the data collected. In the first particle detectors (e.g., emulsions or bubble chambers) pictures were taken and they had to be analyzed manually to reconstruct the events which were recorded. On the other hand, detectors like the Geiger-Muller tube could automatically provide only a count of how many particles were detected in a specific time interval over a certain area.

Improvements in the readout of the detectors came with the availability of integrated circuits technology which allow an increase in the number of channels while, at the same time, decreasing the single channel area. This, in turn, permits us to reconstruct with increasing precision not only the particle's track but also its energy and momentum.

Modern detectors have to provide an ever increasing precision, that goes from the order of nanosecond in the large high energy physics experiments at 8 INTRODUCTION

CERN to picoseconds for other precision experiments. Moreover, they have to be capable of handling increasing particle rates both on the detection side and on the data readout speed.

This thesis is focused on time measurements in gaseous pixel detectors and it is structured as follows. In chapter 1 a brief history of pixel detectors is presented, focusing mainly on the features of their readout systems. In the second part of the chapter, the focus is on the modern detectors at the Large Hadron Collider and their planned upgrades. Chapter 2 presents the operation principle of gaseous detectors with the basic mechanism behind ion-electron couples production and transport mechanism. GridPix detectors are also introduced describing some basic properties. Chapters 3 and 4 contain the main results of this thesis, illustrating the design and testing of two prototype chips featuring high-resolution Time to Digital Converter (TDC). The results on the TDC are complemented with results on other circuitry which has been designed and tested in view of a full size chip. Finally, chapter 5 presents the analysis of data from a beam test using a telescope that contains three GridPix detectors. Their limitations are studied and are used as a justification for the design of Timepix3, a full size chip which features some circuits developed in the prototypes.

# Chapter 1

# Pixel detectors in particle physics

#### 1.1 Introduction

Silicon detectors are crucial tools used in modern high energy physics (HEP) experiments to detect particles, especially in the proximity of the interaction point. The information collected by these detectors is used to reconstruct the particle's track and primary and secondary vertex positions with high spatial resolution. There are two families of silicon detectors used in HEP: strips and pixels.

Strip detectors have been used for longer time in tracking experiments since they are easier to build and read out due to the lower number of channels. On the other hand, they provide position information in only one dimension, forcing the use of multiple planes of detectors rotated with respect to each other to obtain several coordinates to reconstruct the particle's track. This solution however increases the amount of material of the detector and hence the multiple scattering probability, which in turn degrades the overall resolution. Moreover, multiple particles create ambiguities which make pattern recognition less robust.

Research on detectors that could provide two dimensional information started immediately after the first reports on strip detectors [3]. The first type of pixel detector was a charged coupled device (CCD) [4]. Developments of this technology started in parallel with strip detectors for applications where the expected event rate was lower, since one of the main limitations of CCDs is the very slow readout speed. Pixels became common in high energy physics experiments after developments both in detector connectivity (bump bonding) and integrated circuits (ICs) technology. Pixel detectors are used today in many fields besides

tracking, like medical imaging, fluorescence microscopy or, to stay in high energy physics, calorimetry. These applications, however, are beyond the scope of this work and will not be discussed.

In the following sections a brief history of silicon detectors will be given, highlighting mainly the achieved resolution and the electrical characteristics of the readout electronics. After that, a more detailed description of the state of the art detectors and readout chips will be given to form a reference framework in which this work has been developed.

## 1.2 Tracking silicon detector: overview

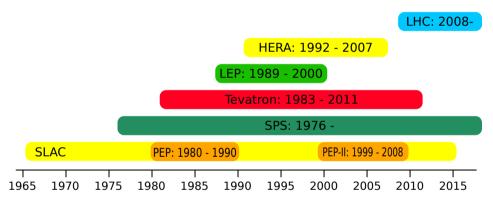

Figure 1.1 shows the most important accelerators used for high energy physics discoveries during the past 50 years. In describing the developments of silicon detectors we will focus on the experiments built to collect data coming from these machines after a brief discussion of the first successful results in using silicon detectors.

**Figure 1.1.** *Timeline of the most important accelerators used in high energy physics in the past decades.*

The first working silicon strip detector was used at CERN at the NA11 experiment [5] installed in the SPS accelerator in the early 80's. The NA11 experiment was aimed at studying short lived particles and in particular charmed hadrons [6]. The first prototype consisted of 100 strips 140  $\mu$ m wide, 30 mm long with a pitch of 200  $\mu$ m and a total sensitive area of 20 mm  $\times$  30 mm. The final detector consisted of 1200 strips with a pitch of 20  $\mu$ m; it had 4.5  $\mu$ m single hit resolution and an analog readout made of hybrid preamplifiers and Analog to Digital Converters (ADCs). This first detector proved its usefulness in vertex reconstruction but also gave clear indications that improvements both in the manufacturing

| Experiment                | Chip name     | Type  | Year | Technology |

|---------------------------|---------------|-------|------|------------|

| Mark II (SLC)             | Microplex     | Strip | 1988 | 5.0 µm     |

| DELPHI (LEP)              | MX3           | Strip | 1991 | 3.0 µm     |

| DELPHI (LEP2)             | SP8           | Pixel | 1997 | 3.0 µm     |

| ALEPH (LEP)               | CAMEX64       | Strip | 1991 | 3.5 µm     |

| OPAL (LEP2)               | MX7 Microplex | Strip | 1997 | 1.2 µm     |

| BaBar                     | Atom          | Strip | 1995 | 0.8 µm     |

| CDF (Tevatron) / L3 (LEP) | SVX           | Strip | 1992 | 3.0 µm     |

| D0 (Tevatron)             | SVX II        | Strip | 2001 | 1.2 µm     |

| HERMES/HERA-B (HERA)      | HELIX 2.2     | Strip | 2001 | 0.8 µm     |

| H1 (HERA)                 | APC128        | Strip | 2001 | 0.8 µm     |

| ZEUS (HERA)               | HELIX 3.0     | Strip | 2001 | 0.8 µm     |

**Table 1.1.** Overview of the developments in readout chips for silicon detectors for the main high energy physics experiments.

of the detectors and in the readout electronics were required for future experiments.

As mentioned, the readout of the detectors used in the NA11 experiment was still difficult and discrete components were used: to allow the miniaturization of the detector and to increase the number of channels available Application Specific Integrated Circuits (ASICs) were necessary to provide small area, high speed readout systems. In 1985 successful tests of silicon strip detectors with ASIC readout were carried out [7].

Also charge coupled devices (CCDs) started being used soon after their invention [8] in fixed target experiments [9] and in collider experiments such as SLD at the SLAC linear collider. The VXD2 detector was assembled using commercial CCDs of area  $1\,\text{cm}^2$  and pixel size  $22\,\mu\text{m}\times22\,\mu\text{m}$ . The pixel readout rate was  $2\,\text{MHz}$  with a shaping time of 300 ns and a noise level of less than 300 electrons. In this case the signals from the pixel were still processed by external electronics.

Miniaturization and high readout speed were not the only difficulties to overcome. The detectors are generally placed close to the interaction point thus collecting a lot of radiation that can damage them, degrading the performance or in extreme cases causing the complete failure of the device. Radiation hardness then became another key aspect to take into account during the development of silicon detectors. Table 1.1 gives an overview of the various readout ASICs discussed in this section and shows the continuous trend of improvements in the available technology and the performances of the ASICs produced.

Following the first successful results, silicon detectors for tracking started to become widely used. Mark II at the Stanford Linear Accelerator Center (SLAC)

used silicon microstrips [10] readout by a custom designed ASIC, Microplex [11]. The chip contained 128 charge sensitive amplifiers with multiplexed analog output. It was produced in 5  $\mu$ m nMOS technology and the final ASIC had an active area of 4.4 mm  $\times$  6.4 mm and it could withstand more than 1 Mrad before failure.

Experiments at the Large Electron Positron (LEP) collider also installed silicon tracking detectors. At DELPHI, the tracking detector consisted of three layers of silicon microstrips with a pitch of  $25\,\mu m$  [12]; the 73728 total channels were readout serially by the MX3 chips produced in  $3\,\mu m$  CMOS technology. The chip consisted of 128 charge sensitive amplifiers, with every channel dissipating  $0.5\,mW$ . The serial readout guaranteed a rate of  $2.5\,MHz$  and the signal to noise ratio was 15:1. The radiation dose causing chip failure was in the range from  $5\,krad$  to  $85\,krad$ .

For the upgrade of LEP, DELPHI replaced the microstrips with two layers of pixel detectors plus two layers of microstrips [13]. The pixel detector had in total 1.2 million channels. Each pixel was  $330\,\mu\text{m} \times 330\,\mu\text{m}$  except for pixels at the edges which were bigger to minimize the inactive area. They were read out by the SP8 chip; in every pixel there was a preamplifier, a shaper, a discriminator and a 1 bit memory. A notable feature was the implementation of a zero suppression readout scheme, that allowed to read out only the pixels with a hit.

The ALEPH vertex detector [14] was also a microstrip detector with active area  $49\,\text{mm}\times49\,\text{mm}$  and strip pitch of  $25\,\mu\text{m}$  or  $50\,\mu\text{m}$  for P or N type strips. The CAMEX64 readout chip was built in  $3.5\,\mu\text{m}$  technology, it had 64 channels which individually dissipate roughly  $1\,\text{mW}$  of power and had a baseline noise of 335 electrons. The chip could sustain  $25\,\text{krad}$  of radiation before it stopped functioning. Both the detectors and readout chips were updated for phase two of operations (LEP2), with improvements mainly in radiation hardness and noise performance.

L3 installed a silicon microstrip detector in 1993 as an upgrade of the existing tracker which did not use any silicon system [15]. To have the detector ready in time for the installation they decided to use the same readout chip as CDF (described later in this section).

OPAL, the fourth experiment at LEP, installed a silicon microstrip tracker during the first upgrade [16]. The 65502 channels were read out by the MX7 chip and its radiation hard (MX7-RH) version which was used in proximity of the interaction point and built in 1.2 µm technology. The noise was kept below 350 electrons and the power consumption was 2 mW per channel. The signal to noise performances could be kept within 80% up to 700 Gy of absorbed dose. Each channel contained a Charge Sensitive Amplifier (CSA) and a bandwidth filter with the output connected by switches to two storage capacitors.

At SLAC (California, USA) also the BaBar experiment used silicon strips as

vertex detectors. The 128 strips were read out by the Atom chip built in  $0.8\,\mu m$  technology. The peaking time of the chip was selectable among  $100\,ns$ ,  $200\,ns$  and  $400\,ns$  giving a different ENC from 380 to 220 electrons respectively with an average power consumption of  $4.5\,mW$  per channel.

The next generation of collider experiments to use silicon vertex detectors were CDF and D0 at Tevatron at Fermilab (Illinois, USA). The CDF silicon strip tracker [17] was readout by the SVX IC chip which was built using 3 µm CMOS technology [18]. The 128 channels in a single chip consumed 150 mW while the signal to noise ratio was between 10 and 15. The readout speed was either 1 MHz, when reading out the analog information, or 10 MHz when only the digital part was transmitted off chip. The chip had an example of a sparse-readout system: one could choose to readout only strips where a hit was detected instead of reading out all the channels. Tests on radiation hardness proved that the noise would double after an exposure to 20 krad of radiation making the chip not usable beyond the end of the scheduled RunI.

For the upgrade of the detectors for RunII of Tevatron, also D0 installed a microstrip tracker [19]. The SVXII chip was the upgrade of the SVX made in 1.2 µm radiation hard technology and had 128 channels. It featured sparse readout, a signal-to-noise ratio of 20 and power consumption approximately of 3 mW per channel [20].

Around the same time ZEUS, HERMES and HERA-B at the Hadron-Electron Ring Accelerator (HERA) at DESY (Hamburg, Germany) installed a strip vertex detector for the first upgrade in 2000 [21], [22]. The strips had a 20  $\mu$ m pitch but only one in six was AC coupled to a readout line. The signals were readout by the Helix3.0 ASIC built in 0.8  $\mu$ m CMOS technology. Each chip contained 128 channels, each one equipped with a charge amplifier and shaper with a measured ENC of 340 + 40C electrons, where C is the input capacitance in pF. The signals were then sampled in an analog pipeline with a maximum latency of 128 samples. The readout was performed through a serial bus and multiple chips could be daisy chained together. A chip dissipated 2 mW per channel and could sustain up to 100 krad radiation dose before deteriorating operations [23].

The other general purpose detector at HERA was H1. H1 had a backward silicon tracker which was upgraded during the 2000 shutdown with a forward and a central silicon tracker. The first version of the readout chip was called APC128 [24] and it was produced in a 2  $\mu$ m technology. Each one of the 128 channels consisted of a CSA followed by an analog event pipeline with a total power consumption of 300  $\mu$ W. The noise measurements showed values as 675 electrons + 28 electrons pF<sup>-1</sup>. For radiation doses over 100 krad a change in the behavior of the chip was detected, making it unreliable for further operation. For the central tracker a radiation hard version of the chip was produced [25]. The main difference between this new version and the previous one is the 2  $\mu$ m

DMILL radiation hard technology which consequently lead to the redesign of the analog frontend, in particular the amplifier, to respect the new design rules.

#### 1.3 Modern silicon detectors at the LHC

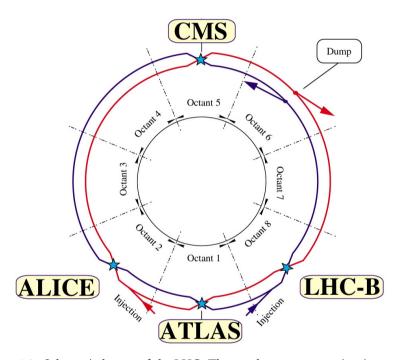

The Large Hadron Collider [26] (LHC, see figure 1.2) is a proton accelerator installed at CERN in the 27 km tunnel which previously hosted the LEP accelerator.

**Figure 1.2.** Schematic layout of the LHC. The two beams are running in opposite directions.

One ring of superconducting magnets and RF cavities stabilizes and accelerates two bunches of protons which travel in opposite direction. At four interaction points the two beams collide every 25 ns with a nominal center of mass energy of 14 TeV. At the four collision points experiments have been built: two high luminosity, general purpose experiments (ATLAS and CMS), a B-physics experiment (LHCb) and one dedicated heavy ions experiment (ALICE)<sup>1</sup>. The

<sup>&</sup>lt;sup>1</sup>LHC is designed to run not only with protons but also with lead ions.

| Experiment    | Chip name | Tech. | Pixel size       | Dimension        | Power    |

|---------------|-----------|-------|------------------|------------------|----------|

| _             | _         | (µm)  | (µm)             | (mm)             | (μW/ch.) |

| ATLAS         | FE-I3     | 0.25  | $400 \times 50$  | $7 \times 11$    | 40       |

| ATLAS (up.)   | FE-I4     | 0.13  | $250 \times 50$  | $20 \times 19$   | 6.6      |

| CMS           | PSI46V2   | 0.25  | $100 \times 150$ | $7.9 \times 9.8$ | 29       |

| LHCb          | Beetle    | 0.25  | NA               | $6.1 \times 5.5$ | 5        |

| LHCb (up.)    | VeloPix   | 0.13  | $55 \times 55$   | 14 	imes 14      | 46       |

| Medipix coll. | Medipix3  | 0.13  | $55 \times 55$   | 14 	imes 14      | 15       |

| Medipix coll. | Timepix   | 0.13  | $55 \times 55$   | 14 	imes 14      | 14       |

**Table 1.2.** Overview of the latest developments in pixel readout chips.

target luminosities are  $10^{34}\,\mathrm{cm^{-2}s^{-1}}$  for ATLAS and CMS,  $2\times10^{32}\,\mathrm{cm^{-2}s^{-1}}$  for LHCb and  $10^{27}\,\mathrm{cm^{-2}s^{-1}}$  for ALICE during the ion runs.

The overview of tracking detectors given in section 1.2 pointed out clearly the trend in miniaturization, lower power, low noise and increased radiation hardness for detectors used in high energy physics applications. A list of the most important requirements for modern tracking detectors includes:

- low noise frontend;

- low power consumption per channel;

- high granularity;

- radiation hardness of both the sensor and the readout electronics;

- high readout speed;

- low cost.

It is clear that the four detectors at the LHC, given the harsh environment where they have to operate, stretch the use of available technology to the limit in terms of required radiation hardness, readout and processing speed, detector granularity, cooling and overall performance. In the following sections an overview of ATLAS, CMS and LHCb will be given, focusing in particular on the pixel silicon detectors and their readout electronics. Common feature to all the readout chips currently used in the three experiments are the 0.25 µm technology used and special layout rules used to ensure higher radiation hardness with respect to the standard design rules [27]. Table 1.2 summarizes the characteristics of the chips that will be presented in the new sections about LHC and multi purpose readout chips that will be introduced subsequently.

# 1.4 The Atlas pixel detector

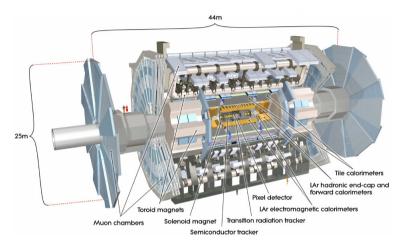

ATLAS (A Toroidal LHC ApparatuS) is a general purpose detector [28] installed at the LHC at CERN. Figure 1.3 shows a cut-away view of the ATLAS detector. The detector is approximately 25 m high and 44 m long with a weight of roughly 7000 t.

**Figure 1.3.** *Cut-away view of the ATLAS detector.*

In this thesis, we will focus on the characteristics of the pixel tracker which provides the required momentum and vertex resolution together with the microstrip and the straw tube detectors. The pixel detector has approximately 80.4 million readout channels and it has to withstand a 1 MeV neutron equivalent fluence ( $F_{neq}$ ) between  $46 \times 10^{12} \, \mathrm{cm}^{-2}$  and  $270 \times 10^{12} \, \mathrm{cm}^{-2}$  for a maximum dose of  $15.8 \, \mathrm{Mrad}^2$ . Over the ten-year design lifetime of the experiment, the pixel inner vertexing layer must be replaced after approximately three years of operation at design luminosity.

The FE-I3 (FrontEnd Iteration 3) pixel chip [29] is the currently used readout chip for the pixel sensors. It contains 2880 pixel cells with dimensions  $400\,\mu m \times 50\,\mu m$  arranged in a  $18 \times 160$  matrix with the final size of the chip being  $0.7\,cm \times 1.1\,cm$ . Power consumption per channel is kept within  $40\,\mu W$  while the noise is lower than 200 electrons.

Each pixel cell contains a CSA where the signal from the sensor is integrated, and a digital part where the signal from the analog block is compared to a

$<sup>^2</sup>$ Assuming an inelastic cross section of 80 mb, a luminosity of  $10^{34}\,\mathrm{cm}^{-2}\,\mathrm{s}^{-1}$  and a data taking period of  $10^7\,\mathrm{s}$ . Simulation results.

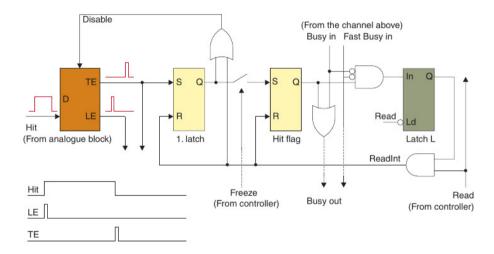

programmable threshold in the discriminator. Figure 1.4 shows the digital part of the pixel. The "D" block generates two short (ns) pulses at the rising and falling edge of the signal which are used to calculate and store the Time over Threshold (ToT) information as the combination of two different time stamps. The complete hit information is then available after the falling edge. The readout part transfers the hit pixel address, the time stamp and the ToT information to the periphery of the chip; unless a trigger signal arrives from the Level-1 trigger in less than 3.2 µs the hit is deleted. Otherwise, the triggered events are serially readout from the chip in order of trigger arrival.

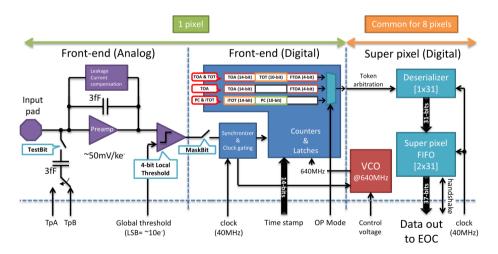

Figure 1.4. The digital part of the FE-I3 pixel with the timing diagram. The "D" block generates the two short pulses used to determine the ToT information from the two respective time stamps. ToT, ToA and the pixel number are then transferred to the periphery of the chip. If a trigger arrives the hit is readout, otherwise it is deleted.

### 1.4.1 Atlas upgrade

After the first three successful years of operations, LHC shut down to prepare the machine for the 14 TeV operation. During the shutdown the ATLAS detector has been extended with a pixel layer close to the beam pipe which uses a new readout chip.

The FE-I4 ASIC [30], successor of FE-I3, is designed in 130 nm CMOS technology. It contains 26880 hybrid pixels arranged in a matrix of 80 columns with 250 µm pitch and 336 rows with 50 µm pitch. The dimensions of the chip are

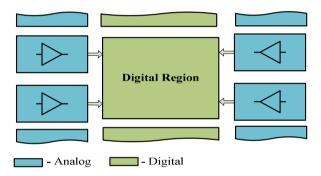

$2\,\mathrm{cm} \times 1.9\,\mathrm{cm}$ . The FE-I4 architecture is fundamentally different from FE-I3. In particular, it has been decided that the hit recorded in the pixel should not be moved to the periphery of the chip and then wait the decision to keep it or not based on the level 1 trigger decision. Instead the hit is stored locally until the same level 1 trigger decides if it is to be kept or not. The pixels are organized in double columns and divided in  $2\times 2$  groups, as shown in figure 1.5. Each pixel is equipped with its own analog frontend but the digital logic is shared among the four pixels in the group and it is called Pixel Digital Region (PDR). It has been shown [31] that this solution minimizes the physical resources needed to store and process the hit information. Moreover, the calculated inefficiency is below 0.1% for the innermost pixel layer at 3 times the full LHC luminosity and assuming a latency of 120 bunch crossing.

**Figure 1.5.** Double column layout: a group of  $2 \times 2$  pixels, each one with its own analog frontend, shares the digital logic to minimize the physical resources needed to store and process the hit information.

The global time stamping is common to the PDR while the ToT is locally produced in the single pixel with a counting technique with a four bits resolution. The storage of the ToT values is done in the PDR which can contain up to five events. Since the four pixels are readout only if a trigger arrives the activity on the common double column bus is lower with respect to FE-I3.

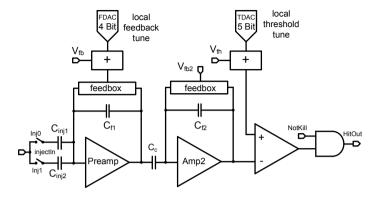

The analog frontend [32] has been designed as a two stages architecture (see figure 1.6). The first stage is a CSA whose purpose is charge collection. The second stage is a voltage amplifying stage with no shaping of the signal. Once the charge is collected the amplification takes place in this stage which is decoupled via the input capacitor  $C_c$  isolating in practice the second stage from any DC shift that may occur due to radiation effects. The ENC is kept below 300 electrons.

An 8bit/10bit encoding has been chosen to send the data off chip. However,

**Figure 1.6.** FE-I4 frontend block diagram. The double stage architecture allows to decouple the charge collection and shaping stage from the amplification one. The capacitor  $C_c$  decouples the first part from the second, isolating the last stage from DC shifts due to radiation effects.

in order to cope with the required data rate expected a faster clock than the  $40\,\mathrm{MHz}$  has to be used for the readout. This clock is produced on chip using a Phase Locked Loop (PLL) and allows a readout speed of  $160\,\mathrm{Mbit\,s^{-1}}$ .

## 1.5 The CMS pixel detector

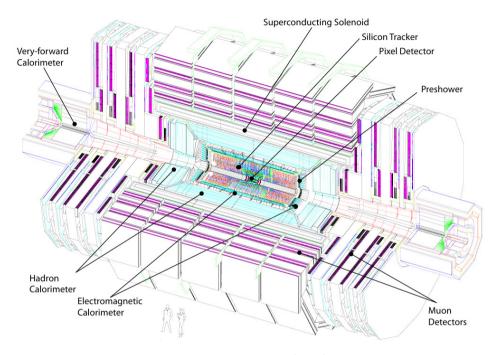

The Compact Muon Solenoid (CMS) detector [33] is the other general purpose experiment at LHC. The detector (see figure 1.7) is 21.6 m long and has a diameter of 14.6 m. It has a total weight of 12500 t. The main feature driving the design of the full detector is the superconducting solenoid that provides the 4T magnetic field for the muon momentum measurements.

The tracking volume is a cylinder  $5.8\,\mathrm{m}$  long with a diameter of  $2.6\,\mathrm{m}$ . It is composed of ten layers of silicon microstrips to provide the required granularity and precision in tracking and of three layers of silicon pixels which are placed close to the interaction region which improve the reconstruction of secondary vertices. The total detector surface of the silicon tracker is about  $200\,\mathrm{m}^2$ . The pixel detector covers the interaction point at radii between  $4.4\,\mathrm{cm}$  and  $10.2\,\mathrm{cm}$  and it consists of 1440 pixel modules. The operating conditions foresee a hit rate density of  $1\,\mathrm{MHz\,mm^{-2}}$  at a radius of  $4\,\mathrm{cm}$ . Since the size of a pixel is  $100\,\mathrm{\mu m} \times 150\,\mathrm{\mu m}$  the occupancy is around 1%.

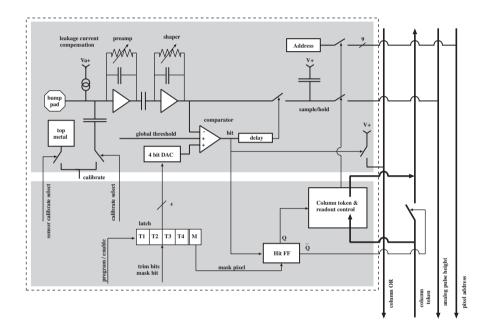

The sensors are readout by the custom chip PSI46V2 [34] which contains a

Figure 1.7. Compact Muon Solenoid overview.

matrix of  $52 \times 80$  pixels with the total size of the chip being  $7.9\,\mathrm{mm} \times 9.8\,\mathrm{mm}$ . The three main blocks of the chip are the single pixel units which are organized in double columns, the end of column (EOC) periphery which controls the readout and trigger of a single double column and the periphery of the chip where the supply and controls are located. A single readout chip consumes  $120\,\mathrm{mW}$  ( $29\,\mu\mathrm{W}$  per channel).

Figure 1.8 shows the single pixel block diagram; the signal from the sensor is amplified and shaped by a two-stages CSA plus a shaper. The signal from the frontend is followed by a comparator which has a 4 bits programmable threshold. This threshold is used to mitigate the transistors mismatch inherent to each production process. Once the signal goes above threshold the output of the shaper is recorded in a sample and hold circuit. The periphery of the double column is notified of the hit immediately through a double column common OR and the pixel is inactive until the signal is readout. Thus, the dead time of the single pixel is short but it depends on the occupancy. An event activating multiple pixels in the same double column will result in those same pixels being inactive for a long time.

The readout of the pixel occurs when a token from the double column pe-

riphery arrives. It is important to remark that the CMS pixel chip stores and sends the analog information (pulse height) to the chip periphery which is then digitized, unlike the ATLAS pixel chip in which the digitization is done at the pixel level. The analog information is sent out together with the pixel address and stored in buffers in the EOC where the data are then compared to the higher level trigger which is externally produced and subsequently kept to be sent out of the chip or discarded.

**Figure 1.8.** *Single pixel block diagram of the CMS pixel chip.*

#### 1.6 The LHCb Vertex Locator

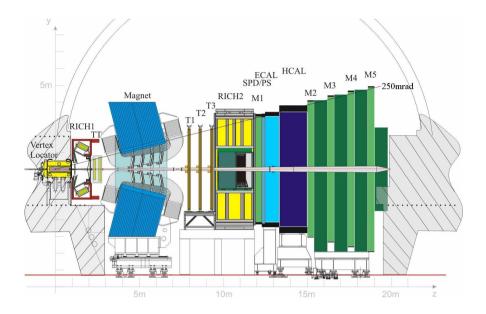

LHCb [35] is an experiment dedicated to the study of heavy flavor physics and in particular to the decay of beauty and charmed particles to detect any violation of the CP symmetry. Figure 1.9 shows an overview of the detector.

The tracking system of LHCb is divided in two parts: the Vertex Locator (VELO) and the Silicon Tracker (ST). In the following section only the VELO will be described with its upgrade, since it is connected with the chips developed in this work.

Figure 1.9. LHCb detector overview.

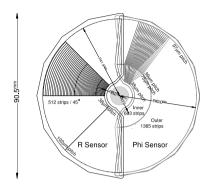

Given a certain number of constraints (geometrical, environmental, integration with the surrounding detector systems), the LHCb VELO detector is quite different in concept with respect to the ATLAS and CMS trackers. To cope with the high rate of LHC and to produce a fast high level trigger, simulations prove that the best choice for the coordinate system are the polar coordinates  $R\phi$  instead of the usual xy scheme. This feature led to the design of two different sensors, one called  $\phi$ -sensor and the other one R-sensor, the former providing information on the azimuthal angle the latter on the distance from the beam. A sketch of the two different sensors can be seen in figure 1.10 where for clarity only a portion of the strips is depicted.

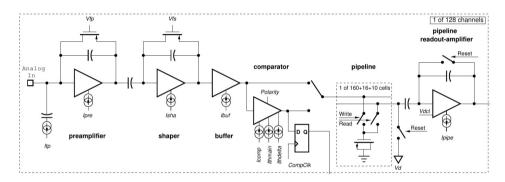

The VELO is readout with a custom ASIC called Beetle. It has a die size of  $61 \times 5.5\,\mathrm{mm^2}$  and 128 readout channels each equipped with a CSA and CR-RC shaper as shown in picture 1.11. A comparator per channel provides a binary signal. The output of the shaper or of the comparator is then sampled into an analog pipeline at  $40\,\mathrm{MHz}$ . The measured noise of the frontend is equal to  $500\pm48.3$  electrons/pF. The minimum rise time is less than 25 ns with the remainder adjustable to be less than 30%. The chip has a typical power consumption of  $5\,\mathrm{mW}$  per channel.

Figure 1.10. LHCb VELO sensor sketch.

Figure 1.11. LHCb VELO frontend.

# 1.6.1 VELO upgrade: VeloPix

For the upgrade LHCb decided to replace the current strip detector with a pixel detector called VeloPix [36]. VeloPix is derived from the latest iterations of the Medipix/Timepix series of chips (see section 1.7) and it shares with them some characteristics like the 130 nm technology and the  $256 \times 256$  pixel matrix with a pixel size of  $55\,\mu\text{m} \times 55\,\mu\text{m}$ . Moreover VeloPix uses many circuits already developed for Timepix3 (see section 5 for more details): a fast frontend (rising time <  $25\,\text{ns}$ ), zero suppression and data driven readout. Since VeloPix will be placed in proximity of the interaction point at a distance of about 7 mm both the radiation hardness of the chip and the readout speed are of great importance. The chip has to be able to survive doses up to 400 MRad in a foreseen lifetime of 10 years and it has to be capable of handling a hit rate of 500 MHits/s which requires an output bandwidth larger than 12.2 GBit/s. The chip will consume

less than 3 W.

One notable characteristic of VeloPix derives directly from the need to process such a big amount of hits. To reduce the amount of bits to send to the periphery an approach similar to the one used for FE-I4 has been adopted.  $2\times 4$  pixels are grouped in a structure called Super Pixel. This allows to reduce by 25% the required bandwidth since duplicate information such as the timestamp will be sent only once. The consequence is that the layout of the Super Pixel requires a different positioning of the analog frontends on the sides while the central part is used for the common digital blocks. VeloPix is in the design phase and the first production run is foreseen in summer 2015.

# 1.7 The Medipix family

In the previous sections the focus has been on detectors and readout chips used in collider experiments. However it is clear that the applications of silicon detectors are not limited to this field. In the early nineties a collaboration was formed with the aim of developing a photon counting chip for imaging purposes which was built in 1997 called Medipix1 [37]. The chip contains a matrix of  $64\times64$  pixels of size  $170\,\mu\text{m}\times170\,\mu\text{m}$  covering a total active area of  $1.2\,\text{cm}^2$  and was developed using a  $1\,\mu\text{m}$  technology. Each pixel contains a CSA and a shaper. The signal collected and amplified by the analog frontend is then compared with an externally set threshold in the discriminator: if the signal exceeds the threshold one event is counted up to 32767 events (15 bits counter). The maximum count rate is  $2\,\text{MHz}$  with a maximum readout speed of  $384\,\text{ms}$  at  $10\,\text{MHz}$ .

Following the success of Medipix1 and with the purpose of taking advantage of the submicron technology that were becoming available to increase the number of pixels per chip and include more functionality, the Medipix2 chip was developed [38] in 2002 in 0.25  $\mu m$  technology. The matrix was enlarged to  $256 \times 256$  pixels of size  $55 \, \mu m \times 55 \, \mu m$  with an active area of  $2 \, cm^2$ . The chip consumes less than 1 W. While the structure of the frontend remained the same with the usual amplifier-shaper-discriminator chain, the input was upgraded to accept both positive and negative charge to allow the use of different materials as sensors. Moreover, with Medipix2 the concept of an energy window was introduced: it is possible to select two thresholds (upper and lower) to accept only photons inside that energy window. Each pixel can accept a rate of 100 kHz in an adjustable time window. Readout is performed after exposure of the chip to minimize the dead time and can be done serially or in parallel. In view of large area applications the chip was designed to be 3-side buttable.

Medipix3 [39] is the last arrival in the Medipix family. While the physical dimensions are the same as Medipix2, it uses a 130 nm technology which allows

to put more transistors and hence more logic in the single pixel cell while retaining the same low power consumption. The upgrades consist in particular in the operation modes of the chip; to mitigate the effects of charge sharing a charge summing mode has been implemented. When a cluster of neighboring pixels is hit, all the charge is allocated to the cell with the highest charge deposit. Moreover, it is possible to configure the chip in spectroscopic mode. In this case, 4 pixels are connected allowing the use of 8 different thresholds at the cost of losing some spatial resolution.

# 1.8 The Timepix chip

The surprising application of the Medipix2 chip as readout for Micro Pattern Gaseous Detectors (MPGD) such as Micromegas or Gas Electron Multipliers (GEM) sparked the desire to design a chip that could provide information on the ToA of the electrons from the ionization trail as well as information on the charge collected. This led to the design of the Timepix (Timepix1) chip [40].

Timepix is a general purpose chip which allows to record the ToA, the ToT or count the number of events on a per pixel basis. The chip has an active area of  $1.4\,\text{cm}\times1.4\,\text{cm}$ . The pixel pitch is  $55\,\mu\text{m}$  and the power consumption is  $14\,\mu\text{W}$  per channel. The periphery is located on one side, making Timepix three side buttable.

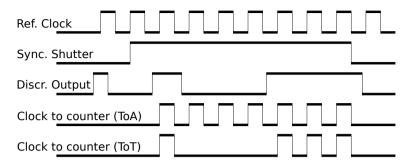

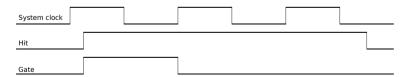

Figure 1.12 shows the time diagram for the different modes of operation of Timepix. In any operation mode the shutter must be open to record the incoming hits; this signal is set externally by the user. In Time of Arrival (ToA) mode the first hit to arrive with the shutter open starts the recording of the system clock by counting. The counting stops when the shutter is closed. A second hit detected in this time window in the same pixel does not have any influence. In Time over Threshold (ToT) mode, instead, the time spent over threshold by all of the detected hits when the shutter is open is recorded, giving information on the total amount of charge detected. The different modes can be selected on a per pixel basis.

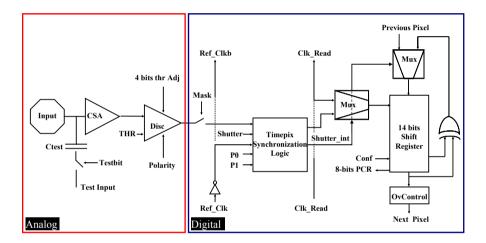

Figure 1.13 shows a block diagram of the Timepix pixel. The analog frontend is made of a single stage CSA and a discriminator. Given the application in MPGDs particular care has been taken in the design of the preamplifier to combine low noise and high gain. To reduce the input capacitance (and hence reduce the noise) a cascode has been added in the amplifier; the biasing is controlled with a global 8-bits DAC. The high gain limits the linear output range but makes the rise time faster which is important to reduce timewalk (see section 3.1).

The digital part of the pixel includes the Timepix Synchronization Logic (TSL), a 14-bits shift register and the 8-bits of pixel configuration. The TSL syn-

Figure 1.12. Timepix time diagram.

Figure 1.13. Timepix pixel block diagram.

chronizes the externally produced shutter with the system clock so that every pixel receive a glitch-free internal shutter. It is composed of two state machines designed with an asynchronous network which uses SR flip-flops. Besides not propagating glitches to the counter, it takes care that the digital logic works only when there is a hit, to minimize power consumption.

An important feature of the chip to highlight is that the system clock, which determines the resolution, can be set externally up to 100 MHz. This is crucial when it comes to Timepix as readout for MPGD and in particular for GridPix detectors (see section 2.1 for more details) since the resolution in the direction perpendicular to the chip plane is determined by the time resolution available: in Timepix this is then limited to 10 ns which is not enough to use GridPix as tracking detector.

1.9. CONCLUSION 27

Given the limitations of Timepix as readout chip for GridPix detectors the design of a new chip called Timepix3 started in 2010. The chip has been taped out in 2013 and is described in more details in section 5.2 together with the first measurement results.

#### 1.9 Conclusion

In this chapter an overview of the most important strip and pixel detectors used in high energy physics experiments has been presented. The focus on the readout chips has highlighted how since the beginning the design and performance of the chips rapidly evolved with the newer technologies available. There is a clear trend towards readout chips that are radiation hard and consume the least possible amount of power. In addition, more functionality is being implemented in the single readout cell thanks to the available submicron technologies.

# Chapter 2

# Gaseous pixels and high resolution time measurements

The review presented in Chapter 1 focused mainly on readout chips developed for silicon detectors. Gaseous detectors like Time Projection Chambers existed but they were usually readout with planes of wires. However in the past decade a new trend in gas detectors emerged with concepts like Micromegas detectors or Gas Electron Multipliers requiring studies on gas properties and detector characteristics and the development of new, dedicated readout chips. The main feature of a Micro Pattern Gas Detector (MPGD) is the 3D reconstruction of a particle's track which can be obtained by measuring the trail of the electrons in the detection gas volume. To reconstruct this trail one measures the time it takes the individual electrons to travel to the anode.

In the following sections the operational principles of a particular type of MPGD called GridPix will be presented, followed by the basic concepts of ionization and electron transport in gases. Finally, a review of the most common time measurement techniques will be presented.

### 2.1 GridPix detectors

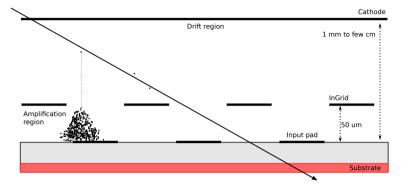

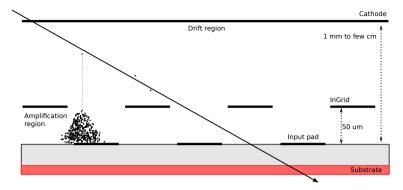

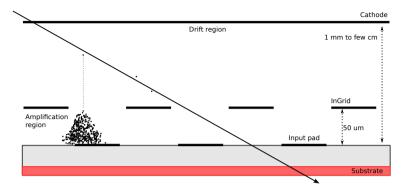

At Nikhef a novel concept was developed some 10 years ago, GridPix. A GridPix detector is a miniaturized Time Projection Chamber (TPC) that uses a pixel chip as readout plane. The detector is built combining a Timepix chip with an Integrated Grid (InGrid) on top of it. A schematic diagram of this kind of detector can be seen in figure 2.1. The first proof of concept of the readout of a micro-TPC using a pixel chip as readout plane was given in 2004 [41], [42] using a Medipix2

chip [38] with a Gas Electron Multiplier (GEM) foil on top [43]. Medipix2 is a photon counting chip and cannot measure the drift time of the electrons created by an incoming charged particle in the drift volume. On this premise, Timepix chip was developed at CERN [40], based on the existing Medipix2.

Figure 2.1. Schematic representation of the working principle of a GridPix detector. A charged particle passes through the drift region and it ionizes the gas molecules. The generated electrons drift towards the grid. In the region between the grid and the chip an avalanche process takes place due to the strong electric field applied. The electrons of the avalanche are then collected at the input pad.

On top of Timepix, an aluminum grid is built using MEMS<sup>1</sup> technology at a height of  $50\,\mu\text{m}$ , defining the amplification region. The grid contains holes which are aligned with the pixel pads underneath. On a larger distance from the chip a cathode is placed, which defines the drift volume and is chosen accordingly to the application. The amplification and drift volumes are filled with a gas mixture and an electric field is applied between the cathode and the chip and between the grid and the chip, which is always at ground potential. When a charged particle passes through the drift region it ionizes a few gas molecules. The liberated electrons drift by means of the applied electric field toward the grid. Once an electron traverses one of the holes in the grid an avalanche process takes place due to the strong electric field ( $70\,\text{to}\ 100\,\text{kV}\ \text{cm}^{-1}$ , depending on the gas mixture) in the amplification region, with typical gain values around  $10^4$ . The electrons of the avalanche are then collected at the input pad and the resulting signal is processed by the frontend electronics.

Compared to conventional TPCs, that use a plane (or multiple planes) of wires for the readout, the main advantage of using a pixel detector is the in-

<sup>&</sup>lt;sup>1</sup>Micro Electro Mechanical Systems

creased spatial resolution that can be achieved. In fact the granularity is such that most pixels record avalanches that originate from a single electron. Compared to regular silicon pixel sensors, the use of gas as detector medium on top of the chip may result in less material and hence a lower multiple scattering probability. Moreover, the input capacitance due to the detector itself is reduced, thereby reducing the input noise. It is worth noticing that a pixel chip can be used also for the readout of large TPCs if one could build such large area GridPix detectors.

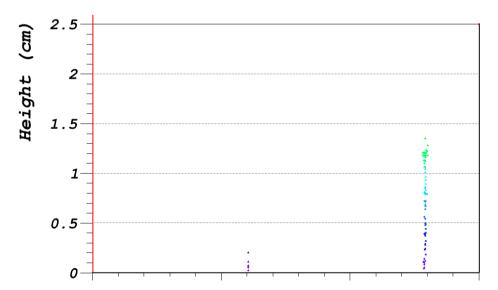

Figure 2.2 shows an example of an event recorded with a prototype GridPix detector [44] having a drift distance of 3 cm. The detector was inside a magnetic field of 0.2 T with the field lines running parallel to the drift direction. The electrons from ionization of single atoms in the He/isobutane gas mixture used are traceable; different colors represent the different Time of Arrival (ToA) recorded by the Timepix and translated to height in the drift volume.

**Figure 2.2.** Event recorded with a GridPix detector. The height of the drift volume is 3 cm and a magnetic field was applied. The different colors along the track represent measured arrival times.

Even though a long R&D phase has shown the virtues of GridPix detectors, the viability still needs to be proven to make it reliable and suitable for operations as tracking detector in full scale experiments [45].

## 2.2 Gas properties

When a charged particle passes through the gas in the drift volume of a GridPix detector the relevant processes that take place from the moment the particle arrives to the detection of the signal at the input pad of the pixel chip are:

- the ionization of gas molecules;

- the drift of the generated electrons to the grid;

- the amplification of the signal in the region between the grid and the pixel pad;

- charge induction.

In the next paragraphs, some details on every step of the process will be given.

#### 2.2.1 Ionization in the gas

A charged particle passing through the gaseous drift volume of a GridPix detector loses energy and ionizes some gas molecules [46]. Given a gas atom *X* and a charged particle *p* the interaction can be described as:

$$X + p \rightarrow X^+ + p + e^-$$

where  $X^+$  is the positive ion and  $e^-$  is the primary electron. This process can only happen if the energy of the incoming particle is bigger than the ionization energy  $E_i$  of the gas molecules. Notice that if the primary electron energy after the first ionization is big enough, it might start a trail:

$$X + e^{-} \rightarrow X^{+} + e^{-} + e^{-}$$

and in this case the secondary is called  $\delta$ -electron.

Defining  $n_p$  as the average number of primary ion pairs per cm and  $n_T$  the average number of ion pairs including the one created by the  $\delta$ -electrons one can write

$$\langle n_T \rangle = \frac{L \cdot \langle \frac{dE}{dx} \rangle_{\text{ioniz}}}{W_i}$$

(2.1)

where  $\langle \frac{dE}{dx} \rangle_{\text{ioniz}}$  is the mean energy loss of the incident particle, L is the path length of the gas layer the particle has to cross and  $W_i$  is the average energy of

| Gas             | I (eV) | $W_i$ (eV) | $\frac{dE}{dx}$ (MeV g <sup>-1</sup> cm <sup>2</sup> ) | $n_p \; (\text{cm}^{-1})$ | $n_T \text{ (cm}^{-1})$ |

|-----------------|--------|------------|--------------------------------------------------------|---------------------------|-------------------------|

| $H_2$           | 15.4   | 37         | 4.03                                                   | 5.2                       | 9.2                     |

| Ar              | 15.8   | 26         | 1.47                                                   | 29.4                      | 94                      |

| Xe              | 12.1   | 22         | 1.23                                                   | 44                        | 307                     |

| CO <sub>2</sub> | 13.7   | 33         | 1.62                                                   | 34                        | 91                      |

**Table 2.1.** *Gas properties*

the ion pair. Table 2.1 gives the values of some relevant quantities for different gases.

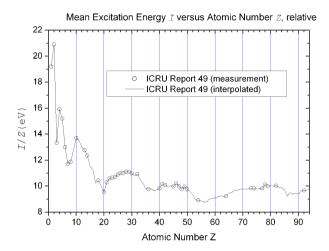

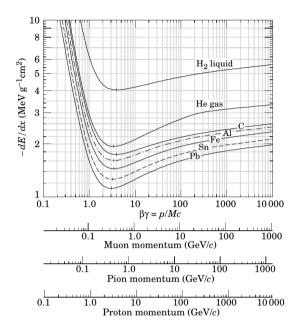

The energy loss process that enters in formula 2.1 to determine the number of ionizations produced is described by the Bethe-Bloch equation 2.2 which gives the mean rate of energy loss for a moderately relativistic particle of charge *z* passing through a material with atomic number Z and mass number A:

$$-\left\langle \frac{dE}{dx} \right\rangle = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} \ln \left( \frac{2m_e c^2 \beta^2 \gamma^2 T_{\text{max}}}{I^2} \right) - \beta^2 \right]$$

(2.2)

where  $K = 4\pi N_A r_e^2 m_e c^2$ ,  $m_e$  is the electron mass,  $r_e$  is the classical electron radius,  $N_A$  is the Avogadro number,  $T_{\rm max}$  is the maximum kinetic energy that can be transferred to a free electron in a single collision and I is the mean excitation energy<sup>2</sup>. The most difficult parameter to determine is I and it is usually derived from measurements. Figure 2.3 shows the results obtained for several elements [47]. For a particle with mass M and momentum  $M\beta\gamma c$ , the maximum kinetic energy transfer  $T_{\rm max}$  is given by:

$$T_{\text{max}} = \frac{2m_e c^2 \beta^2 \gamma^2}{1 + 2\gamma m_e / M + (m_e / M)^2}$$

(2.3)

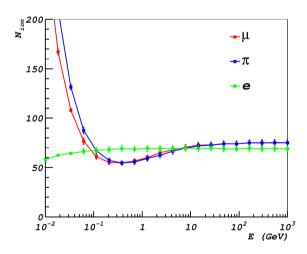

Figure 2.4 shows the mean energy loss rate for different particles in different substances while figure 2.5 shows the simulated most probable number number of ionizations per cm for different types of particles in  $\rm CO_2/DME$  (50/50), which is the chosen gas for the GridPix detectors.

The number of pairs produced can be estimated analytically. The production of pairs is a Poissonian process which can be described as:

$$P(n_p, < n_p >) = \frac{< n_p >_p^n \cdot e^{-< n_p >}}{n_p!}$$

(2.4)

$<sup>2</sup>m_e c^2 = 0.511$  MeV,  $r_e = 2.818$  fm,  $N_A = 6.022 \times 10^{23}$  mol<sup>-1</sup>

**Figure 2.3.** *The mean excitation potential I of atoms versus the atomic number Z.*

with  $\langle n_p \rangle = \frac{L}{\lambda}$  and  $\lambda = \frac{1}{n_e \sigma_I}$  ( $n_e$  is the electron density,  $\sigma_I$  is the ionization cross section and  $\lambda$  is then the mean distance between ionization events). The probability of having zero interactions is  $P(0) = exp - L/\lambda$ . Knowing the intrinsic efficiency of a gas detector one can then experimentally determine the parameters  $\lambda$  and  $\sigma_I$  of a gas.

# 2.2.2 Electron transport in the gas

Once an electron is produced it is accelerated by the electric field applied between the cathode and the grid. In vacuum, the electron would be accelerated to high velocity and reach the grid in a short time. However the electron will scatter isotropically with the gas molecules. The net effect at the microscopic level is a random motion which is superimposed to the preferred direction of drift (toward the grid). Thus, there are two terms to take into account to describe the electron moving in the gas under the effect of an electric field: one related to the drift velocity  $v_D$  which is caused by the electric field and one related to diffusion which is the macroscopic effect of the microscopic random motion.

In the most general case, the motion of an electron in an electromagnetic field is described by equation 2.5

**Figure 2.4.** Mean energy loss rate in liquid (bubble chamber) hydrogen, gaseous helium, carbon, aluminum, iron, tin, and lead.

**Figure 2.5.** Most probable number of ionizations per cm for different types of particles in CO<sub>2</sub>/DME (50/50). Calculation performed with Magboltz.

$$m\frac{d\vec{v}}{dt} = e\vec{E} + e(\vec{v} \times \vec{B}) + Q(t)$$

(2.5)

where  $\vec{v}$  is the instantaneous velocity, and Q(t) is a time dependent term due to collisions with the gas atoms. Assuming a time between collisions  $\tau$ ,  $\vec{E}$  and  $\vec{B}$  constant between collisions (and in general across the drift volume) and averaging over a  $\Delta t >> \tau$  then:

$$m < \frac{d\vec{v}}{dt} > = e(\vec{E} + < \vec{v} > \times \vec{B}) - \frac{m}{\tau} \vec{v}_D$$

(2.6)

which gives for the drift velocity:

$$\vec{v}_D = \mu \vec{E} \tag{2.7}$$

where

$$\mu = \frac{e\tau}{m} \tag{2.8}$$

is the electron mobility and depends on the gas. In general, one can distinguish two types of gases with respect to  $\mu$ : so called hot gases for which the electron loses a small fraction of its energy during the collision, giving  $\mu \propto \tau$ . Typical values of  $v_D$  are, for example, 3-5 cm  $\mu s^{-1}$  in Ar/CH<sub>4</sub> (90/10). The other type of gas is called cold: the electrons lose a lot of energy during the collisions and thus  $\mu$  is approximately constant and  $v_D \propto E$ . CO<sub>2</sub>/DME (50/50) is an example of a cold gas.

The drifting electrons scatter with the gas molecules. The final random motion that is the result of this scattering process can be characterized by the mean energy  $\epsilon$  and gives rise to diffusion. The total motion can be described by

$$\vec{J} = n\vec{v}_D - D\vec{\nabla}n\tag{2.9}$$

where the constant D is called diffusion coefficient. The term  $n\vec{v}$  describes the motion due to the drift while the second term describes the diffusion process. The motion of the electrons follows also the continuity equation:

$$\frac{\delta n}{\delta \tau} + \vec{\nabla} \cdot \vec{J} = 0 \tag{2.10}$$

The solution of equation 2.9 in the simplest case is then given by

$$n = \left(\frac{1}{\sqrt{4\pi Dt}}\right)^3 \cdot \exp(-\frac{r^2}{4Dt}) \tag{2.11}$$

where  $r = x^2 + y^2 + (z - v_D t)^2$ . From equation 2.11 one can see that the diffusion width  $\sigma$  of an electron cloud after starting point-like and traveling for a time t is:

$$\sigma = \sqrt{2Dt} \tag{2.12}$$

so that equation 2.11 can be rewritten as

$$n = \left(\frac{1}{\sigma\sqrt{2\pi}}\right)^3 \exp(-\frac{r^2}{2\sigma^2}) \tag{2.13}$$

However, experimentally one can see that this equation is not completely valid. The electric field introduces a non-symmetric behavior in the electron motion, which is described by introducing two different diffusion values, longitudinal  $(D_L)$  and transversal  $(D_T)$ . Taking into account this effect, equation 2.13 is adjusted as follows:

$$n = \left(\frac{1}{\sigma_L \sqrt{2\pi}}\right) \cdot \left(\frac{1}{\sigma_T \sqrt{2\pi}}\right)^2 \exp\left(-\frac{x^2 + y^2}{2\sigma_T} - \frac{(z - v_d t)^2}{2\sigma_L}\right) \tag{2.14}$$

# 2.2.3 Amplification

The electrons produced by ionization do not form a signal strong enough to be detected by current frontend electronics (for example, the input noise per pixel could be roughly  $100e^-$ ). For this reason, an amplification step is necessary and it is provided by the strong electric field present between the grid and the readout chip. For the purpose of this discussion such field is assumed homogeneous in the amplification region.

A primary electron can produce secondary ionization if the energy it receives from the electric field accelerates it enough to ionize another gas molecule. The secondary electrons can also receive enough energy to ionize more molecules, thus leading to the avalanche formation.

To provide a simple description of the multiplication process let's introduce a parameter  $\alpha$  called Townsend coefficient. Given a number of electrons n that travel for a distance dx in a region with uniform electric field E the number of electrons produced will be

$$dn = \alpha n dx \tag{2.15}$$

Integrating over the total path, the total number of electrons in the avalanche will then be

$$n(x) = n_0 \exp(\alpha x) \tag{2.16}$$

with  $n_0$  being the initial number of electrons. One can introduce the gas gain factor  $G = \frac{n}{n_0} = \exp(\alpha x)$  which depends only on the gas. Experimentally, it is possible to see that for values of  $\alpha x > 20$  the conditions are such that sparks start to occur in the gas, making the system unreliable.

This model, however, is too simple to explain the observations made in experiments. It is possible to obtain a more realistic result introducing an ionization parameter that depends on the avalanche size:  $\alpha(n,x) = \alpha(x)(1+\theta/n)$ . One can then find out that:

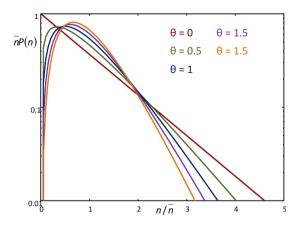

$$P(n) = \frac{1}{\bar{n}} \frac{(\theta+1)^{(\theta+1)}}{\Gamma(\theta+1)} \left(\frac{n}{\bar{n}}\right)^{\theta} e^{-\frac{(\theta+1)n}{\bar{n}}}$$

(2.17)

The previous distribution is called a Polya distribution and it describes quite well the behavior of the multiplication process for many gases by tuning the parameter  $\theta$ . However it must be said that the physical interpretation of such parameter is still unclear. Figure 2.6 shows different Polya distributions for different values of the parameter  $\theta$ .

# 2.2.4 Signal development

The multiplication process that takes place in the high electric field region leaves behind a large number of electron-ion pairs. Due to the electric field, the two constituents move in opposite directions toward the pixel pad or the grid. By construction, most of the pairs will be produced close to the anode. Considering also that the electrons have higher mobility the final result is that the electrons will reach their electrode much faster than the ions. The outcome is that most of the signal is induced by slower departing ions.

The charge induced can be described as a current flowing between the electrode and ground. Then, applying the Shockley-Ramo theorem [48] the current can be calculated as:

**Figure 2.6.** *Polya distribution for different values of*  $\theta$ *.*

$$i(t) = q \frac{\vec{v_d} \cdot \vec{E_w}}{V_m} \tag{2.18}$$

where  $\vec{v_d}$  is the drift velocity and  $\vec{E_w}$  and  $V_w$  are the weighting field and potential. These last two terms are calculated by setting all the potentials and the charges to zero except for the electrode under study. The total charge collected after the moving charge has finished drifting is then

$$Q = \int_0^{\Delta t} i(t)dt = q\Delta V \tag{2.19}$$

A more precise treatment for complex geometries can be found in [49], [50] and [51] but it is beyond the scope of this thesis.

# 2.3 Basic frontend characteristics

In the previous section the signal coming from the primary ionization electrons was amplified through a multiplication process. Once the avalanche has been produced one needs to collect the electrons and process the resulting signal to extract the needed information. In the following paragraphs the typical frontend chain implemented in many chips (as the ones shown in section 1.3) will be discussed.

Figure 2.7 shows the basic blocks which constitute a typical electronic frontend for a chip used as readout for particle detectors.

**Figure 2.7.** Basic blocks which constitute the frontend electronics of a typical chip used for the readout of particle detectors.

The avalanche signal is collected on the input pad and the resulting signal is amplified and shaped. It is worth noticing that the amplifying and shaping stages are usually performed together by the same circuit. The signal so generated is then compared to an external threshold in the discriminator. If the signal exceeds the threshold value it is then digitized and the data is transmitted on the data bus ready to be read out.

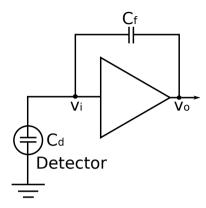

## 2.3.1 Charge sensitive amplifier

The signal coming from the electrons in the avalanche is collected at the input pad and amplified. While there are different types of amplifiers (voltage sensitive or current sensitive, for example) only the charge sensitive amplifier will be discussed here, since it is the one used in this thesis. Figure 2.8 shows the basic principle of a charge sensitive amplifier. The central part is an inverting amplifier to which is connected the detector, here represented with its capacitance  $C_d$ . In the ideal case the amplifier has an infinite input resistance so that no current can flow into it. Given an (inverting) gain -A ( $A \gg 1$ ), if the input signal produces a voltage  $v_i$  at the input then at the output there will be a corresponding  $v_0 = -Av_i$ . The voltage difference between the two ends of the feedback capacitance  $C_f$  will be then  $v_f = v_i(1+A)$  which gives a stored charge of  $Q_f = C_f v_f = C_f (A+1)v_i$ . Given the (mentioned) assumption that no current can flow into the amplifier one obtains that  $Q_i = Q_f$ : the entire input charge is collected on the feedback capacitance.

The amplifier input appears as a capacitance  $C_i = \frac{Q_i}{v_i}$ . Such a capacitance is called dynamic capacitance, since it varies with the input signal. It is then possible to calculate the conversion gain in terms of the input charge:

$$A_Q = \frac{v_o}{Q_i} = \frac{Av_i}{C_i v_i} = \frac{A}{C_i} = \frac{A}{(A+1)C_f} \approx \frac{1}{C_f}$$

(2.20)

**Figure 2.8.** Basic schematic of a charge sensitive amplifier. The detector is represented by an equivalent capacitance  $C_d$ .

In conclusion, in a charge sensitive amplifier the conversion gain is controllable simply with one parameter, the feedback capacitance  $C_f$ . The treatment of the realistic circuit requires a more complex analysis of the feedback loop and of the stability of the amplifier, but the basics remain the same: the gain element must have a high input impedance and the input capacitance must be large compared to the sensor capacitance to minimize the loss of input charge.

# 2.3.2 Shaper

After the input signal has been amplified the shaping stage takes place. The purpose of shaping the signal is twofold: on one hand one wants to transform the very fast input signal into a more easily processable shape; on the other hand one wants to cut off the noise introduced with the input stage to improve the signal to noise ratio. In general a shaper will put a limit at high frequencies, which will set the rise time, and at low frequencies, which will set the pulse duration. However, increasing too much the pulse duration comes with an augmented dead time of the electronic chain. The amplifier stage can be also used as shaping stage: since any real amplifier as a limited bandwidth the shaping of the signal comes naturally with it.

#### 2.3.3 Discriminator

In the simplest form a discriminator takes as input the shaped signal and compares it to an externally set threshold: if the signal is above threshold the discriminator output goes high and the presence of a pulse is recorded. This system

is called binary, because the only thing it does is detecting the presence/absence of a signal<sup>3</sup>.

# 2.4 GridPix at work: an example

For tracking applications one is often interested in minimizing the thickness of the drift volume, to minimize the material. For GridPix the minimum possible height is 1 mm, since with smaller drift volumes the probability of having ionization is so small that the efficiency suffers.

Consider as an example figure 2.9: two events are shown side by side. The left event has been recorded with a detector that has a 1 mm drift height, while for the detector used to record the event on the right the drift height is 1.9 cm. It is clear that for the former event the track reconstruction is quite difficult because the number of electrons produced by ionization is small, hence the resolution will be poorly determined.

Figure 2.9. Event recorded with two GridPix detectors, with 1 mm (left) and 1.9 cm (right) drift height respectively. With such a small number of primaries detected in the left case, it is difficult to perform a good track reconstruction.

<sup>&</sup>lt;sup>3</sup>In more complex applications one might want to record the length of the signal (Time over Threshold (ToT)) or its moment of arrival (Time of Arrival (ToA)). In those cases the output of the discriminator has to be a linear function of the input pulse.

In particular, the resolution of GridPix is degraded by several factors:

- diffusion, both in the x-y plane of the readout chip and in the perpendicular z direction;

- time resolution, since it directly affects the reconstruction of the z point of production of the electron;

- pixel size, which affects the resolution in the x-y plane;

- timewalk.

In this thesis we will focus on improving the resolution by means of improving the pixel chip used as readout for a GridPix detector. In particular, to increase the resolution in the z direction it is necessary to have available a high time resolution, down to a nanosecond to be able to reconstruct with high precision the production point of an electron in the drift volume. Having available such a readout chip will allow to reconstruct events like the one on the left in figure 2.9 with good precision.

There are different approaches available to reach such resolution, but it is important to point out the principal constraints that must be taken into account to decide which solution is best for the design of a pixel chip.

- Area: the circuit must fit in a relatively small area, since what is needed is a per pixel high resolution time measurement. Hence the pixel should be kept as small as possible to not degrade the x-y resolution but large enough to contain all the required logic;

- power consumption: due to high occupancy in some tracking applications,

a big portion of the chip might be active at the same time; it is then funda mental to keep the power consumption at reasonable levels. Moreover, low

power consumption means less cooling requirements which in turn means

less material in the detector and thus leads to a better spatial resolution.

# 2.5 High precision time measurements

There are a number of techniques available to measure time intervals per pulse duration with integrated circuits with high precision ([52], [53]) and each one of them has its own advantages and disadvantages. We are specifically interested in obtaining a nanosecond resolution with a relatively long dynamic range in the order of hundreds of microseconds; the former for tracking applications, the latter for large TPC applications similar to the one proposed for the International Linear Collider (ILC). For the purpose of this work, the main features to take into

account to decide which method is better are the area occupied and the power budget.

A first distinction that can be made when talking about time measurements is the type of measure performed: absolute or relative. In an absolute time measurement the moment of detection of the signal is timestamped using a system wide clock which is sent to all the Time to Digital Converters (TDCs). In a relative time measurement the arrival time is instead measured with respect to a fixed signal (usually a common stop) that is sent at a known time.

Additionally, one can differentiate between analog and digital methods, even though a digitization of the time interval measured occurs also in some analog methods to simplify the readout. In general, analog methods are based on current integration while digital methods are based on a counting principle. A brief review of some common solutions will be presented in the following paragraphs, highlighting in particular the methods suited for a future implementation in a pixel chip.

### 2.5.1 Ramp interpolate

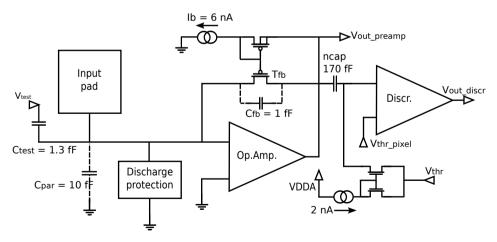

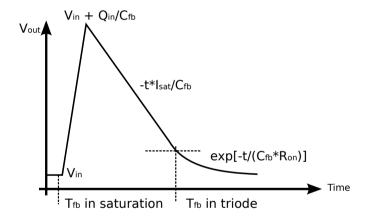

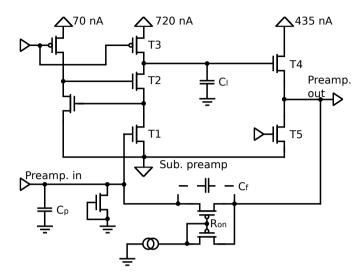

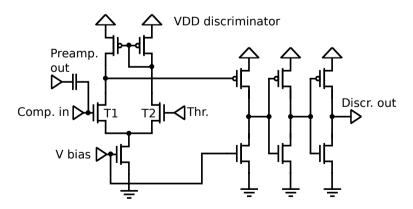

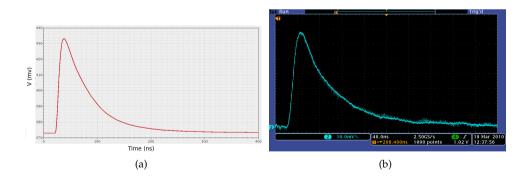

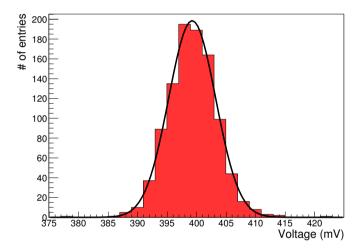

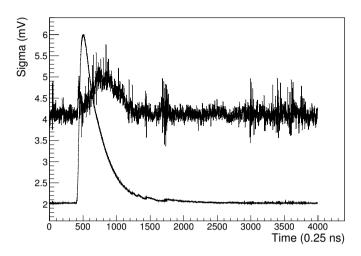

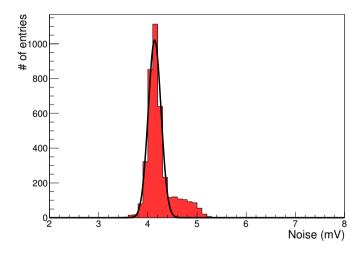

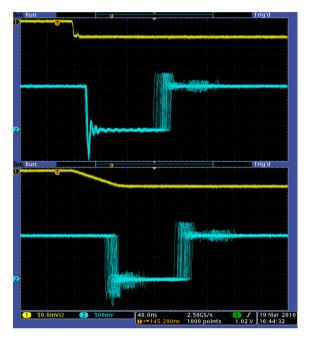

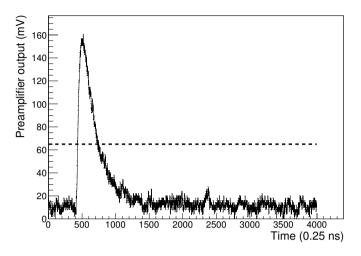

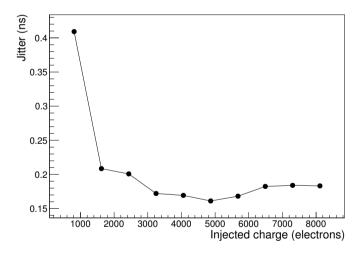

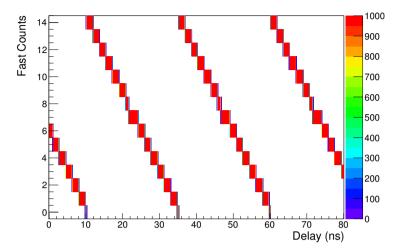

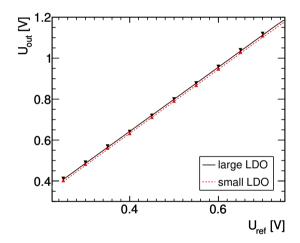

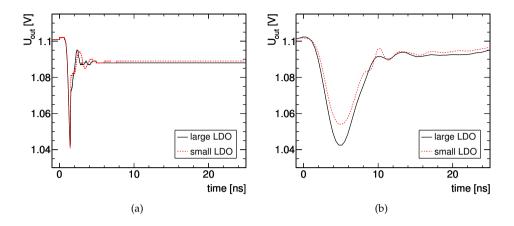

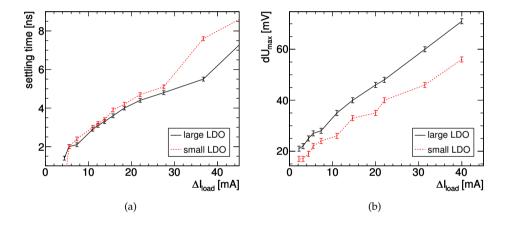

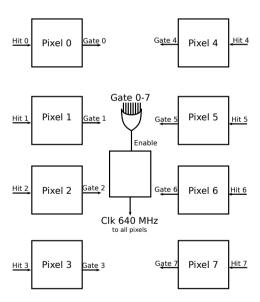

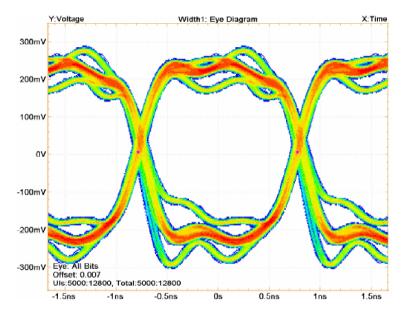

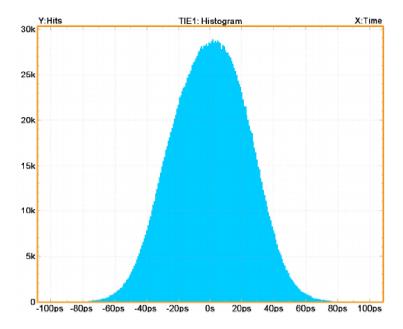

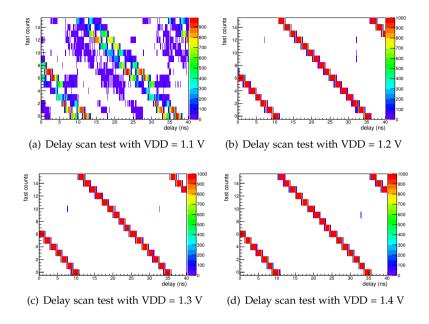

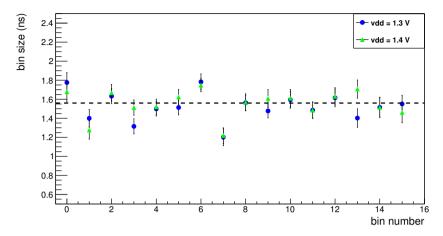

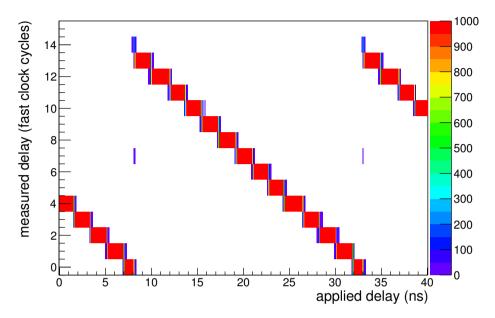

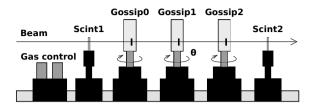

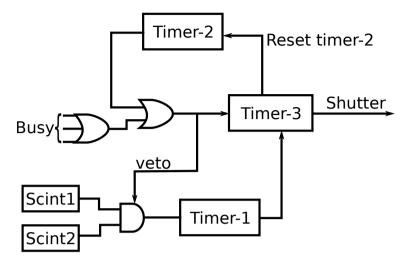

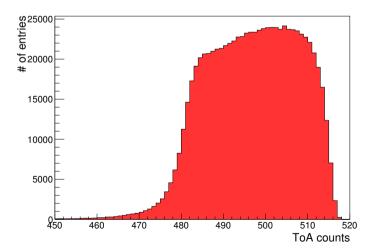

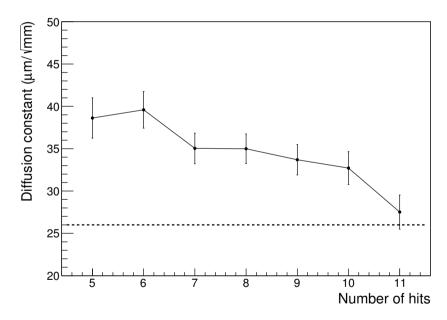

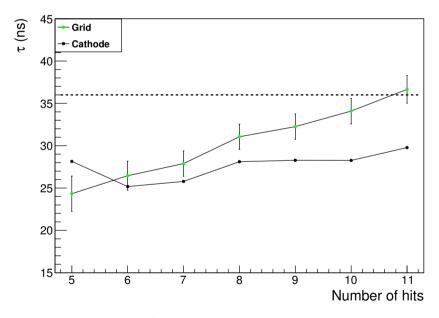

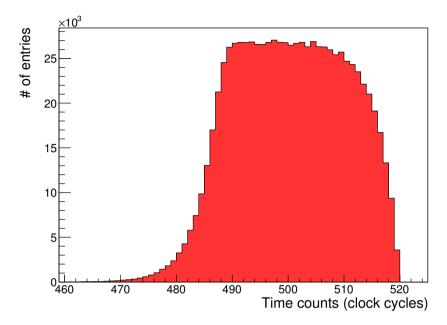

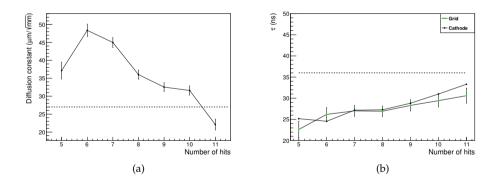

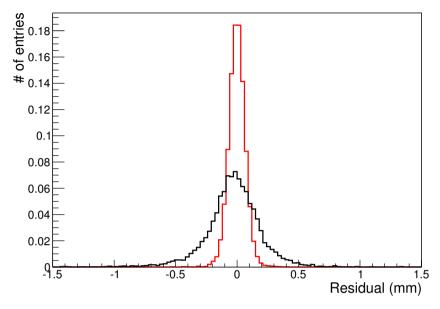

A simple analog method to measure a time interval involves the use of a capacitor. The capacitor is initially discharged at zero Volt and it is charged with a constant current  $I_0$  when the start event occurs until the stop arrives. The applied constant current causes the voltage across the capacitor to linearly increase to the value  $V_f$ . When the charging process is completed,  $V_f$  can be measured using an Analog to Digital (ADC) converter.