FERMILAB-Pub-96/008-E CDF

# Capacitance Measurements of Double-Sided Silicon Microstrip Detectors

M.A. Frautschi, M.R. Hoeferkamp and S.C. Seidel For the CDF Collaboration

Fermi National Accelerator Laboratory P.O. Box 500, Batavia, Illinois 60510

The New Mexico Center for Particle Physics University of New Mexico Albuquerque, New Mexico 87131

January 1996

Submitted to Nuclear Instruments and Methods

#### Disclaimer

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, expressed or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

# CAPACITANCE MEASUREMENTS OF DOUBLE-SIDED SILICON MICROSTRIP DETECTORS

M. A. Frautschi, M. R. Hoeferkamp, S. C. Seidel The New Mexico Center for Particle Physics The University of New Mexico Albuquerque, NM 87131

20 September 1995

#### Abstract

Direct measurements of the total capacitance with respect to ground of both the nand p-sides of double—and single—metal silicon microstrip detectors over six frequency

decades are described. Individual measurements of contributions to the total capacitance of a single strip are described. These include the detector's backplane capacitance

and its coupling and interstrip capacitances. The combination of the constituent capacitances is shown to be consistent with the direct measurement and with a SPICE

simulation. Additional n-side contributions due to the second-metal layer are also included in the direct measurement of total capacitance and in simulation. Measurements

on detectors from a variety of vendors and with several geometries are compared with

those of other workers. Detailed protocols for specific apparatus are given. A discussion of the isolation and grounding requirements for each class of measurement and a

comparison of several meters is included.

### Contents

| 1 | Inte | DUCTION                                                           | 6   |

|---|------|-------------------------------------------------------------------|-----|

| 2 | Bas  | C DETECTOR PARAMETERS                                             | 7   |

| 3 | SIMU | ATION 1                                                           | l 1 |

|   | 3.1  | Goals                                                             | 11  |

|   | 3.2  | THE SPICE SIMULATION                                              | 11  |

|   |      | 3.2.1 SPICE Model, Double-Sided Detector                          | 11  |

|   |      | 3.2.2 SPICE Model, Component Value Calculations                   | 15  |

|   |      | 3.2.3 SPICE Model, Capacitance Meter                              | 16  |

|   | 3.3  | Results                                                           | 17  |

| 4 | Мга  | UREMENTS 1                                                        | L 7 |

| - |      |                                                                   |     |

|   | 4.1  |                                                                   | 18  |

|   | 4.2  | OPERATING VOLTAGE                                                 | 18  |

|   | 4.3  | Typical Measurement Procedure                                     | 18  |

|   | 4.4  | BULK CAPACITANCE, DEPLETION VOLTAGE, AND BACKPLANE CAPACITANCE 1  | 19  |

|   |      | 4.4.1 Theory                                                      | 19  |

|   |      | 4.4.2 Procedure                                                   | 21  |

|   |      | 4.4.3 Estimate of Depletion Voltage Uncertainty                   | 22  |

|   | 4.5  | P-SIDE MEASUREMENTS                                               | 22  |

|   |      | 4.5.1 COUPLING CAPACITANCE                                        | 26  |

|   |      | 4.5.2 Interstrip Capacitance                                      | 29  |

|   |      | 4.5.3 P-SIDE SINGLE AC STRIP CAPACITANCE WITH RESPECT TO GROUND 2 | 29  |

|   | 4.6  | N-SIDE (DOUBLE-METAL) MEASUREMENTS                                | 32  |

|   |      | 4.6.1 COUPLING CAPACITANCE                                        | 32  |

|   |      | 4.6.2 Interstrip and Overlap Capacitance                          | 32  |

|              |             | 4.6.3 N-SIDE SINGLE AC STRIP CAPACITANCE WITH RESPECT TO GROUND | 37 |

|--------------|-------------|-----------------------------------------------------------------|----|

|              | 4.7         | ESTIMATE OF CAPACITANCE UNCERTAINTY                             | 37 |

|              |             | 4.7.1 Systematic Errors                                         | 37 |

|              |             | 4.7.2 Nonuniformities in p-side Coupling Capacitance            | 38 |

| 5            | Sum         | MARY OF TOTAL CAPACITANCE MEASUREMENTS                          | 38 |

| 6            | Con         | CLUSION                                                         | 39 |

| 7            | Оυт         | CLOOK                                                           | 41 |

| 8            | Аск         | NOWLEDGEMENTS                                                   | 42 |

| $\mathbf{A}$ | Inst        | CRUMENTATION                                                    | 46 |

|              | <b>A.</b> 1 | COMMERCIALLY AVAILABLE EQUIPMENT                                | 46 |

|              | <b>A.2</b>  | CUSTOM MADE EQUIPMENT                                           | 47 |

|              |             | A.2.1 BIAS ISOLATION NETWORK                                    | 47 |

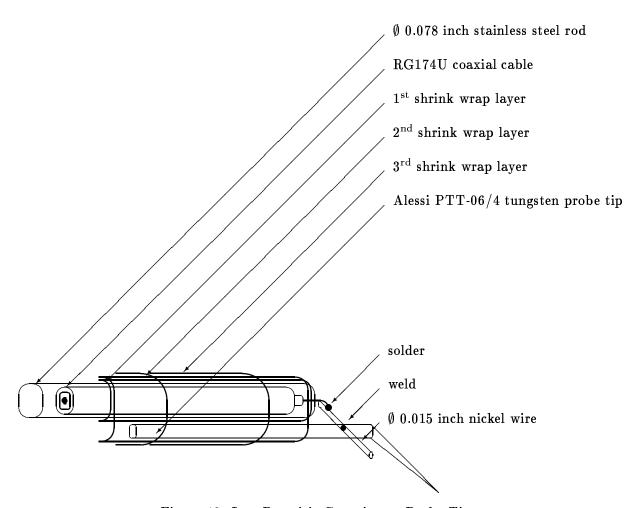

|              |             | A.2.2 Low Parasitic Capacitance Probe Tips                      | 50 |

|              |             | A.2.3 VACUUM CHUCK FOR LOWER SIDE PROBING                       | 50 |

|              |             | A.2.4 BIAS DISTRIBUTION NETWORK                                 | 52 |

|              | A.3         | Isolation and Grounding                                         | 52 |

| В            | Pro         | TOCOLS                                                          | 55 |

|              | B.1         | GENERAL PREPARATION FOR CAPACITANCE MEASUREMENTS                | 55 |

|              | B.2         | CAPACITANCE METER CALIBRATION                                   | 56 |

|              |             | B.2.1 HP 4192A CALIBRATION                                      | 57 |

|              |             | B.2.2 HP 4284A CALIBRATION                                      | 58 |

|              | B.3         | MEASUREMENT FREQUENCY SELECTION                                 | 59 |

|              | B.4         | IDENTIFICATION OF ADJACENT INTERLEAVED STRIPS                   | 59 |

|              | R 5         | PROBE TIP PREPARATION                                           | 61 |

### List of Tables

|   | 1                                    | DETECTOR TYPES                                                                                                                                                                                                                                   | 8                                            |

|---|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|   | 2                                    | NOMINAL P-SIDE DETECTOR PARAMETERS                                                                                                                                                                                                               | 10                                           |

|   | 3                                    | Nominal N-side Detector Parameters                                                                                                                                                                                                               | 10                                           |

|   | 4                                    | SPICE MODEL COMPONENTS                                                                                                                                                                                                                           | 16                                           |

|   | 5                                    | Typical Operating Voltages                                                                                                                                                                                                                       | 18                                           |

|   | 6                                    | BACKPLANE CAPACITANCE FOR UNIRRADIATED DETECTORS                                                                                                                                                                                                 | 22                                           |

|   | 7                                    | Depletion Voltage Uncertainties                                                                                                                                                                                                                  | 23                                           |

|   | 8                                    | MEASURED CAPACITANCE UNCERTAINTIES                                                                                                                                                                                                               | 37                                           |

|   | 9                                    | SUMMARY OF MEASURED AND SIMULATED CAPACITANCES                                                                                                                                                                                                   | 40                                           |

|   | 10                                   | BIAS ISOLATION NETWORK COMPONENTS                                                                                                                                                                                                                | 50                                           |

|   | 11                                   | PROBE TIP ETCHER COMPONENTS                                                                                                                                                                                                                      | 62                                           |

|   |                                      |                                                                                                                                                                                                                                                  |                                              |

| L | ist d                                | of Figures                                                                                                                                                                                                                                       |                                              |

| L | ist o                                | Of Figures  CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR                                                                                                                                                                           | 9                                            |

| L |                                      |                                                                                                                                                                                                                                                  | 9                                            |

| L | 1                                    | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR                                                                                                                                                                                       |                                              |

| L | 1 2                                  | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR SPICE MODEL OF A SINTEF/SI SVX II PROTOTYPE DETECTOR                                                                                                                                  | 12                                           |

| L | 1<br>2<br>3                          | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR SPICE MODEL OF A SINTEF/SI SVX II PROTOTYPE DETECTOR                                                                                                                                  | 12<br>13                                     |

| L | 1<br>2<br>3<br>4                     | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR  SPICE Model of a SINTEF/SI SVX II PROTOTYPE DETECTOR  SPICE Model of a SINTEF/SI DS641/640 DETECTOR                                                                                  | 12<br>13<br>14                               |

| L | 1<br>2<br>3<br>4<br>5                | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR  SPICE Model of a SINTEF/SI SVX II PROTOTYPE DETECTOR  SPICE Model of a SINTEF/SI DS641/640 DETECTOR  DETECTOR CROSS SECTIONAL VIEWS                                                  | 12<br>13<br>14<br>23<br>24                   |

| L | 1<br>2<br>3<br>4<br>5                | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR  SPICE Model of a SINTEF/SI SVX II PROTOTYPE DETECTOR  SPICE Model of a SINTEF/SI DS641/640 DETECTOR  DETECTOR CROSS SECTIONAL VIEWS                                                  | 12<br>13<br>14<br>23<br>24                   |

| L | 1<br>2<br>3<br>4<br>5<br>6<br>7      | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR SPICE MODEL OF A SINTEF/SI SVX II PROTOTYPE DETECTOR SPICE MODEL OF A SINTEF/SI DS641/640 DETECTOR                                                                                    | 12<br>13<br>14<br>23<br>24<br>25             |

| L | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR SPICE Model of a SINTEF/SI SVX II PROTOTYPE DETECTOR SPICE Model of a SINTEF/SI DS641/640 DETECTOR DETECTOR CROSS SECTIONAL VIEWS SINTEF/SI DS641/640 DEPLETION VOLTAGE DETERMINATION | 12<br>13<br>14<br>23<br>24<br>25<br>27       |

| L | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | CAPACITANCES OF A DOUBLE-SIDED SILICON MICROSTRIP DETECTOR SPICE Model of a SINTEF/SI SVX II PROTOTYPE DETECTOR SPICE Model of a SINTEF/SI DS641/640 DETECTOR                                                                                    | 12<br>13<br>14<br>23<br>24<br>25<br>27<br>28 |

| 13 | HP 4192A MEASUREMENT OF P-SIDE TOTAL CAPACITANCE         | 34 |

|----|----------------------------------------------------------|----|

| 14 | HP 4284A MEASUREMENT OF P-SIDE TOTAL CAPACITANCE         | 35 |

| 15 | N-SIDE COUPLING CAPACITANCE                              | 36 |

| 16 | EXTERNAL DC VOLTAGE BIAS PROTECTION CIRCUIT              | 48 |

| 17 | Effect of Low Level LCR Input Isolation                  | 49 |

| 18 | LOW PARASITIC CAPACITANCE PROBE TIP                      | 51 |

| 19 | SPICE SIMULATION OF LCR METER AND POWER SUPPLY ISOLATION | 53 |

| 20 | P-SIDE INTERSTRIP CAPACITANCE: HP 4284A                  | 54 |

#### 1 Introduction

This paper describes simulation and direct measurement of the total capacitance with respect to ground and several of its principle constituents for double-sided [1, 2] silicon microstrip detectors. The sum of the constituents is shown to be consistent with the direct measurement of the total capacitance and with a lumped element electrical model (SPICE [3] simulation). We compare these methods with those of other workers, including those based on noise measurements using calibrated front-end electronics bonded to detectors. The intent is to predict the overall signal-to-noise performance of a complete system, or "ladder," <sup>1</sup> of double-sided sensors and read-out electronics.

The techniques described in this paper permit comparison of various detector geometries from the standpoint of their capacitance as a predictor of noise performance. Capacitance measurements taken before and after irradiation allow specification of the final design that will maximize the useful performance lifetime of the device. It is important to emphasize, however, that these methods are no substitute for signal-to-noise measurements made on production ladders with the final data acquisition system. This will contain details such as the bandwidth, form factors, shaping and integration times of the read-out electronics, the capacitances distributed throughout the sensor (as opposed to modeling the detector network as a single, discrete capacitor connected to the input amplifier), proximity of read-out electronics to the sensor, as well as the effects neighboring sensors may induce, all of which may impact the signal-to-noise ratio.

SVX II [4], the upgrade of the silicon microstrip detector at the Fermilab Collider Detector Facility will incorporate double-sided technology to provide both  $r-\phi$  and r-z track reconstruction. One of the major branch points in the design of this detector is the choice between double-metal and glass z-print interconnect technology [5] to connect the r-z read-out strips, which run transverse to the ladders, to hybrids at the ends. While ladder assembly is considerably simplified in the double-metal case, the second-metal layer contributes significantly to the total capacitance with respect to ground presented to the front-end amplifier, thereby lowering the signal-to-noise ratio. The effect of this additional capacitance on the signal-to-noise ratio and any changes it may undergo as a result of irradiation are factors driving this choice.

The signal-to-noise ratio is critical to realization of the full track reconstruction and resolution capabilities of SVX II. Noise voltages,  $V_{\text{noise}}^i$ , present at the input of the SVX III front-end amplifier, are reflected as equivalent charges,  $Q_{\text{noise}}^i$ , which compete with the (approximately fixed) charge collected from the ionizing track,  $Q_{\text{signal}}$ . The greater the capacitive load,  $C_{\text{input}}$ , presented to the input of the front-end amplifier, the lower the signal-to-noise ratio (S/N) is [6]:

$$S/N = rac{Q_{

m signal}}{\Sigma_i \; Q_{

m noise}^i}$$

<sup>&</sup>lt;sup>1</sup>Generally, in silicon vertex detectors, several silicon sensors are supported by rails and bonded to each other and to electronics at one or both ends. This basic functional unit is known as a ladder.

$$pprox rac{Q_{

m signal}}{C_{

m input} \; \Sigma_i \; V_{

m noise}^i}.$$

(1)

The various contributions to the S/N are uncorrelated, hence the summations are in quadrature.

The contributions to the capacitance presented to the front-end amplifier by the detector are summarized below. For both the p- and n-sides, these are:

•  $C_{\text{coupling}}$ : AC metal strip to DC implant strip (typically 10 pF/cm)

which capacitively divides the signal with:

- ullet  $C_{

m backplane}^{i-{

m side}}$   $(i=n \ {

m or} \ p)$ : DC implant strip to ground plane (typically 0.35  $p{

m F/cm}$ )

- ullet  $C_{

m interstrip}^{

m DC}$ : DC implant to neighbor DC implant (typically 1  $p{

m F/cm/neighbor}$ )

- ullet  $C_{

m interstrip}^{

m AC}$ : AC metal to neighbor AC metal (typically 0.5  $p{

m F/cm/neighbor}$ )

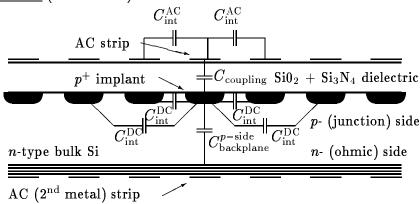

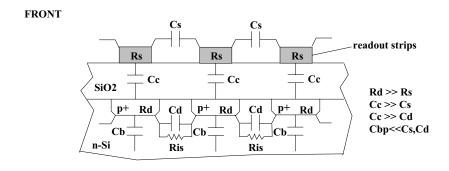

In addition to the four capacitances listed above, the second-metal layer introduces a network of capacitive couplings between read-out strips. These are shown in the lower half of Figure 1. These affect resolution and track reconstruction and may potentially impact the choice of a multiplexing scheme. The second-metal layer on the *n*-side contributes:

- $C_{11}$ : 1st metal AC strip to neighbor 1st metal AC strip ( $\approx 1/3~p\text{F/cm/neighbor}$ )

- ullet  $C_{12}\colon 1^{

m st}$  and  $2^{

m nd}$  metal overlap ( $pprox 10~f{

m F/overlap})$

- ullet  $C_{22}$ : 2<sup>nd</sup> metal AC strip to neighbor 2<sup>nd</sup> metal AC strip ( $pprox 2/3~p{

m F/cm/neighbor})$

Less than 1 fF/overlap [7] is expected for the equivalent  $C_{12}$  with the glass z-print technology. The various capacitances are schematically represented in Figure 1.

#### 2 Basic Detector Parameters

For prototyping purposes, detectors of eight different geometries were manufactured by the SINTEF/SI and Micron, Ltd. firms. (Two sensor sizes, one "long" and the other "short" were chosen to exploit the maximum area of the standard four-inch diameter silicon wafer.) The abbreviations used to identify each manufacturer and geometry are given in Table 1. The detector parameters pertinent to capacitance measurements and simulation for SINTEF/SI, Micron, Ltd., and Hamamatsu Photonics, K.K. detectors are given in Tables 2 and 3 for the p- and n-sides, respectively. The last column in Table 3 refers to the multiplexing factor. This indicates the number of first metal strips that are bonded

to a second metal strip. This technique is used to reduce the number and density of the n-side read-out electronics in exchange for additional capacitance (lower signal-to-noise ratio) and increased possibility of "ghost" hits. (Since it is impossible to distinguish which of the implant strips was hit, the track reconstruction algorithm assumes that all strips were hit and then attempts to fit track segments to strips in several layers; the best fit strips are included. The other, spurious, tracks are referred to as ghosts). The Hamamatsu detectors use non-integral multiplexing, m=1.5. This means that 2/3 of the implant strips are connected to two implants while the remaining 1/3 are connected to one implant. A ladder constructed of two detectors would have m=3.

| Designator | Description                                      |

|------------|--------------------------------------------------|

| SI         | SINTEF/SI a                                      |

| MI         | Micron Semiconductor, Ltd. b                     |

| HA         | Hamamatsu Photonics, K.K. <sup>c</sup>           |

| A          | "short" geometry; p-side intermediate strips [8] |

| В          | "short" geometry                                 |

| C          | "long" geometry; n-side intermediate strips      |

| D          | "long" geometry                                  |

| SM         | n-side single-metal                              |

| DM         | n-side double-metal                              |

Table 1: A brief listing of detector types.

a SINTEF/SI

P.O. Box 124 Blindern

N-0314 Oslo, Norway.

b Micron Semiconductor, Limited

1 Royal Buildings, Marlborough Road

Churchill Industrial Estate, Lancing

Sussex BN15 8UN, England.

Hamamatsu Photonics, K.K.

Solid State Division

1126-1 Ichino-cho

Hamamatsu-shi, 435 Japan.

cross section (not to scale):

Figure 1: Capacitances of a double-sided, double-metal silicon microstrip detector. The upper half illustrates the p-side, in profile view, while the lower half displays the n-side seen from above. The dielectric is composed of  $\mathrm{SiO}_2$  and  $\mathrm{Si}_3\mathrm{N}_4$  layers and is passivated with polyimide or an additional  $\mathrm{SiO}_2$  layer not shown in the figure.  $C_{\mathrm{interstrip}}^{\mathrm{DC}}$  is abbreviated  $C_{\mathrm{int}}^{\mathrm{DC}}$ . On the n-side,  $C_{\mathrm{interstrip}}^{\mathrm{DC}}$  refers to the coupling between implant strips,  $C_{11}$  denotes coupling between strips of the first metal layer,  $C_{12}$  refers to coupling between overlapping regions of the first and second metal layers, and  $C_{22}$  refers to coupling between strips of the second metal layer.

Detector implant metalinter-Туре # length width pitch width mediate strips (cm)  $(\mu m)$  $(\mu m)$  $(\mu m)$ strips? SINTEF/SI SI-A 768 4.1 10 25 7.5yes SI-B 384 4.1 10 507.5no SI-C 256 8.2 10 50 7.5 no SI-D 8.2256 10 507.5no DS641/640 [9] 7 1280 5.625 10 yes Micron, Ltd. MI-A768 4.1 11 25 10 yes MI-B 384 4.1 11 5010 no MI-C 256 8.3 11 50 10 no MI-D 256 8.3 11 50 10 no K.K. Hamamatsu Photonics, HA-0 256 7.61 14 608 no HA-1 384 5.88 14 62 8 no

Table 2: Nominal p-side detector parameters.

Table 3: Nominal n-side detector parameters.

| Detector  |                           | impl   | lant           |                    | $1^{\mathrm{st}}$ metal | 2      | nd metal           |                    | p-stop         | inter-  |               |

|-----------|---------------------------|--------|----------------|--------------------|-------------------------|--------|--------------------|--------------------|----------------|---------|---------------|

| Туре      | #                         | length | width          | $_{ m pitch}$      | $\mathbf{width}$        | length | $\mathbf{width}$   | $\mathbf{pitch}$   | width a        | mediate | m             |

|           | strips                    | (cm)   | $(\mu { m m})$ | $(\mu \mathrm{m})$ | $(\mu { m m})$          | (cm)   | $(\mu \mathbf{m})$ | $(\mu \mathrm{m})$ | $(\mu { m m})$ | strips? |               |

|           | SINTEF/SI                 |        |                |                    |                         |        |                    |                    |                |         |               |

| SI-A      | 384                       | 2.0    | 12             | 103                | 7.5                     | 4.1    | 7.5                | 50                 | 60             | no      | 1             |

| SI-B      | 384                       | 2.0    | 12             | 103                | 7.5                     | 4.1    | 7.5                | 50                 | 60             | no      | 1             |

| SI-C      | 1024                      | 1.3    | 12             | 79                 | 7.5                     | 8.2    | 7.5                | 50                 | 40             | yes     | 2             |

| SI-D      | 512                       | 1.3    | 12             | 158                | 7.5                     | 8.2    | 7.5                | 50                 | 120            | no      | 2             |

| DS641/640 | 640                       | 3.1    | 7              | 85                 | 10                      | 5.6    | 7                  | 50                 |                | no      | 1             |

|           |                           |        |                |                    | Micron, I               | td.    |                    |                    |                |         |               |

| MI-A      | 384                       | 1.9    | 11             | 103                | 10                      | 4.1    | 10                 | 50                 | 58             | no      | 1             |

| MI-B      | 384                       | 1.9    | 11             | 103                | 10                      | 4.1    | 10                 | 50                 | 58             | no      | 1             |

| MI-C      | 1024                      | 1.2    | 11             | 80                 | 10                      | 8.3    | 10                 | 50                 | 40             | yes     | 2             |

| MI-D      | 512                       | 1.2    | 11             | 160                | 10                      | 8.3    | 10                 | 50                 | 115            | no      | 2             |

|           | Hamamatsu Photonics, K.K. |        |                |                    |                         |        |                    |                    |                |         |               |

| HA-0      | 1024                      | 1.53   | 18             | 74.5               | 12                      | 7.64   | 8                  | 59                 | 45.5           | no      | <b>2</b> b    |

| HA-1      | 1152                      | 2.37   | 16             | 66                 | 10                      | 7.64   | 8                  | 60                 | 39             | no      | $1.5^{\rm c}$ |

<sup>&</sup>lt;sup>a</sup> See References [10, 11].

b 1st metal strips are ganged in sets of two.

c 1st metal strips are ganged in sets of two, alternating with unganged strips.

#### 3 SIMULATION

#### 3.1 GOALS

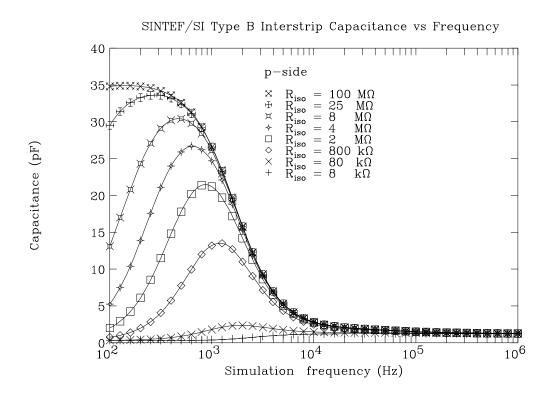

Detailed circuit models of silicon microstrip detectors were developed to aid in the interpretation of the capacitance measurements. The models were based on discrete electrical circuit components (capacitors and resistors). The SPICE electrical simulator was used to predict and verify the performance of the detector circuit models. SPICE employs the solution of the matrix equations describing the circuit voltages, currents and resistances (or conductances). (A field simulator using a boundary element solution method was not used.) The models were used to predict frequency response curves for the various detector geometries, then compared to the measurements obtained with LCR meters.

#### 3.2 THE SPICE SIMULATION

#### 3.2.1 SPICE MODEL, DOUBLE-SIDED DETECTOR

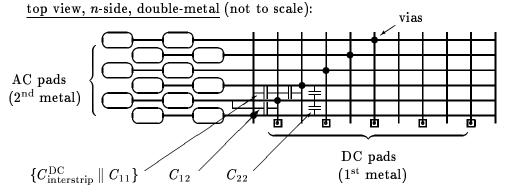

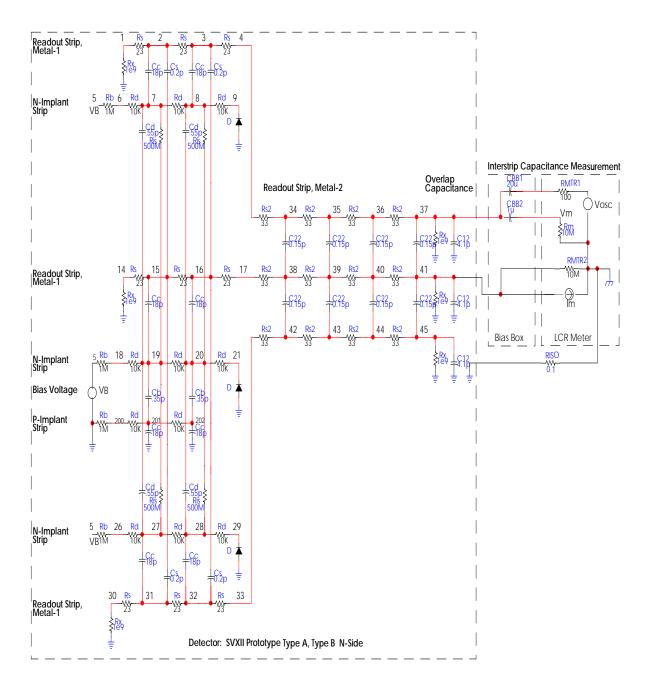

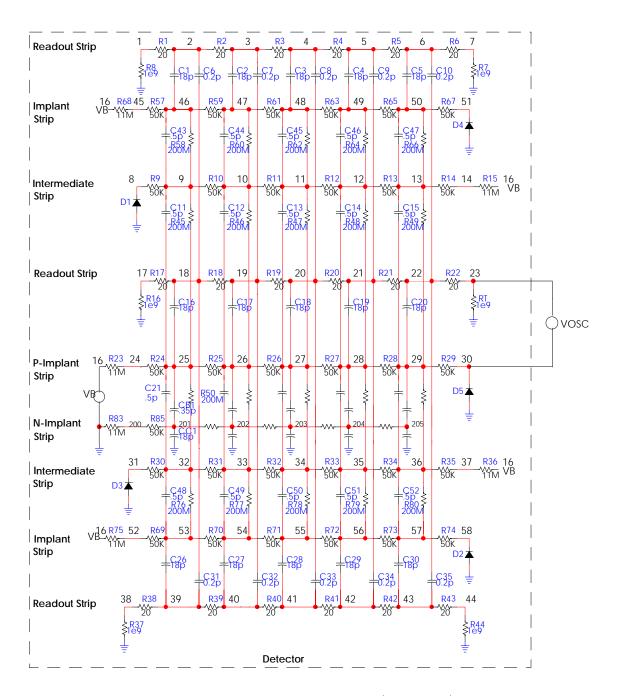

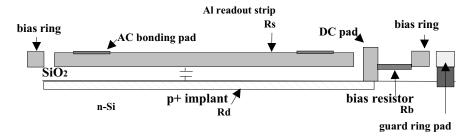

The development of an accurate electrical network (SPICE) model of detector resistive, capacitive, and diode junction elements is an essential step (see Figures 2 and 3). The distributed nature of the coupling capacitor formed by the implant, dielectric (SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> layers) and aluminum layers (see Figure 4) mandates using a lumped model approach which involves connecting many small subcircuits in series. This approach was also used in the SPICE calculations performed in Reference [12]. Discrete, passive, components are used to represent each small section of the implant–readout strip combination (the lumped strip segment). Each lumped strip segment (see Figure 4) consists of a coupling capacitance ( $C_{\rm interstrip}^{\rm AC}$ ), DC interstrip capacitance ( $C_{\rm interstrip}^{\rm AC}$ ), implant strip resistance ( $R_{\rm implant}$ ), readout strip resistance ( $R_{\rm readout}$ ), and interstrip resistance ( $R_{\rm interstrip}$ ).

An adequate number of lumps must be used such that the natural frequencies of the lumped elements do not occur in the frequency range of the simulation run. One lump per centimeter was determined to be adequate for these simulations. Around the lumped segments, additional components are added to represent the backplane capacitance  $(C_{\text{backplane}}^i, \text{ where } i=n \text{ or } p)$ , bias resistance  $(R_{\text{bias}})$ , and p-n junction currents of the strips (D). Table 4 lists the various input parameters and their symbols as used in the model and this paper.

Three strips were included in the model of a detector with no intermediate strips <sup>2</sup> (see Figure 2), and five strips were used for the detector with intermediate strips (see Figure 3). For detectors which have intermediate strips and 2-times multiplexing, ten strips were included in the simulation. The model for detectors with double-metal readout also included

<sup>&</sup>lt;sup>2</sup>Intermediate non-read-out strips are DC implant strips placed between read-out strips. Like the read-out strips, they have polysilicon bias resistors and collect charge left by ionizing tracks, however this charge is not coupled to an amplifier since there is no associated AC metal strip. Instead, depending on the geometry, a fraction of this charge is induced on each of the neighbor strips. See Reference [8].

Figure 2: SPICE model of the *n*-side of the SINTEF/SI SVX II type A or type B prototype detector. The LCR meter is shown configured for an interstrip capacitance measurement. The "Bias Box" is the SPICE representation of the Bias Isolation Network described in Appendix A.2.1.

Figure 3: SPICE model of the p-side of the SINTEF/SI DS641/640 detector. Some component references and values have been deleted for clarity. The values for the first lump of the n-implant strip are shown; values for similar components in the subsequent lumps are the same.

SIDE

Figure 4: Detector cross sectional views used for the SPICE simulation.

separate lumped segments of one lump per centimeter of second metal interstrip capacitance  $(C_{22})$ , overlap capacitance  $(C_{12})$ , and second metal strip resistance  $(R_{\text{readout}}^{\text{2nd}})$ . The interstrip capacitance terms were adjusted to include contributions from all the neighboring strips on a given detector. This adjustment factor is 0.1 pF/cm [13].

#### 3.2.2 SPICE MODEL, COMPONENT VALUE CALCULATIONS

The calculation of SPICE model component values and tolerances used as input width and thickness specifications of the implant strips, readout strips, and insulator supplied by the detector manufacturers. From these, the component values input to the model may be calculated. Published measurements [13] and calculations [14] were also used wherever possible. A listing of typical values is given in Table 4. The following methods were used in the calculation of the individual component values:

Coupling Capacitance  $(C_{\text{coupling}})$ : The simple parallel plate capacitor model;  $C_{\text{coupling}} = \frac{\epsilon/d}{d}$  yields the capacitance per unit area for a dielectric of permittivity  $\epsilon$  and thickness d.

Interstrip Capacitance ( $C_{\rm interstrip}^{\rm DC}$ ,  $C_{\rm interstrip}^{\rm AC}$ ): For the p-side, Figure 4 of [13] gives an estimate for  $C_{\rm total}$ . In the present model  $C_{\rm total} = (2 \times C_{\rm interstrip}^{\rm DC} + 2 \times C_{\rm interstrip}^{\rm AC}) + C_{\rm backplane}$ . The values obtained for adjacent strips have been scaled by 110 percent to account for the contributions of neighbors. First  $C_{\rm backplane}$  is calculated by scaling from the result given in [13], then  $C_{\rm interstrip}^{\rm AC}$  and  $C_{\rm interstrip}^{\rm DC}$  are estimated assuming that  $C_{\rm interstrip}^{\rm DC} = 3$   $C_{\rm interstrip}^{\rm AC}$ . For the n-side the p-stops  $^3$  are modeled. This is done using the observation that in most detector designs there is a gap between the n-strip and the p-stop which collects electrons attracted to the accumulation layer and increases the effective width of the n-strip [14]. Thus the width of the n-strip becomes  $W_{\rm eff} = {\rm pitch} - W_{p-{\rm stop}}$  [14]. With this correction then Figure 5 of [13] is used to obtain  $C_{\rm interstrip}^{\rm DC}$  and  $C_{\rm interstrip}^{\rm AC}$  as described above.

Backplane Capacitance ( $C_{\text{backplane}}^i$ , where i = n or p): Equation (8) and Figure 8 of [13] are used to calculate the backplane capacitance.

Double-Metal Capacitances: The second layer of metal in a double-metal readout scheme adds several capacitive components, two of which are included in the SPICE model. Equation (1) of [14] is used to calculate the interstrip capacitance of the second layer metal strips  $(C_{22})$ . Equation (3) of [14] is used to find the capacitance due to the overlaps of the first and second layer metal readout strips  $(C_{12})$ . Capacitance due to the overlapping of the second metal readout strip with the p-stops or intermediate strips is not modeled.

Implant Strip Resistance ( $R_{implant}$ ): Calculated from the manufacturer's specified sheet resistance.

Readout Strip Resistance ( $R_{

m readout}$ ): Calculated from the width and thickness of the Al

<sup>&</sup>lt;sup>3</sup> p-stops are "blocking" p-doped implant strips inserted between the n-strips. They defeat the accumulation layer that would otherwise increase with irradiation. This layer forms a conductive path between n-strips [10, 11].

| Syı                     | mbol                             | Name                           | Typical | Unit                   |

|-------------------------|----------------------------------|--------------------------------|---------|------------------------|

| SPICE <sup>a</sup> text |                                  |                                | Value   |                        |

| Сс                      | $C_{ m coupling}$                | Coupling Capacitance           | 18      | $p\mathrm{F/cm}$       |

| Cd                      | $C_{ m interstrip}^{ m DC}$      | DC Interstrip Capacitance      | 0.55    | $p\mathrm{F/cm}$       |

| Cs                      | $C_{ m interstrip}^{ m AC}$      | AC Interstrip Capacitance      | 0.2     | $p{ m F/cm}$           |

| C11                     | $C_{11}$                         | Interstrip Capacitance-Metal-1 | 0.75    | $p{ m F/cm}$           |

| C22                     | $C_{22}$                         | Interstrip Capacitance-Metal-2 | 0.15    | $p{ m F/cm}$           |

| C12                     | $C_{12}$                         | Overlap Capacitance            | 8       | $f{ m F/overlap}$      |

| Cb                      | $C_{ m backplane}^{n-{ m side}}$ | Backplane Capacitance          | 0.35    | $p\mathrm{F/cm}$       |

| Cb                      | $C_{ m backplane}^{p-{ m side}}$ | Backplane Capacitance          | 0.35    | $p\mathrm{F/cm}$       |

| Rd                      | $R_{ m implant}$                 | Implant Strip Resistance       | 50      | ${ m k}\Omega/{ m cm}$ |

| Rs                      | $R_{ m readout}$                 | Readout Strip Resistance       | 30      | $\Omega/\mathrm{cm}$   |

| Ris                     | $R_{ m interstrip}$              | Interstrip Resistance          | 500     | $\mathrm{M}\Omega$     |

| Rb                      | $R_{ m bias}$                    | Bias Resistance                | 2       | $M\Omega$              |

| D                       | D                                | p-n Junction Current           | 1       | $n{ m A/strip}$        |

<sup>&</sup>lt;sup>a</sup> Figures 2 and 3 use a different notation than the text.

Table 4: SPICE model components. See Section 3.2.1 and Figures 2 and 3.

strip.

Bias Resistance ( $R_{

m bias}$ ): Calculated from the manufacturer's specified sheet resistance.

Interstrip Resistance ( $R_{\rm interstrip}$ ): 500 megohms.

Currents (D): The diodes in Figures 2 and 3 represent the p-n junctions between the bulk and the implant strips. A leakage current of approximately 1nA per strip is specified in the diode model in order to establish a realistic DC current through the strip.

#### 3.2.3 SPICE MODEL, CAPACITANCE METER

Accurate representation of the measurement apparatus and fixturing setup (including the capacitance meter, bias isolation network, and cabling) was deemed necessary to represent properly effects external to the detector, such as grounding, isolation, and choice of probing points. The model of the LCR meter in Figure 2 is based on the "Auto Balance Bridge" technology common to the HP 4284A Precision LCR meter and HP 4192A Low Frequency Impedance Analyzer. These meters measure a complex impedance by injecting into the device under test a known AC voltage and phase signal over a range of frequencies, measuring the AC return current and phase, and calculating the impedance parameters (magnitude and phase of resistance, R, and reactance, X). The capacitance is extracted from the impedance measurement from the following relation:  $Im(I) = 1/X = 2 \pi f C$ ,

yielding C vs. f. The SPICE simulation performs these same operations.

The modeling of the isolation between the power supply return and the meter's AC signal return is discussed in Appendix A.3.

#### 3.3 Results

A complete summary of detector capacitance predictions by SPICE simulations for a sample population of vendors and geometries is shown in Table 9. The errors were estimated for each geometry by running 100 simulations in which each of the input parameters was subject to a uniform Monte Carlo variation over the tolerance range specified by the manufacturer, or  $\pm$  10% in cases where tolerances were not supplied. The SPICE model method for calculating detector capacitances gives results which are consistent with the measured capacitances to within 10 % for the n-side and to within 20 % for the p-side.

#### 4 Measurements

The intent of this paper is to demonstrate two methods for measuring the total capacitance with respect to ground presented to the front-end amplifier chip by a single strip of a silicon microstrip detector, including effects of neighboring strips, and a SPICE model for each geometry measured and each of two measurement methods. In one method, the constituents are individually measured and then summed. The other yields the total capacitance with respect to ground in a single, direct, measurement. These two methods and the SPICE models are shown to be consistent in Section 4.5.3. A summary of the results obtained by the direct method is presented in Section 5.

Several capacitance measurements will be discussed. First, the bulk capacitance, from which depletion voltage,  $V_{\rm depl}$ , and the capacitance between a single implant strip and the opposite side of the detector (its backplane)  $C_{\rm backplane}^{i-{\rm side}}$  (i=n or p), may be derived, is described. Then the coupling capacitance,  $C_{\rm coupling}$ , and interstrip capacitance,  $C_{\rm interstrip}$ , are presented in Sections 4.5.1 (for the p-side) and 4.5.2. The direct and summed methods for measuring the total capacitance,  $C_{\rm total}$ , with respect to ground, are described in Section 4.5.3.

Where the n- and p-side measurement procedures differ, appropriate detail is given. The protocols used for the measurements reported here are listed in Appendix B. While these procedures are specific to the instrumentation used for each measurement, not every procedure need be repeated for each measurement.

#### 4.1 APPARATUS

Measurements may be taken manually or by computer control using programs written in Microsoft QuickBASIC<sup>TM</sup> (with the appropriate IEEE 488 device drivers) and calls to the Hewlett-Packard 4192A or 4284A and Keithley 237 or with an object-oriented acquisition and analysis system such as National Instruments' LabVIEW<sup>TM</sup> (with appropriate "Virtual Instrument" drivers). Manual acquisition allows the operator to observe stability of the measurement prior to recording the data. Details of the apparatus may be found in Appendix A.

#### 4.2 OPERATING VOLTAGE

Nominal operating voltages are given in Table 5. These reflect considerations of full depletion of the silicon and prompt charge collection addressed in Section 4.4.

| Manufacturer              | Type           | $V_{ m oper} \  m (V)$ |

|---------------------------|----------------|------------------------|

| SINTEF/SI                 | DS641/640      | 50                     |

| SINTEF/SI                 | SVX II A,B,C,D | 80                     |

| Micron, Ltd.              | SVX II A,B,C,D | 50                     |

| Hamamatsu Photonics, K.K. | SVX II         | 50                     |

Table 5: Typical operating voltages.

#### 4.3 Typical Measurement Procedure

The general measurement procedure is as follows:

- Allow equipment to warm up for manufacturer's recommended time.

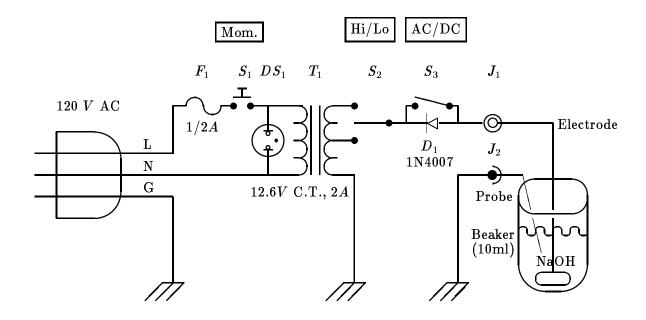

- Make DC bias connections through bias isolation network (Appendix A.2.1).

- Confirm isolation (Appendix A.3).

- Connect appropriate length extension, bias isolation network, and probe tips to LCR meter.

- Connect all grounds (LCR meter, power supply in OPERATE mode).

- Calibrate LCR meter (Appendix B.2).

- Mount detector in appropriate fixture (Appendix A.2.3).

- Land bias and guard ring probes on lower and upper sides of detector.

- Bring detector to full operating voltage (Section 4.2).

- Land LCR meter probe(s) as appropriate to the measurement.

- Record the data.

## 4.4 BULK CAPACITANCE, DEPLETION VOLTAGE, AND BACKPLANE CAPACITANCE

A procedure for measurement of the bulk capacitance of a complete silicon microstrip is described. From this, the depletion voltage (and therefrom the operating voltage) and the capacitance between a single strip and the opposite side of the the detector (the "backplane") may be measured.

#### 4.4.1 THEORY

Silicon microstrip detectors require a reverse-bias potential to create a region free of mobile carriers around the p-n junction. (These carriers would otherwise be available to combine with charge liberated by the passage of an ionizing particle, making detection of the charge – and therefore the particle – impossible.) This region is called the depletion layer. The bias voltage must be sufficient to deplete fully the available volume within the bulk, thereby maximizing the amount of charge collected from the ionizing particle and providing rapid collection of that charge.

The rapid collection of charge from the microstrip detector is important because the next generation of high luminosity colliders requires much faster charge integration than is used at present. During Run II of the Fermilab Tevatron, the beam crossing time will be reduced from 396 to 132 ns [15]. This places a significant constraint on the integration time, which for the front—end electronics of SVX II will be approximately 100 ns. To assure prompt <sup>4</sup> collection of the charge, a bias voltage of 20 V or more above full depletion (defined below) will be used to operate SVX II detectors. This reduces the effects of drift and diffusion. The same conditions are used for the detectors tested here.

Additional constraints of high voltage breakdown, power consumption, heating, shot noise (which is proportional to the square root of the leakage current), and microdischarge noise [18] drive the operating voltage in the opposite direction. Further, radiation damage beyond that sufficient to invert the bulk silicon increases the depletion voltage [19, 20, 21]. It is therefore desirable to operate the device near the minimum bias voltage required for prompt signal collection.

<sup>&</sup>lt;sup>4</sup>A SPICE simulation [16] of charge collection was run for SVX II prototype [17] detectors. In all configurations simulated, the collection time for the charge was under 60 ns.

Since the depletion voltage determines the operating voltage, a technique to measure the onset of full depletion is described. This technique is based on a model of the depletion layer as a parallel plate capacitor.

The bulk capacitance per unit area of the reverse-biased sensor is determined by the depth of the depletion layer, d:

$$C_{\text{bulk}} = \frac{\epsilon_{\text{Si}}}{d}$$

(2)

where  $\epsilon_{Si}$  is the permittivity of the bulk silicon. The applied bias potential and the thickness of the depletion layer are related by [22]:

$$V_{\rm bias} = \frac{q \ d^2 \ |N_{\rm effective}|}{2\epsilon_{\rm Si}} \tag{3}$$

where  $N_{\text{effective}}$  is the effective charge carrier density, the number of (negative) donors minus the number of (positive) acceptors, and q is the absolute value of the electron charge.

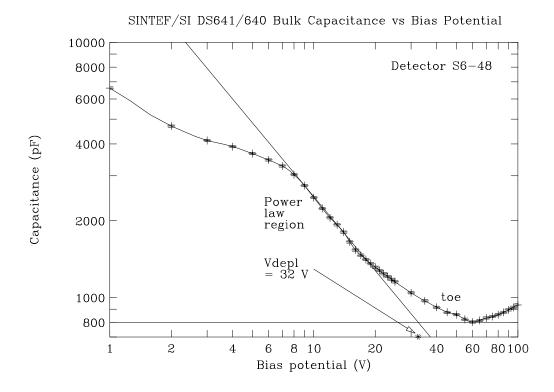

The depletion voltage,  $V_{\text{depl}}$ , is extracted from a plot of  $\log \{C_{\text{bulk}}\}\ vs.$   $\log \{V_{\text{bias}}\}$ . Below  $V_{\text{depl}}$  this curve falls proportionally to a power of the voltage,  $aV^n$ , as may be seen by inserting Equation 3 into Equation 2. The capacitance per unit area,  $C_{\text{bulk}}$ , is then given by:

where  $d_{\text{depl}}$  is the full depletion depth of the device.

The point of inflection in a  $\log\{C_{\text{bulk}}\}\ vs.$   $\log\{V_{\text{bias}}\}$  curve results from the transition from the upper line to the lower line in Equation 4 and thereby defines the depletion voltage,  $V_{\text{depl}}$ . To locate  $V_{\text{depl}}$ , first a line is drawn through the most steeply falling portion of the power-law region, as shown in Figure 5. A second, horizontal, line is drawn through the minimum of the approximately flat "toe" region as shown in the same figure. The intersection of the two lines defines the toe of the  $C_{\text{bulk}}\ vs.$   $V_{\text{bias}}$  curve. The V coordinate of this point is the depletion voltage.

In the case of a planar electrode diode, above  $V_{\rm depl}$  the curve is flat, owing to the uniform penetration of the electric field from the p-side electrode to the n-side electrode; the parallel plate capacitor model is a good approximation. In silicon microstrip detectors the onset of depletion is more gradual. This is due to periodic nonuniformities in the electric field around the n- and p-side implants. These regions of reduced electric field leave some of the silicon undepleted. Only by applying voltages beyond those sufficient to deplete a planar electrode diode of similar bulk geometry are these remaining regions depleted. Thus, the conventional intersection method provides an underestimate of depletion voltage when applied to silicon microstrip detectors. Full depletion is reached at voltages somewhat higher than those at which the  $\log \{C_{\rm bulk}\}$  vs.  $\log \{V_{\rm bias}\}$  curve begins to flatten. The size of this additional

voltage is affected by the structure of the electrodes and depends on the width-to-pitch ratio of the strips [13].

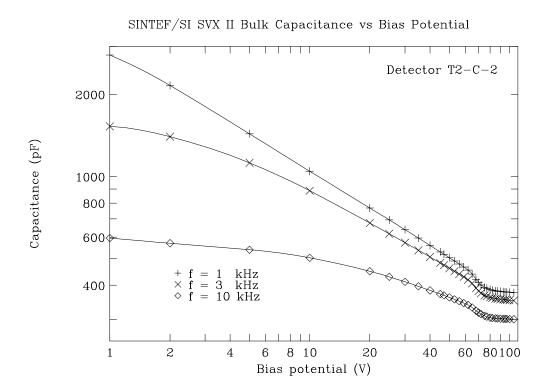

Figure 6 shows the frequency dependence of the curve shape of an unirradiated detector. The three curves presented yield a consistent depletion voltage, since they share a common V coordinate for their inflection points. Radiation induced effects on frequency dependence of  $C_{\text{bulk}}$  measurements have been reported in [23].

The capacitance between a single strip, the depleted bulk silicon, and the strips on the opposite side is called the backplane capacitance. It is denoted  $C_{\text{backplane}}^{i-\text{side}}$ , where i=n or p (see Figure 1). It may be approximated (edge effects are ignored) from  $C_{\text{bulk}}$  measured at full depletion voltage (or above) divided by the number of DC implant strips on the same side as the strip in question:

Typical backplane capacitances for unirradiated SINTEF/SI detectors are given in Table 6.

#### 4.4.2 PROCEDURE

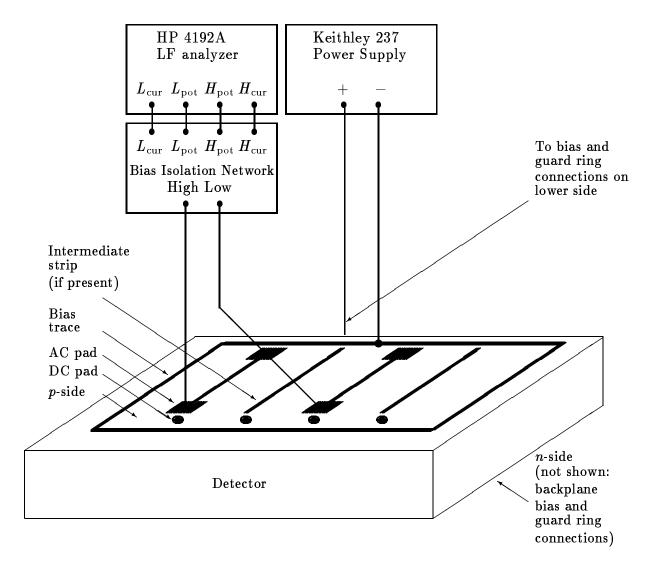

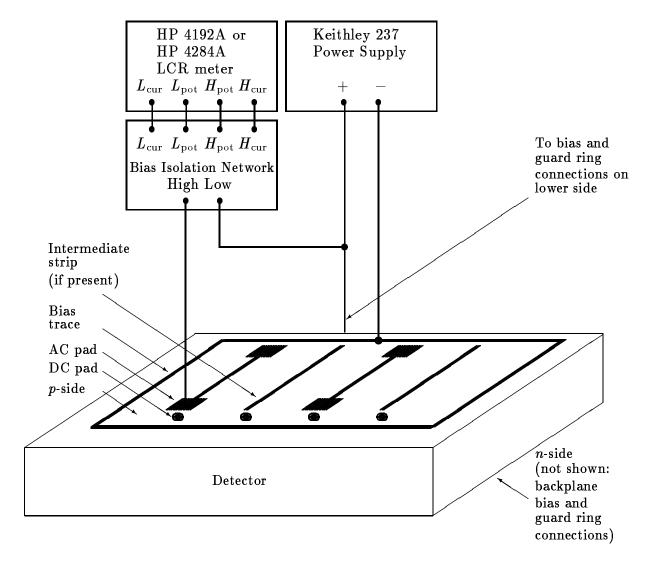

The arrangement for the depletion voltage measurement is depicted in Figure 7. The probe station and its micro-positioners are not shown for simplicity. The power supply, LCR meter, and bias isolation network (Appendix A.2.1) are shown. Low parasitic capacitance probes (Appendix A.2.2) are used to probe the upper surface <sup>5</sup> while the bias and guard ring contacts on the lower surface are made through the probing chuck (Appendix A.2.3). The effect of the probes, fixtures, and cables that intervene between the detector and the device under test are compensated for by the calibration procedures described in Appendix B.2.

The lower surface of the detector has its bias and guard rings contacted using the underside probing fixture or conductive rubber. The bias and guard rings on the *n*- and *p*-sides of the detector are connected to their respective terminals on the power supply through the bias isolation network.

Capacitance is recorded as a function of bias voltage in steps of a few volts while the capacitance decreases to a minimum value. The bias voltage steps are chosen to provide good fits through the most steeply falling portion of the power law region and above the toe of the  $C_{\rm bulk}\ vs.\ V_{\rm bias}$  curve. These are set in software. Data taking is complete when the measured capacitance falls to a constant value or microdischarge noise makes further capacitance determination impossible.

The slope of the line through the most steeply falling portion of the power law region may be found by a  $\chi^2$  minimization offline or graphically. Similarly, the intersection of this line and the horizontal line through the region above the toe may be found algebraically or graphically.

<sup>&</sup>lt;sup>5</sup>This is for convenience of making connections. The  $V_{\rm depl}$  measurement is relatively insensitive to systematic errors in measured capacitance as described in Section 4.4.3.

|            |                 | ,                | $C_{ m bulk}$   | . 7.7\            |                  | $C_{ m backplar}^{p-{ m side}}$ |                   |                   | $C_{\mathrm{backplar}}^{n-\mathrm{side}}$ |                   |

|------------|-----------------|------------------|-----------------|-------------------|------------------|---------------------------------|-------------------|-------------------|-------------------------------------------|-------------------|

| Designator | $\mathbf{Name}$ | \ <del>-</del>   | F @ 100         | ,                 |                  | /cm @ 1                         | ,                 | `                 | /cm @ 1                                   | •                 |

|            |                 | $1 \mathrm{kHz}$ | $3\mathrm{kHz}$ | $10 \mathrm{kHz}$ | $1 \mathrm{kHz}$ | $3 \mathrm{kHz}$                | $10 \mathrm{kHz}$ | $1  \mathrm{kHz}$ | $3 \mathrm{kHz}$                          | $10 \mathrm{kHz}$ |

|            |                 |                  |                 | Single-I          | Metal            |                                 |                   |                   |                                           |                   |

| SI-A-SM    | KB51-1          | 307              | 3 02            | 295               | 0.10             | 0.10                            | 0.09              | 0.40              | 0.40                                      | 0.39              |

| SI-B-SM    | SVX2-B-6        | 312              | 299             | 302               | 0.20             | 0.19                            | 0.19              | 0.41              | 0.39                                      | 0.41              |

| SI-C-SM    | SVX2-C-32       | 419              | 408             | 364               | 0.20             | 0.19                            | 0.17              | 0.31              | 0.31                                      | 0.27              |

| SI-D-SM    | SVX2-D-4        | 382              | 379             | 361               | 0.18             | 0.18                            | 0.17              | 0.58              | 0.57                                      | 0.55              |

|            |                 |                  |                 | Double-           | Metal            |                                 |                   |                   |                                           |                   |

| SI-A-DM    | KB54-1          | 283              | 279             | 273               | 0.09             | 0.09                            | 0.09              | 0.37              | 0.36                                      | 0.36              |

| SI-B-DM    | KB54-2          | 312              | 299             | 302               | 0.20             | 0.19                            | 0.19              | 0.41              | 0.39                                      | 0.39              |

| SI-C-DM    | LB54-1          | 365              | 3 49            | 315               | 0.17             | 0.17                            | 0.15              | 0.27              | 0.26                                      | 0.24              |

| SI-D-DM    | LB54-2          | 388              | 363             | 340               | 0.18             | 0.17                            | 0.16              | 0.58              | 0.55                                      | 0.51              |

| DS641/640  | S6-29           | 935              | _               | 146               | 0.13             | _                               | 0.02              | 0.47              | _                                         | 0.07              |

Table 6: Backplane capacitance for unirradiated SINTEF/SI detectors.

#### 4.4.3 ESTIMATE OF DEPLETION VOLTAGE UNCERTAINTY

A listing of several sources of systematic errors in the  $V_{\rm depl}$  measurement is given in Table 7.

Typical  $C_{\rm bulk}$  vs.  $V_{\rm bias}$  curves are shown in Figures 5 and 6. As the detector is depleted, the device capacitance drops from thousands to hundreds of pF. The uncertainties associated with the determination of the capacitance ( $\sigma_{\rm HP}$   $_{4284A}$ ,  $\sigma_{\rm LCR}$   $_{\rm cable}$ , and  $\sigma_{\rm LCR}$   $_{\rm cal}$ ) are relatively small. Further, they are all independent of bias voltage, since the LCR meter is isolated from the bias supply by the bias isolation network. Thus, any contribution to the log  $\{C_{\rm bulk}\}$  vs. log  $\{V_{\rm bias}\}$  plot will be a systematic vertical shift of the entire curve. Since  $V_{\rm depl}$  is determined from the point of inflection in this curve, not from the absolute value of the capacitance, these effects contribute negligibly. The contribution is not zero due to the logarithmic capacitance scale which will affect the slope, and therefore the point of intersection with the horizontal region, in the event of an overall, additive, shift in capacitance.

The dominant error comes from the fitting,  $\sigma_{\rm fit}=\pm~1~V.$

#### 4.5 P-SIDE MEASUREMENTS

Measurements of coupling capacitance, interstrip capacitance, and total capacitance with respect to ground are presented. These results are shown to be consistent with simulation. (Interstrip capacitance measurements must be made with LCR meters with floating return connections; this requirement is discussed in Appendix A.3.)

Figure 5: Example of a bulk capacitance versus bias potential measurement used to determine depletion voltage of a SINTEF/SI DS641/640 detector, S6-48. The measurement signal is 500 Hz at 1 V.  $V_{\rm depl}$  is determined from the intersection of the line drawn through the power law region and a horizontal line drawn through the minimum above the toe. See Section 4.4 for a discussion of the details of the shape of the curve.

Table 7:  $V_{\text{depl}}$  uncertainty contributions.

| Source                      | Magnitude                |

|-----------------------------|--------------------------|

| $\sigma_V^{ m fit}$         | $\pm~1	ext{V}$           |

| $\sigma_C^{ m cable\ loss}$ | $\pm~10^{-4}~\mathrm{V}$ |

| $\sigma_V^{	ext{K237}}$     | $\pm~0.033~\mathrm{V}$   |

| $\sigma_C^{ m HP~4284A}$    | $\pm~0.3\%$              |

| $\sigma_C^{ m HP~4192A}$    | $\pm~0.5\%$              |

| $\sigma_C^{ m LCR\ cable}$  | $\pm~1~p{ m F}$          |

| $\sigma_C^{ m LCR~cal}$     | $\pm~0.01~p{ m F}$       |

Figure 6: Example of a bulk capacitance versus bias potential measurement used to determine depletion voltage for a SINTEF/SI SVX II type C detector, T2-C-2. The frequency dependence of the capacitance has a negligible effect on the determination of the depletion voltage (prior to irradiation [23]). See Section 4.4 for a discussion of the details of the shape of the curve.

Figure 7: Depletion voltage measurement arrangement. The detector and probes remain in darkness during the measurement. The meter and power supply are computer—controlled via an IEEE488 bus. The meter's AC test signal and the (positive) bias potential are carried by the "High" terminal of the bias isolation network, while the return AC signal is delivered to the meter and the return bias potential to its "Low" potential terminal. The guard ring connections (not shown) are tied to the bias traces on their respective sides. (For the case of detectors with split traces for independent biasing of the even- and odd-numbered strips, two probes are required to contact these, and a third probe for the guard ring. All three probes are then tied to the appropriate terminal of the power supply. A similar arrangement is made for the opposite side. For simplicity, only one connection is shown in the figure.) The bias isolation network is illustrated in Figure 16. The meter and power supply are isolated according to a protocol described in Appendix A.3. See Section 4.4. This figure is based on a figure from Reference [24].

#### 4.5.1 COUPLING CAPACITANCE

The capacitance between the AC metal read-out strip and the  $p^+$  DC implant strip isolates the bias voltage and leakage currents from the front-end of the read-out chip. In terms of the overall total capacitance with respect to ground, the coupling capacitor couples the AC and DC components of the interstrip capacitance (Section 4.5.2) and allows both components to be measured by probing adjoining AC strips. This coupling is frequency dependent; therefore, it is important to understand the coupling capacitance in the context of the overall total capacitance measurement. As such, this capacitance is a factor in the total capacitance with respect to ground presented to the front-end amplifier and therefore affects the reflected equivalent noise charge of the chip. This capacitance also couples the charge in the DC implant strip to the read-out chip. Thus, the coupling capacitance impacts both the numerator and denominator of the signal-to-noise ratio.

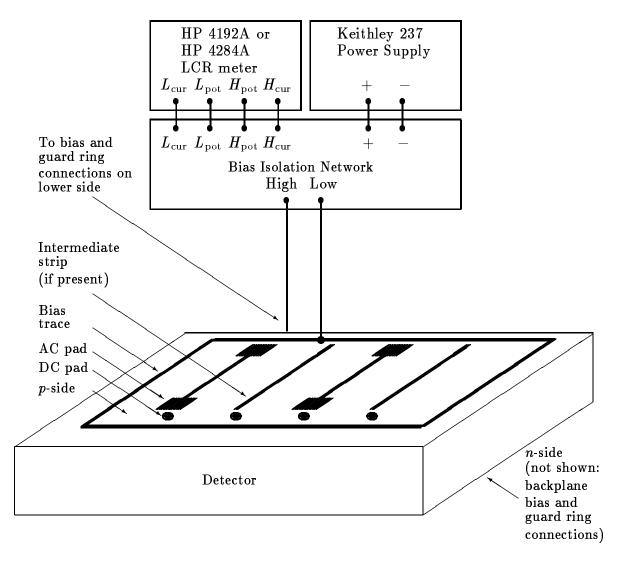

The coupling capacitance is measured with much of the same equipment and many of the same procedures used for the depletion voltage measurement (Section 4.4). Using the double-sided detector probing chuck as illustrated schematically in Figure 8, the detector is biased and isolated. Two low parasitic capacitance probe tips are attached through the bias isolation network to the HP 4192A or 4284A meter. These probes are placed on the DC and AC pads of the strip under test. (In the case of the HP 4284A, the high potential probe – isolated by the capacitance in the bias isolation network – is landed on the DC pad to prevent shorting the detector bias through the LCR meter. The low potential probe, HP 4192A or HP 4284A signal ground, contacts the AC strip.)

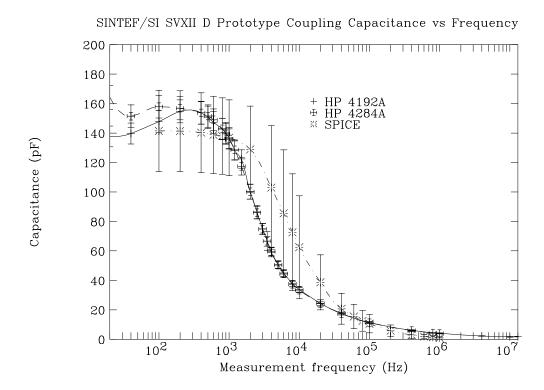

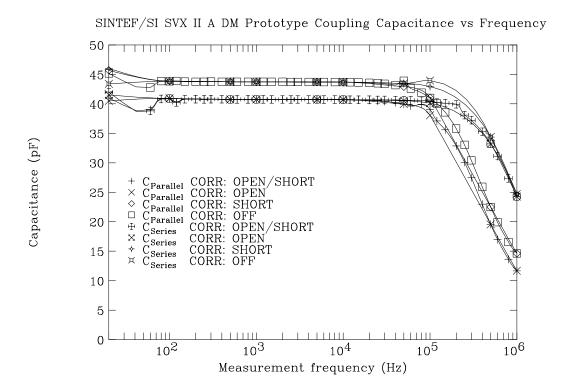

The coupling capacitance (assuming a parallel equivalent measurement circuit,  $C_{\rm parallel}$ , which the LCR meter uses to model the detector under test) <sup>6</sup> and the dissipation factor  $D^{7}$  are recorded either automatically, using the IEEE488 bus and host computer, or manually. A logarithmic frequency sweep of between 6 and 48 points from 20 Hz to 1 MHz is made for each new detector type. A typical curve is shown in Figure 9. A flat region of the  $C_{\rm coupling}\,vs$  frequency plot is identified. Subsequent coupling capacitance measurements are made at a frequency well within the flat region. For the coupling capacitance measurements described in this paper, a frequency of 500 Hz was used.

An investigation of systematic uncertainties associated with measurements of coupling capacitance for the p-side of SINTEF/SI SVX II detectors is given in Section 4.7.2.

$<sup>^6</sup>$ The LCR meter also supports a series model ( $C_{\rm series}$ ). For the measurements discussed in this paper, the parallel model was used. The difference between the two models is negligible for the measurements described here. This is shown in Figure 15.

<sup>&</sup>lt;sup>7</sup>The dissipation factor D (= 1/Q where Q is the "quality factor") is a measure of the nonideality of the capacitor under test, i.e., its resistance. A perfect capacitor would have D=0. D is an input to the determination of the basic accuracy of the LCR meter. The HP 4284A basic accuracy is guaranteed only for  $|D| \leq 0.1$ .

Figure 8: p-side coupling capacitance measurement arrangement. The guard ring connections (not shown) are tied to the bias traces on their respective sides. The bias isolation network is illustrated in Figure 16. The meter and power supply are isolated according to a protocol described in Appendix A.3. See Section 4.5.1. This figure is based on a figure from Reference [24].

Figure 9: Coupling capacitance versus measurement frequency for the *p*-side of the SIN-TEF/SI SVX II prototype type D detector. Measurements using the HP 4192A Low Frequency Impedance Analyzer and the HP 4284A Precision LCR meter are shown. Results of a SPICE simulation are included.

#### 4.5.2 Interstrip Capacitance

The interstrip capacitance is the dominant component of the total capacitance with respect to ground. The larger the ratio of interstrip to coupling capacitance, the more of the signal is coupled away to neighboring strips instead of to the front—end amplifier. This reduces the signal and thus lowers the signal—to—noise ratio as well. For these reasons, it is desirable to minimize the interstrip capacitance.

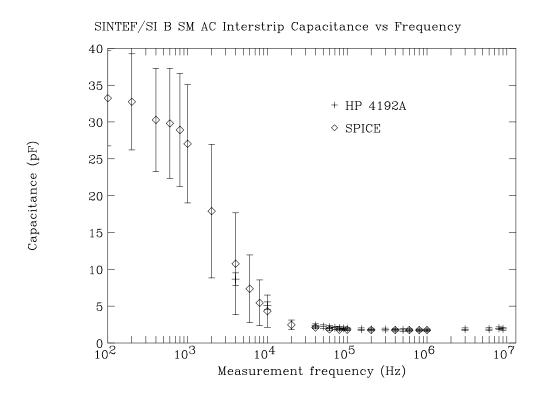

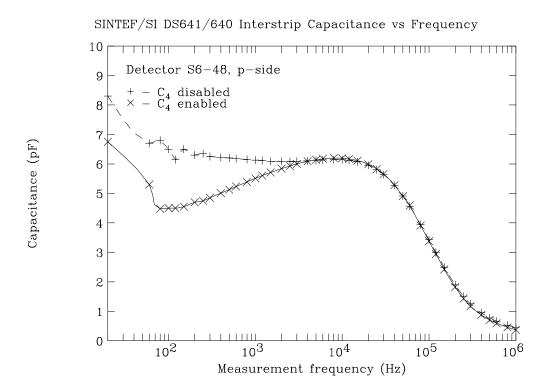

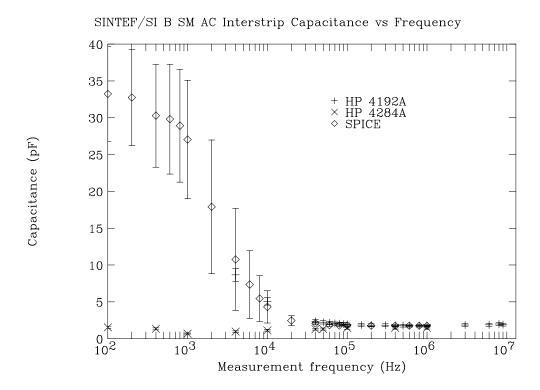

The measurement arrangement is shown in Figure 10. Neighboring strips are floated. We chose 1 MHz as the reference measurement frequency for the following reason: interstrip capacitance is composed of two components,  $C_{\rm interstrip}^{\rm AC}$  and  $C_{\rm interstrip}^{\rm DC}$ , reflecting the capacitance between adjacent AC metal strips and the capacitance between adjacent implants, respectively. (See Figure 1.) These components are coupled by the coupling capacitor. At sufficiently high frequencies (above the toe in the graph shown in Figure 11), the coupling capacitors act as AC shorts (as may be seen by inspection of Figure 9), and a measurement of the  $C_{\rm interstrip}^{\rm AC}$  component includes the  $C_{\rm interstrip}^{\rm DC}$  component (and any cross couplings between the AC metal strip and its neighboring DC implant). The calibration procedure is described in Appendix B.2.

We have investigated the effect of probing next-to-nearest neighbor strips by leaving one floating strip between two probed strips, repeating with two floating strips in between, then three strips, and so on. We estimate on this basis that the sum of all neighboring strips raises the overall interstrip capacitance by approximately 10 percent over that provided by nearest neighbors alone.

Interstrip capacitance is sensitive to the ground reference of the measuring device. As discussed in Appendix A.3, a meter with fully floating inputs must be used to obtain meaningful results over a wide frequency range.

#### 4.5.3 P-SIDE SINGLE AC STRIP CAPACITANCE WITH RESPECT TO GROUND

The direct measurement of the total capacitance presented to the front-end electronics is, of the measurements described in this paper, the most sensitive to the effects of ground loops, isolation, and probe contact quality. (See Appendices A.3 and B.5 for more on these topics.)

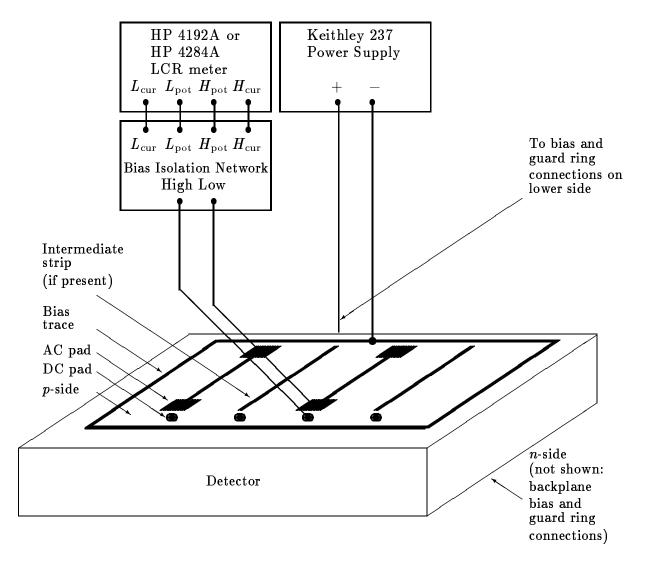

The probe placement and electrical connections are shown in Figure 12. Only a single probe is used, connected to the high potential terminals of the LCR meter. The LCR meter's  $L_{\rm cur}$  and  $L_{\rm pot}$  inputs are tied to the power supply terminals connected to the bias and guard rings on the underside of the sensor. The full operating potential is applied to the underside (n-side) of the sensor. The upper surface (p-side) is grounded.

With this connection scheme, the residual capacitance between the LCR meter's front panel and the device under test is approximately  $0.5~p\mathrm{F}$  more than for coupling and interstrip capacitance. Accordingly, a modified calibration protocol is called for. This protocol is

Figure 10: p-side AC interstrip capacitance measurement arrangement. For DC interstrip capacitance measurements, adjacent DC pads are probed. The guard ring connections (not shown) are tied to the bias traces on their respective sides. The bias isolation network is illustrated in Figure 16. The meter and power supply are isolated according to a protocol described in Appendix A.3. See Section 4.5.2.

Figure 11: Interstrip capacitance versus measurement frequency for the p-side of a detector. The backplane contribution,  $C_{\rm backplane}^{p-{

m side}}$ , is included in this measurement.

described in Appendix B.2.

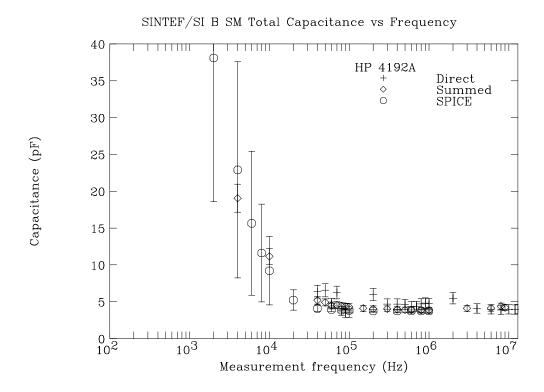

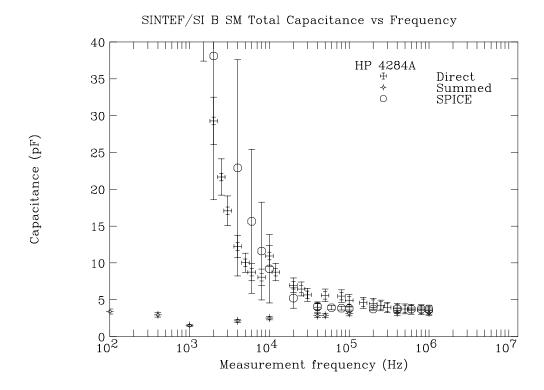

The measured total capacitance with respect to ground is shown in Figures 13 and 14 for the HP 4192A and HP 4284A respectively. In each figure, two measurements and a simulation of a SINTEF/SI type B detector are presented: a direct measurement; a summed measurement, derived from interstrip capacitance measurements made with the same meter; and a SPICE simulation.

The summed measurements are derived from the interstrip capacitance measurements (Section 4.5.2) by multiplying the interstrip result by two, to include neighbors on both sides of the strips, and by 1.1, to account for non-nearest neighbor strips, for a total multiplicative factor of 2.2. The interstrip measurement already contains the backplane contribution to the total capacitance. The summed measurement derived from the HP 4284A meter is inconsistent with the other four curves at low frequencies. This effect is due to the loss of return AC signal when this meter is used for this measurement. This effect is discussed in Appendix A.3.

#### 4.6 N-SIDE (DOUBLE-METAL) MEASUREMENTS

Measurements of the capacitance between DC implant strips  $(C_{\rm interstrip}^{\rm DC})$ , the interstrip capacitance between the first-metal AC strips  $(C_{11})$ , the overlap capacitance between the first-metal layer and the second-metal layer  $(C_{12})$ , and the interstrip capacitance between second-metal layer strips  $(C_{22})$  on the *n*-side of a double-metal detector require use of a capacitance meter that supports fully isolated  $L_{\rm cur}$ ,  $L_{\rm pot}$ ,  $H_{\rm cur}$ , and  $H_{\rm pot}$  inputs. Otherwise, the meter introduces an additional AC path for its return test signal to the power supply ground, which results in falsely low capacitance readings. This effect has been modeled in a SPICE simulation and is discussed in Appendix A.3. Accordingly, these measurements are beyond the scope of this paper. However, the net effect of these additional capacitances can be seen by comparing the total capacitance with respect to ground for the single-metal and double-metal cases. This is shown in Table 9.

#### 4.6.1 COUPLING CAPACITANCE

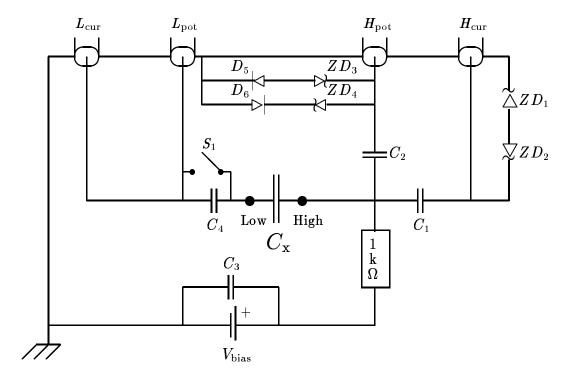

On double-metal detectors, the AC and DC pads are located on adjacent edges of the sensor, instead of along one side. Thus the probe placement differs slightly from the p-side case. Otherwise, the n-side coupling capacitance measurement is performed in a manner identical to that used for the p-side (Section 4.5.1). Figure 15 indicates a typical n-side coupling capacitance measurement.

#### 4.6.2 Interstrip and Overlap Capacitance

Interstrip and overlap capacitance measurements require use of a capacitance meter that supports fully isolated inputs and are outside the scope of the present paper. A scheme to

Figure 12: p-side total capacitance measurement arrangement. The guard ring connections (not shown) are tied to the bias traces on their respective sides. The bias isolation network is illustrated in Figure 16.

Figure 13: Total capacitance versus measurement frequency for the p-side of the SINTEF/SI SVX II prototype type B detector. See Section 4.5.3. Two curves are presented for the HP 4192A Low Frequency Impedance Analyzer; one represents a direct measurement and the other represents a summed measurement, derived from interstrip capacitance measurements (Section 4.5.2). The data presented have had the contributions due the cabling and probes intervening between the meter and detector subtracted. A SPICE simulation is also plotted. Note that in the summed case the HP 4192A (diamond symbol) and SPICE simulation (octagon) are consistent above 10<sup>3</sup> Hz. Compare with similar curves for the HP 4284A Precision LCR meter in Figure 14.

Figure 14: Total capacitance versus measurement frequency for the p-side of the SINTEF/SI SVX II prototype type B detector. See Section 4.5.3. Two curves are presented for the HP 4284A Precision LCR meter; one represents a direct measurement and the other represents a summed measurement, derived from interstrip capacitance measurements (Section 4.5.2). The data presented have had the contributions due the cabling and probes intervening between the meter and detector subtracted. A SPICE simulation is also plotted. Note that in the summed case the HP 4284A ("fancy diamond" symbol) and SPICE simulation (octagon) approach consistency only above 10<sup>5</sup> Hz. This effect is discussed in Appendix A.3. Compare with similar curves for the HP 4192A Low Frequency Impedance Analyzer in Figure 13.

Figure 15: Coupling capacitance versus measurement frequency for the n-side of the SIN-TEF/SI SVX II prototype type A detector. No errors are shown. The various measurement options of the HP 4284A LCR meter are shown. These include the modeling of parasitic capacitances as being in parallel or in series with the device under test, and the use of several calibration modes (CORR:), including no calibration (OFF), OPEN, SHORT or both (OPEN/SHORT). The two families of curves are separated by 3 pF in the flat region. This is the amount applied by the OPEN calibration of the HP 4284A Precision LCR Meter to correct for the residual capacitance of the 2 meter extension (HP 16048D), bias isolation network, fixturing, and probe tips. Similar corrections apply for other measurements. The calibration procedure is discussed in Appendix B.2.

make such measurements is described in Section 7.

#### 4.6.3 N-SIDE SINGLE AC STRIP CAPACITANCE WITH RESPECT TO GROUND

The total capacitance with respect to ground on the n-side is measured in the same manner as on the p-side, detailed in Section 4.5.3.

#### 4.7 ESTIMATE OF CAPACITANCE UNCERTAINTY

#### 4.7.1 Systematic Errors

The coupling, interstrip, and direct total capacitance measurements share many of the same sources of systematic error. The overall error assigned to the direct and interstrip measurements is 10 percent. The coupling capacitance, which is an order of magnitude larger, is assigned a five percent systematic uncertainty. The direct method of measuring total capacitance is preferred to the summed method where a straightforward quadrature sum of the component errors would exceed that of the direct measurement. Sources considered in making this estimate are listed in Table 8 and discussed below.

Table 8: Measured capacitance uncertainty contributions.

| Source                      | Magnitude            |

|-----------------------------|----------------------|

| $\sigma_C^{ m fixturing}$   | $\pm~0.5~p{ m F}$    |

| $\sigma_C^{ m cable\ loss}$ | $\pm~10^{-4}~{ m V}$ |

| $\sigma_C^{ m HP~4284A}$    | $\pm~0.3\%$          |

| $\sigma_C^{ m HP~4192A}$    | $\pm~0.5\%$          |

| $\sigma_C^{ m LCR~cable}$   | $\pm~1~p{ m F}$      |

| $\sigma_C^{ m LCR~cal}$     | $\pm~0.01~p{ m F}$   |

The principle difference between this and Table 7, where the contributions to depletion voltage uncertainty are listed, is in the contribution of the intervening cabling and fixturing,  $\sigma_C^{\rm fixturing} = \pm~0.5~p{\rm F}$ . This is the dominant term. Unlike the case of depletion voltage (Section 4.4.3), where absolute errors in measured capacitance do not affect determination of the point of inflection of the C~vs.~V curve, here the capacitance intervening between the meter and the device under test must be compensated. As mentioned previously, this additional capacitance is on the order of 2.5 to 3.0 pF before OPEN/SHORT correction (HP 4284A) or pedestal subtraction (HP 4192A). After this correction, the meter routinely reads less than  $\pm~0.1~p{\rm F}$  (often less than  $\pm~0.001~p{\rm F}$ ) when the probes are raised. Thus, the quoted uncertainty represents a conservative estimate.

A systematic effect seen in measurements of the p-side coupling capacitance of SINTEF/SI SVX II prototype detectors is discussed separately in Section 4.7.2.

# 4.7.2 Nonuniformities in p-side Coupling Capacitance for SINTEF/SI SVX II PROTOTYPES

The p-side coupling capacitance versus frequency for a typical detector is shown in Figure 9. The coupling capacitance for 24 unirradiated SINTEF/SI SVX II prototype detectors taken at a measurement frequency of 500 Hz is shown in Figures 12a and 12b of [25]. Each data point represents an average over five strips distributed uniformly over the surface of the detector. The error bars are determined from the standard deviation of the average. Many of these p-side measurements exhibit substantial nonuniformities across the surface of the detector as reflected in the large standard deviations; as great as ten times those of similar n-side (ibid., Figures 11a and 11b) measurements (see Section 4.6.1) of both single-metal and double-metal detectors.

These large standard deviations are not explainable in terms of processing variations affecting strip width, strip thickness, implant width, implant depth, dielectric thickness, etc., both according to the manufacturer [26] and normal variations input to a SPICE simulation (see Section 3). Several possible causes were investigated.