# STABILITY RESEARCH PROGRESS ON HIGH-POWER PULSE MODU-LATOR FOR SXFEL-UF\*

Q.B. Yuan<sup>1,2†</sup>, Y.F. Liu<sup>1,2,3</sup>, Y.H. Wu<sup>1,2</sup>, M. Gu<sup>1,2</sup>, J. Tong<sup>1,2,3</sup>

<sup>1,2</sup>Shanghai Institute of Applied Physics, Chinese Academy of Sciences, Shanghai, China <sup>1,2</sup>Shanghai Advanced Research Institute, Chinese Academy of Sciences, Shanghai, China <sup>3</sup>also at University of Chinese Academy of Sciences, Beijing, China

10th Int. Partile Accelerator Conf.

1SBN: 978-3-95450-208-0

STABILITY RESEARCH PROGRES

LATOR FOR

Q.B. Yuan<sup>1,2†</sup>, Y.F. Liu<sup>1,2,3</sup>, Y.

1,2 Shanghai Institute of Applied Physics, Ch

1,2 Shanghai Advanced Research Institute, Cl

3 also at University of Chinese Ac

SXFEL-UF (Shanghai Soft X-ray Free Electron Laser

User Facility) under construction presently demands

higher energy stability. Stability of pulse modulator feedhigher energy stability. Stability of pulse modulator feed-2 ing power for klystron plays an utmost important role in E energy stability and occupy dominant factors in bringing influences in stability of RF power. Currently, stability of high-power pulse modulator of LINAC (Linear Accelerator) is on the level of 0.1% to 0.05% usually. In order to meet the higher stability requirements, it is very necessary for close-loop feedback control techniques instead of traditional open-loop to be applied in the modulator design. The stability controller adopts double control-loops # techniques which feedback signals are respectively from FFN (Pulse Forming Network) and pulse transformer in a oil tank. In addition, the paper also introduces recent ਰ progress on high stable CCPS research (Capacitor Charging Power Supply), which brings direct impact on the stability of modulator. In comparison with the former close-loop design, high stable CCPS design takes the overall modulator stability into full consideration. And the feedback control algorithm utilized to output PWMs (Pulse Width Modulations) for full bridge switches is implemented in the CCPS controller directly rather than modulator controller independent of CCPS. It is expected feasibly to obtain 0.01% stability by taking the above measures.

#### INTRODUCTION

SXFEL-UF is an X-ray Free Electron Laser (XFEL) User Facility with 1.6 GeV under tense construction [1], which has been developed on the basis of SXFELty). In order to obtain more excellent beam quality, microwave system is requested to col. plitude stability and more tight tolerances of phase jitter (0.01% rms). Through beam switch yard, SXFEL-UF would transfer beam to one SBP line with ten sets of invacuum undulators and another undulator line with two vacuum undulators and anomer undulators and sets of U80s, four sets of U40s, one set of U55, ten sets of ∠ U235s and two sets of EPU30s.

However, on the current high power modulator technical condition, it is very difficult and challenging for us Initial condition, it is very difficult and challenging for us to enhance either pulse-to-pulse amplitude stability or ripple within pulse (flatness of flat top) especially to 0.01% level. Thus, whether could LLRF (Low-level RF)

THPRB042

control techniques of microwave system compensate deficiency resulting from unsatisfactory modulator performance? LLRF can accomplish controlling stability of amplitude and phase of RF to some certain level, but which to what extent mostly depends on amplitude stability level of pulsed modulator.

As mentioned in abstract, the performance of the CCPS applied in modulator exactly take up absolutely important factors in modulator's stability [2]. Presently, commercial CCPS products universally adopt analog PWM control techniques and close-loop feedback within internal CCPS. It is not enough for the CCPS only utilizes close-loop with feedback from internal CCPS, feedback from outside CCPS is also indispensible.

This paper would firstly present some current experimental results through adopting close-loop control technology on the basis of routine commercial CCPS. Then recent in-house research progress and design about high repeatable stability are introduced.

### STABILITY CONTROL

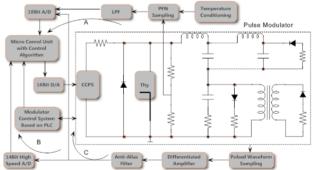

Stability feedback control adopts three kinds of control routes (Figure 1), which are respectively high precision

Figure 1: Stability feedback control schematic for pulse modulator.

sampling of PFN voltages from HV divider(route A), high precision sampling of pulsed waveform through capacitor networks and differentiated amplifier(route C) and highspeed sampling with multi-datum average of pulsed waveform through capacitor networks and differentiated amplifier (route B) [3]. The HV divider is a resistor network with high precision and low temperature drift, which is immersed in a oil cylinder with a ratio 10000:1. The LPF is one 5-order active low pass filter with the cutoff frequency 5kHz. The micro-control unit (based on FPGA) acquires data from the 18-bit A/D (600 kHz sampling rate) and 14-bit high-speed A/D (60 MHz sampling rate) through parallel connections with each other.

<sup>\*</sup> Work supported by the National Natural Science Foundation of China (NO.11675250).

<sup>†</sup> yuanqibing@zjlab.org.cn

## PFN Sampling (Route A)

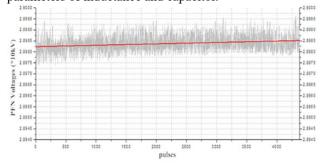

According to the acquisition datum of voltages of PFN by use of high precision resistor voltage divider, The controller regulates the D/A values through analog control interface between CCPS and FPGA system with the proportional integral (PI) algorithm. In order to draw a comparison between close-loop and open-loop control condition, two kinds of test results are respectively recorded and analysed (Figure 2 and Figure 3). Figure 2 demonstrates PFN voltages would drift under open-loop condition, and the centric values (the red curve) fluctuate 0.01% approximately due to heat drift of distribution parameters of inductance and capacitor.

Figure 2: Open-loop test results of PFN voltages.

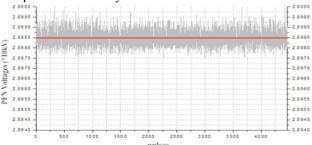

The analysis results measured on close-loop feedback control condition is illustrated in Figure 3, which indicates the centric values have no drift and are stabilized in a straight and horizontal line. Meanwhile, Figure 3 also manifests that although feedback control can restrain long-term drift, short-term fluctuation is hard to be accomplished effectively.

Figure 3: Close-loop test results of PFN voltages.

## Pulse Waveform Sampling (Route C)

The difference of pulsed waveform sampling control ring from PFN sampling feedback is that feedback signal is gained from capacitor voltage divider network of pulse transformer in oil tank. In consideration of high precision but low sampling A/D, on the one hand, one or two points of pulse is applied as characteristic value. On the other hand, one dedicated peak sampling-holding circuit is designed to prolong and extend the sampling point to about 1ms duration so that multiple datum could be acquired and disposed within one repetition period.

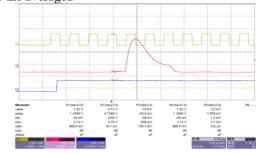

For one or two points sampling, FPGA system is equipped with one sampling synchronous signal. Thus FPGA system could delay a certain time-span to match the interesting and appropriated sampling points (Figure 4), where the klystron is exactly excited by the pulse modulator. For multiple points sampling, FPGA system uses the averaged

Figure 4: Sampling point of pulse waveform.

value as featured value, but delay modulation is carried out by the hardware.

The final control result is showed in Figure 5, and the pulse-to-pulse amplitude stability is 0.03%(rms).

Figure 5: Pulse-to-pulse amplitude stability test result.

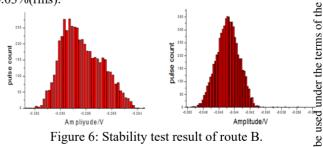

## Pulse Waveform Sampling (Route B)

In route C, although the resolution meets control requirement well, but the sampling points are not sufficient to represent the characteristic value of the pulse waveform. In the mean time, multiple sampling of route C has no apparent difference from one or two points sampling because of sampling extension. Thus, in order to acquire directly a variety of datum within one pulse period, high sampling A/D is put forward and applied [4]. The test result is showed in Figure 6, and stability is also about 0.03%(rms).

Figure 6: Stability test result of route B.

### HIGH STABLE CCPS DESIGN

Three different feedback control methods are discussed particularly in the above text, and the test results don't achieve the expected goal.

may l

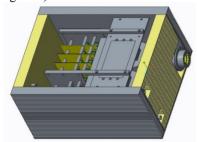

Resonant Charging CCPS

Actually, it is possible to obtain 0.01% amplitude stability, only on the condition that the CCPS stability is superior to 50 ppm or more less. That is to say, for a superior capacitance load, the charge quantity is 50 ppm or more less within one resonant charging period. At # the same time, the charging time must be also considered so as to satisfy the pulse modulator working frequency. Ul-timately, one high stable CCPS (50 kV@0.6 A) has been designed, which is equipped with two resonant highfrequency transformers in one crate, one is coarse charging transformer and another is fine charging transformer. The two oil-immersed transformers (OITs) are installed in a oil box (Figure 7).

Figure 7: Oil-immersed transformers for CCPS.

The switching frequency of the coarse charging under CCM (Continuous Conduction Mode) is 25 kHz (resonant frequency is 50 kHz). The switching frequency of the fine charging is 40 kHz (resonant frequency is 80 kHz). The characters of the OITs are as follows:

- Oil-immersed in aluminium shell with sealed struc-

- 2019). Output through dedicated high voltage electric out-

- Equipped four temperature sensors, installed respectively on oil level top, bottom, iron core and high voltage outlet.

- Equipped with two oil-level sensors.

- CC BY 3.0 licence (© Heat dissipation design with fold-structure and cooling water.

## Charging Simulation

The overall pulse modulator theoretical simulation has been completed by PSPICE, which is composed of full bridge circuit, resonant inductance and capacitor, power ട്ട് switches, transformer, and PFN.

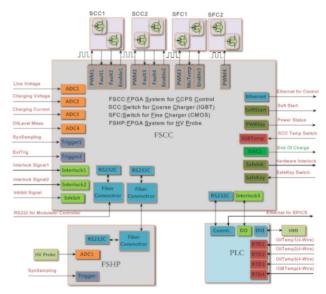

## Controller Design for CCPS

The control system for CCPS is mainly consisted of one FSCC (FPGA System for CCPS), one FSHP (FPGA System for HV Probe) and one PLC for HMI (Human Machine Interface) design and temperature acquisition Y (The Figure 8).

The main task for controller of CCPS is to implement Edigital PWMs control for double full-bridges circuits according to feedback PFN voltage through optical-fiber communication with FSHP. The CCPS controller also offers RS232 or Ethernet interface for dedicated modulator controller. In addition, direct EPICS control access is also available.

The safety interlock design is another consideration. In actual working condition, internal excess temperature due to insufficient heat dissipation may bring great damage to CCPS. These failures would make HV outlet destroyed and oil leaked from compact oil box. So liquid-level monitoring and temperature safety protection are designed in the controller.

Figure 8: Schematic diagram of CCPS controller.

#### **SUMMARY**

The jitter tolerance for SXFEL UF is very tight, accordingly high amplitude stable pulse modulator is also very imperative. Three different feedback control methods on the basis of conventional CCPS are applied and relevant test and experiment results show that short-term stability mainly depends on CCPS own stability. Presently in-house CCPS research and development has been carried out. The big difference with conventional CCPS is the feedback control is implemented in internal CCPS by use of digital PWMs for the control of full-bridges circuits. It is expected that 0.01% stability of pulse modulator would be achieved.

#### ACKNOWLEDGEMENTS

We would like to express sincerely our gratitude to all those who ever provide meaningful and valuable discussion and suggestion.

#### REFERENCES

- [1] Z. Zhao et al., "Status of the SXFEL Facility", Applied Sciences, 2017, 7(6): 607. doi:10.3390/app7060607

- [2] J. S. Oh, S. S. Park, Y. J. Han, et al., "Design Considerations for the Stability Improvement of Klystron-Modulator for PAL XFEL", in Proc. 21st Particle Accelerator Conf. (PAC'05), Knoxville, TN, USA, May 2005, paper RPAE009, pp. 1165-1167.

**MC7: Accelerator Technology T16 Pulsed Power Technology**  IPAC2019, Melbourne, Australia JACoW Publishing doi:10.18429/JACoW-IPAC2019-THPRB042

10th Int. Partile Accelerator Conf. ISBN: 978-3-95450-208-0

Content from this work may be used under the terms of the CC BY 3.0 licence (© 2019). Any distribution of this work must maintain attribution to the author(s), title of the work, publisher, and DOI

- [3] Y. Liu, M. Gu, Q. Yuan, L. Wang, "Designing signal conditioning circuit for stability control system of LINAC modula-tor", nuclear technology, 2013, vol. 36, issue 3. doi:http://ir.sinap.ac.cn/handle/331007/13523

- [4] L. Wang, M. Gu, Q. Yuan, "Data acquisition and processing in stability control system of LINAC modulator", nuclear technology, 2012, 35(7). doi:http://ir.sinap.ac.cn/handle/331007/12774