#### **OPEN ACCESS**

### Development of Low-Power Small-Area L-2L CMOS DACs for multichannel readout systems

To cite this article: D Przyborowski and M Idzik 2012 JINST 7 C01026

View the article online for updates and enhancements.

- <u>A power scalable 10-bit pipeline ADC for</u> <u>Luminosity Detector at ILC</u> M Idzik, K Swientek, T Fiutowski et al.

- Front end electronics for silicon strip detectors in 90nm CMOS technology: advantages and challenges J Kaplon and M Noy

- Wideband pulse amplifier with 8 GHz GBW product in a 0.35 m CMOS technology for the integrated camera of the Cherenkov Telescope Array D Gascon, A Sanuy, E Delagnes et al.

# IOP ebooks<sup>™</sup>

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research.

Start exploring the collection - download the first chapter of every title for free.

RECEIVED: November 15, 2011 ACCEPTED: December 9, 2011 PUBLISHED: January 5, 2012

TOPICAL WORKSHOP ON ELECTRONICS FOR PARTICLE PHYSICS 2011, 26–30 September 2011, VIENNA, AUSTRIA

## Development of Low-Power Small-Area L-2L CMOS DACs for multichannel readout systems

#### D. Przyborowski and M. Idzik

AGH University of Science and Technology, al. Mickiewicza 30, Cracow, Poland

*E-mail:* przyboro@agh.edu.pl

ABSTRACT: The design and measurements of 8-bit DACs based on L-2L ladder architecture are presented. The main design goals were low power consumption and low area. Such features are needed for DACs trimming parameters in each channel of a multichannel readout system. The PMOS and the NMOS based DACs are studied, for wide range of biasing conditions, in two operation modes — as a current generator and a current divider. The NMOS and PMOS prototypes occupying respectively 0.034 mm<sup>2</sup> and 0.043 mm<sup>2</sup> are fabricated in 0.35 $\mu$ m CMOS technology and tested. The measurements show full functionality with the maximum INL and DNL errors below 0.4 LSB. The measured DAC power consumption is about 80 $\mu$ W.

KEYWORDS: VLSI circuits; Analogue electronic circuits

<sup>&</sup>lt;sup>1</sup>Corresponding author.

#### Contents

| 1 | Introduction            |                                 |

|---|-------------------------|---------------------------------|

| 2 | L-2L DAC architecture   |                                 |

|   | 2.1                     | Binary weighting principle      |

|   | 2.2                     | Short channel effects           |

|   | 2.3                     | Mismatch effects                |

|   |                         | 2.3.1 Amplifier input offset    |

| 3 | L-2L DAC implementation |                                 |

|   | 3.1                     | Output amplifier                |

| 4 | Measurements results    |                                 |

|   | 4.1                     | Current generator mode          |

|   | 4.2                     | Current divider mode            |

|   | 4.3                     | DAC performance vs power supply |

| 5 | Summary                 |                                 |

#### **1** Introduction

In multichannel readout systems of high energy physics experiments digital to analog converters (DACs) are commonly used to control various parameters like discriminator threshold voltage or current/voltage bias. The systematic and the random mismatches of CMOS technologies force the use of trimming DACs to obtain a uniform channel to channel behavior in a multichannel ASIC. For these reasons a DAC with moderate (6–8 bits) resolution, a low power consumption and a small die area, is one of the basic building blocks requested in the multichannel readout system. The goal of this paper is to design 8-bit DACs conforming to these specifications.

In section 2, the operation principle of L-2L DAC, with a particular attention to mismatch and offset effects, is discussed. Section 3 describes the design of the proposed NMOS and PMOS based DACs. The measurements results are presented in section 4.

#### 2 L-2L DAC architecture

#### 2.1 Binary weighting principle

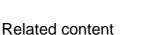

For any bias condition the drain current of MOS transistor is proportional to its width-to-length ratio. Based on this statement it can be shown that any series-parallel connection of identical transistors can be treated as one transistor with equivalent aspect ratio, as shown in figure 1. Since the main branches of circuit in figure 1 are equivalent the current is equally divided between the branches [1, 2].

1

3 4

6

Figure 1. Principle of current division and L-2L ladder design.

#### 2.2 Short channel effects

In modern deep submicron CMOS processes the *short channel effect* is an important factor which affects the drain current of MOSFETs. The most important short channel effect in designing L-2L ladder is the *carrier velocity saturation* (CVS). The effect becomes significant for devices with reduced channel length, for which the proportionality between carrier velocity and longitudinal electrical field vanishes (see expression (2.1)). To reduce this effect the device should work in deep linear region or should have long enough channel [2].

$$\mu_{sat} = \frac{\mu_0}{\sqrt{1 + \left(\frac{\mu_0 V_{DS}}{L v_{sat}}\right)^2}} \tag{2.1}$$

#### 2.3 Mismatch effects

The most important limitations of DAC resolution come from the mismatch effects. The mismatch is caused by the fluctuations of polysilicon shape, doping, or gate oxide thickness. Based on Pelgrom model [3, 4] the dispersion of transistor current can be written as:

• for saturation region

$$\sigma(I_d) = \sqrt{\frac{A_\beta^2}{W \cdot L} + \left(\frac{2 \cdot 100\% \cdot A_{V_{th}}}{V_{od}}\right)^2 \cdot \frac{1}{W \cdot L}},$$

(2.2)

• for linear region:

$$\sigma(I_d) = \sqrt{\frac{A_\beta^2}{W \cdot L} + \left(\frac{100\% \cdot A_{V_{th}}}{V_{od} - \frac{1}{2}V_{ds}}\right)^2 \cdot \frac{1}{W \cdot L} + \left(100\% \cdot \frac{\Delta V_{ds}}{V_{ds}}\right)^2},\tag{2.3}$$

where  $V_{od} = V_{gs} - V_{th}$  is overdrive voltage.

One can see that the main way to minimize transistor mismatch is to increase the device area and/or to increase the overdrive voltage. For the devices working in linear region any variance in drain-source voltage can also seriously deteriorate the performance of current division. For this reason any input offset of amplifier, setting the potential of drain/source node, can be a serious limitation of L-2L DAC resolution.

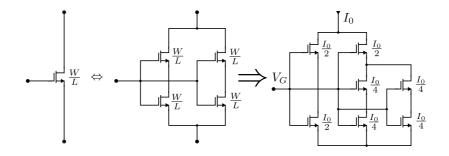

Figure 2. Circuit used in offset analysis.

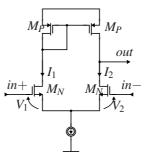

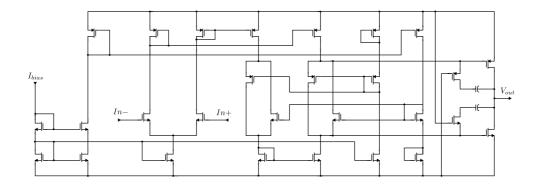

Figure 3. Schematic diagram of proposed DAC.

#### 2.3.1 Amplifier input offset

The input offset of differential amplifier (figure 2) has two components. The first one comes from threshold voltage mismatch in the input pair, while the second from current mismatch in the load. Using the Pelgrom mismatch model one can obtain following expression for the input offset of differential amplifier.

$$V_{offset} = V_{gs_1} - V_{gs_2} \approx \sqrt{\sigma_{V_{th_N}}^2 + \frac{I^2 \cdot \sigma_{I_P}^2}{gm_N^2} + \frac{V_{od_N}^2 \cdot \sigma_{\beta_N}^2}{4}}$$

(2.4)

For the minimum offset one would need a high transconductance of the input pair working with low overdrive voltage, and a large area of the load devices working with high overdrive voltage.

#### **3** L-2L DAC implementation

The proposed NMOS version of L-2L DAC core is shown in figure 3. A complementary circuit is implemented for the PMOS version. The proposed DAC is designed to test the L-2L architecture and can work in two different modes: as a current generator and a current divider. In the first mode the node  $I_{in}$  (see figure 3) is shorted to ground (or  $V_{dd}$  for PMOS version). For this mode the current generated by the ladder depends strongly on biasing conditions ( $V_{bias}$  in saturation region,  $V_{bias}$  and  $V_{ref}$  in linear region). The transistors  $M_c$  and  $M_d$  work as switches [5]. The default bias conditions are set in order to obtain the least significant bit (LSB) current equal 25 nA (LSB voltage step)

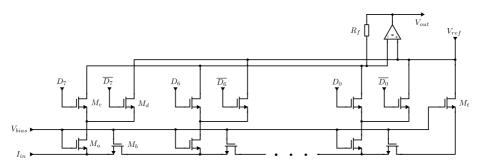

Figure 4. Schematic diagram of output amplifier.

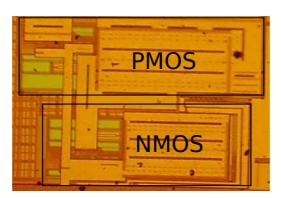

Figure 5. Micrograph of fabricated prototypes.

about 0.5 mV) what corresponds to  $V_{bias}$  about 1.2 V for the NMOS and 1.45 V for the PMOS ladder respectively. In the current divider mode the LSB current was fixed to constant value and the ladder linearity was investigated in different biasing conditions.

#### 3.1 Output amplifier

Due to the relatively high current generated by the L-2L ladder in the current generator mode at maximum gate potential ( $V_{bias} = V_{dd}$ ), a two stage class AB output amplifier was designed. The schematic diagram of the output amplifier is shown in figure 4. The first stage is based on an operational transconductance amplifier (OTA) while the second output stage uses the *floating current source* [6] bias. To ensure stability, a classical Miller compensation technique with nulling resistor is used. The simulated key parameters are: open loop gain 109 dB, gain-bandwidth product 2 MHz, input offset 2 mV, and noise rms 0.1 mV.

#### 4 Measurements results

The first prototypes of PMOS and NMOS DACs were fabricated in a two-poly four-metal 0.35  $\mu$ m CMOS technology. The dimensions of DAC cores are  $340 \times 125 \ \mu$ m<sup>2</sup> for the PMOS version and  $295 \times 116 \ \mu$ m<sup>2</sup> for the NMOS version respectively. The chip micrograph is shown in figure 5. The

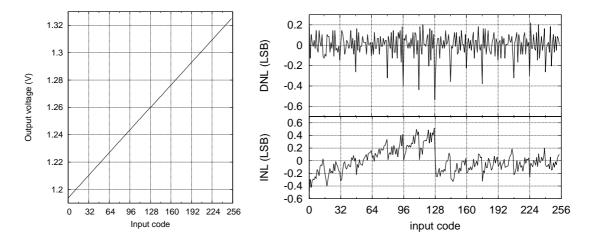

Figure 6. Nonlinearities of NMOS DAC at default biasing conditions.

measured DAC power consumption at default settings is around 80  $\mu$ W. It is similar for the NMOS and the PMOS version since it comes mainly from the output amplifier which consumes around 60  $\mu$ W. The DAC performance was verified over a wide range of biasing conditions in two modes of operation, as a current generator and current divider. Because of the foreseen DAC applications, only the static measurements of linearity were done. The Tektronix AWG2021 arbitrary waveform generator was used as pattern generator and the Agilent B1500 semiconductor analyzer to generate all bias potentials and to measure the DAC output voltage.

#### 4.1 Current generator mode

In this mode of operation four DACs were tested. In figure 6 the linearity measurements, i.e. the transfer curve and the INL, DNL errors, performed for the NMOS DAC, at default biasing conditions, are presented. It is seen that both INL and DNL stay within 0.5 LSB. The NMOS DAC linearity was verified over a wide range of biasing potentials and similar INL and DNL errors were obtained. The NMOS DAC works correctly for the gate potential  $V_{bias}$  in the range 1.2-2.8 V and for the  $V_{ref}$  in the range 1-2 V. The LSB value for these biasing conditions changes from 0.5 mV (for  $V_{bias} = 1.2V$ ) to 4.2 mV ( $V_{bias} = 2.8V$ ) which corresponds to the LSB current range 25-210 nA.

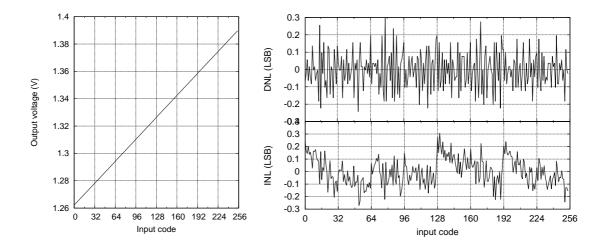

Similar measurements were performed for the PMOS DAC version. Typical linearity results obtained at default biasing conditions are shown in figure 7. The INL and DNL errors stay well within 0.5 LSB. The measurements were repeated changing the biasing conditions, i.e.  $V_{bias}$  in the range 0.1-1.4 V and  $V_{ref}$  from 0.5 to 2.5 V, and similar INL and DNL errors were obtained. The LSB step corresponding to these biasing conditions changes from 0.5 mV ( $V_{bias} = 1.5V$ ) to 2.2 mV ( $V_{bias} = 0.1V$ ). These values of LSB step correspond to currents in the range 25-110 nA.

#### 4.2 Current divider mode

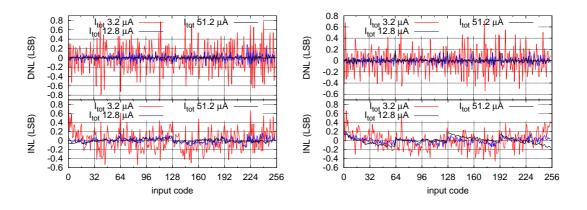

The performance of the prototype DACs was also verified in the current divider operation mode. The measurements were done both for the NMOS and the PMOS DAC, in the current range 12-200 nA per LSB. In figure 8 the nonlinearity errors obtained for the NMOS and the PMOS DAC are

Figure 7. Nonlinearities of PMOS DAC at default biasing conditions.

**Figure 8**. DAC nonlinearities in current divider mode for three value of divided current (NMOS — left, PMOS — right).

shown for different currents. It is seen that the maximum INL and DNL values are below 0.7 LSB and much lower in average.

#### 4.3 DAC performance vs power supply

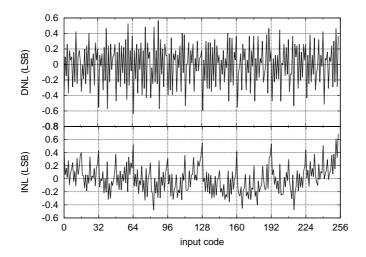

Lastly, the DAC performance was studied as a function of supply voltage. It was verified that the DACs sustain good linearity for supply voltage down to 1.7 V. Typical INL and DNL errors for NMOS DAC measured at 1.7 V supply voltage are shown in figure 9. In fact the only limitation (except the transistor threshold voltage) to scaling of supply voltage in this architecture, is the correct operating point of the output amplifier.

#### 5 Summary

Two general purpose low power (80  $\mu$ W) small size (~ 0.04 mm<sup>2</sup>) 8-bit L-2L DACs were designed, fabricated and tested. A very good linearity was found for the NMOS and the PMOS DAC version,

Figure 9. DAC nonlinearities for 1.7 V of supply voltage.

operating in two different operation modes, i.e. the current generator and the current divider mode. It confirms that the L-2L architecture is a very attractive choice for DACs in CMOS technologies. The obtained low power and area match well with DAC requirements in a multichannel readout system, where fine tuning of various parameters (e.g. thresholds) in every channel, is often needed. In the near future the developed circuits and architectures are foreseen to be implemented in such multichannel readout system.

#### Acknowledgments

This work was supported by the Polish Ministry of Science and Higher Education and its grants for Scientific Research.

#### References

- K. Bult and G.J.G.M. Geelen, An Inherently Linear and Compact MOST-Only Current Division Technique, IEEE J. Solid State Circ. 27 (1992) 1730.

- [2] H. Klimach, M. Scheider and C. Galup-Montoro, An M-2M digital-to-analog converter design methodology based on a physical mismatch model, IEEE Int. Symp. Circ. Sys. (2008) 2257, ISCAS 2008.

- [3] M.J.M. Pelgrom, A.C.J. Duinmaijer and A.P.G. Welbers, *Matching properties of MOS transistors*, *IEEE J. Solid State Circ.* **24** (1989) 1433.

- [4] J. Bastos, *Characterization of MOS transistor mismatch for analog design*, Ph. D. Thesis, Katholieke Universiteit Leuven (1998).

- [5] C.M. Hammerschmied, Q. Huang, *Design and implementation of an untrimmed MOSFET-only 10-bit A/D converter with -79 dB THD, IEEE J. Solid State Circ.* **33** (1998) 1148.

- [6] D.Monticelli, A quad CMOS single-supply op amp with rail-to-rail output swing, IEEE J. Solid State Circ. 21 (1986) 1026.