#### POLITECNICO DI MILANO

V Facoltà di Ingegneria Corso di laurea in Ingegneria Elettronica Dipartimento di Elettronica e Informazione

# STUDY OF ACQUISITION ELECTRONICS WITH A HIGH DYNAMIC RANGE FOR A BEAM LOSS MEASUREMENT SYSTEM

Relatore: Prof. Marco SAMPIETRO

Correlatori: Dr. Bernd DEHNING

Ing. Ewald EFFINGER

CERN, European Organization for Nuclear Research

Tesi di Laurea di:

Giuseppe Guido Venturini Matr. 681497

Anno Accademico 2007-2008

"Fundamentally, all writing is about the same thing; it's about dying, about the brief flicker of time we have here, and the frustration that it creates."

Mordecai Richler

"Try not to be so negative all the time.

Why don't you offer a little... constructive criticism?"

the Blues Brothers, while racing in a parking lot chased by the cops.

### Sommario

Le particelle accelerate nella catena di acceleratori al CERN raggiungono energie elevate, la più elevata, al momento di collisione nel LHC, è pari a 7 GeV.

Durante l'azionamento delle macchine, inevitabilmente un certo numero di particelle sono perse dal fascio, depositando energia nelle parti che compongono la macchina e generando una cascata di particelle secondarie nella collisione con la struttura.

Il processo di generazione della cascata, nell'interazione con la struttura dell'acceleratore, attiva il materiale, costituendo un fattore di rischio per i lavoratori nell'acceleratore.

A seconda dell'entità delle perdite è anche possibile che si determini un danneggiamento fisico dei componenti dell'acceleratore. Nel Large Hadron Collider, i magneti superconduttori che mantengono le particelle nell'orbita circolare e forniscono la necessaria messa a fuoco al fascio sono mantenuti ad una temperatura di funzionamento pari a 1.9 K attraverso un sistema criogenico facente uso di elio superliquido. Un innalzamento di temperatura potrebbe potenzialmente interrompere il fenomeno superconduttivo, provocando un innalzamento improvviso della resistivitá del materiale e la dissipazione immediata di tutta l'energia immagazzinata nel magnete, danneggiandolo irrevocabilmente. La perdita del fascio é potenzialmente distruttiva anche negli acceleratori minori, nel SPS é in grado di perforare la camera a vuoto che lo contiene.

Il sistema di monitoraggio delle perdite del fascio è stato sviluppato per proteggere affidabilmente le macchine che compongono la catena di acceleratori del CERN, minimizzare l'attivazione dei materiali e fornire informazioni sullo stato del fascio agli operatori del sincrotrone: il sistema fornisce misure riguardo a restrizioni dell'apertura focale, distorsione dell'orbita, oscillazione del fascio e diffusione delle particelle. Tali informazioni sono utilizzate per regolare i parametri della macchina e massimizzare l'efficienza di trasmissione delle particelle dalla sorgente al punto di interazione. Per questo motivo, due tipi di rivelatori sono distribuiti lungo gli acceleratori, nelle posizioni in cui si attendono le perdite più significative: il tipo di sensore principale è la camera di ionizzazione, sebbene dove si attendano dosi estremamente elevate, tali da saturarne la risposta, vengono utilizzati monitor di emissione secondaria. Entrambi i rivelatori sono sensibili alle cascate di particelle secondarie dovute alle interazioni ad alta energia e sono caratterizzati da una eccellente linearità e accuratezza rispetto all'energia persa dalle particelle nell'attraversamento, una risposta rapida e una buona resistenza alle radiazioni ionizzanti.

Laddove è richiesta una protezione pronta della macchina, per ogni posizione dei rivelatori, la frazione della cascata di particelle che interagisce con il sensore è ricondotta all'energia deposta nel magnete attraverso simulazioni ed è definito un massimo valore permesso, tale da non causare danni.

Il segnale proveniente dal rivelatore è letto dall'elettronica di misura e, dove necessario, il valore acquisito è confrontato con la soglia associata alla posizione considerata lungo l'anello. A causa della varietà delle dimensioni degli acceleratori, il segnale può essere acquisito e convertito in digitale nel tunnel dell'acceleratore e inviato all'elettronica di superficie per essere processato – come avviene nell'LHC – o l'intera acquisizione e processamento può essere effettuata in superficie in una zona protetta ricavata ad hoc. Nel primo caso, è necessario che l'elettronica sia in grado di tollerare l'esposizione alle radiazioni.

Quando è rilevato che una soglia energetica è stata superata, l'abilitazione del fascio è interrotta e le particelle sono dirette verso una linea di dump. Nelle macchine che utilizzano magneti caldi – ad esempio PS Booster – quando si verificano delle perdite eccessive, i parametri della macchina sono regolati, migliorando così la qualità del fascio.

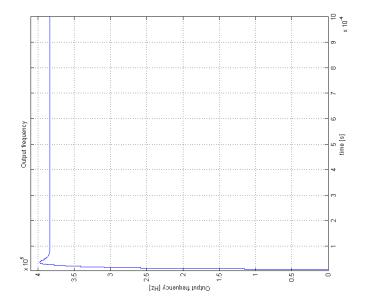

In questo lavoro, è stato realizzato il progetto di un convertitore digitale per il segnale di corrente proveniente da camere di ionizzazione, basato su un principio di conversione corrente-frequenza. Il progetto si rivolge agli acceleratori Proton Synchrotron, PS Booster e al futuro LINAC4, dove le perdite sono elevate rispetto ad altri casi simili, con un massimo pari a 100 mA. La minima corrente che si vuole rilevare vale 1 nA.

Il sistema permette l'acquisizione integrale di segnali di ambo le polarità senza richiedere alcuna configurazione e fornisce un numero digitale avente un LSB pari ad una carica elementare, corredato da un conteggio frazionario tramite un convertitore analogico digitale, per incrementare la risoluzione. Dopo una introduzione sul CERN, la prima parte fornisce una descrizione del sistema di misura delle perdite del fascio e dei sensori utilizzati. La teoria alla base del loro funzionamento è rivista e corredata di misure sperimentali.

Successivamente, è effettuato un confronto tra le possibili scelte che possono essere fatte per realizzare il dispositivo.

Sono innazitutto considerate le tecniche presenti in letteratura che permettono l'acquisizione del segnale per accoppiamento in continua, con particolare attenzione a quelle che offrono un range dinamico elevato, tra cui i convertitori corrente-frequenza. Nel capitolo successivo, è rivista la teoria della misura di carica associata ad impulsi di corrente rapidi e ripetitivi, tali sono quelli generati dai singoli gruppi di particelle che riempiono gli acceleratori. Per ottenere un range dinamico elevato, è data particolare attenzione alla minimizzazione della carica di rumore equivalente (ENC), basata sulla teoria del filtraggio ottimo.

Tra le due categorie, è stata scelta la prima, per le seguenti ragioni: il segnale di uscita dalla camera di ionizzazione è una rapida sequenza di impulsi, spaziati di 500 ns caratterizzati da una lunga coda, dovuta alla lenta deriva degli ioni nel gas che riempie il rivelatore. La carica di questi impulsi vuole essere misurata integralmente ma la soppressione della coda viene ad essere necessaria per impedire la sovrapposizione dei segnali in ingresso al convertitore analogico digitale alla fine della catena di filtraggio. Inoltre, il sistema non si presta facilmente a misure di correnti di ambo le polarità, richieste nelle specifiche.

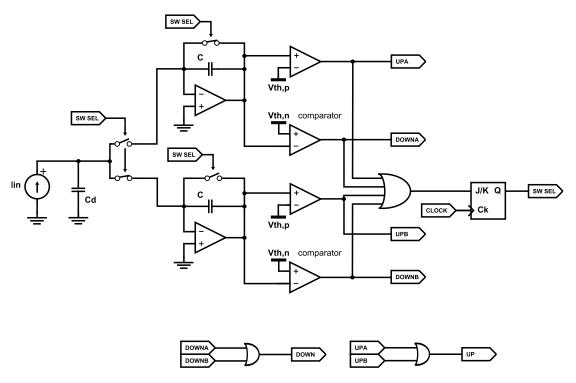

Diverse architetture circuitali sono considerate e modifiche sono proposte ove necessarie. Tra i circuiti analizzati sono presenti integratori a bilancio di carica, stadi a due integratori operanti in parallelo e integratori con condensatori commutabili, in versioni sincrone e asincrone.

È stato progettato un sistema, contenente un FPGA per il processamento dei dati e la loro trasmissione su bus VME64. È stato scritto il codice VHDL necessario al funzionamento, incluso il processamento dei dati acquisiti e la loro organizzazione in somme parziali su finestre temporali mobili, la loro trasmissione secondo il corretto protocollo sul bus e diverse funzionalità secondarie che forniscono informazioni sullo stato del sistema. Un primo prototipo è stato inviato per essere realizzato. A causa di alcuni ritardi nella realizzazione della scheda stampata, al momento della scrittura di questa tesi non sono ancora disponibili dati sperimentali.

### **Abstract**

The particles accelerated in CERN accelerator chain reach high energies, topped by the particle energy at collision in the LHC, 7 GeV.

During the operation, an amount of particles is inevitably lost from the beam. Depending on the extent of the losses, physical damage to machine components may be caused and the shower of secondary emission particles deposits energy in the surrounding equipment constituting the accelerator. The hadronic cascade also activates their materials, representing a hazard to the workers at CERN.

In the LHC, the superconducting magnets that constitute the synchrotron lattice are kept at an operating temperature of 1.9 K through a cryogenic facility employing superliquid helium, the increase in their temperature potentially initiates a quench. In the SPS, the damage due to a lost beam is also visible.

The Beam Loss Monitoring (BLM) system has been developed to reliably protect the machines composing CERN's accelerator chain and additionally provide information about the beam status: the system provides observations about local aperture restrictions, orbit distortion, beam oscillations and particle diffusion, allowing the operators to tune the machines, measure and maximize the efficiency of the chain.

To achieve this, two types of particles detectors are distributed along the machines in the positions where the most intense losses are expected, typically where aperture limitations are present – for example where the collimators are located. The main type of detector in use is the ionization chamber, albeit where a very high dose rate is expected Secondary Emission Monitor (SEM) are employed instead. Both types of detectors are sensitive to the hardronic showers initiated by high energy particles and they are characterized by high linearity and accuracy with respect to the energy lost by the particles, a fast responses and good radiation tolerance.

Where timely machine protection is in place, for every detector location the fraction of particles from the hardronic showers has been linked to the energy distribution within the coil through simulation-based analysis and maximum allowable energy value has been established.

The signal from the detector is acquired by the front-end electronics and, where applicable, the measurement is compared with the threshold relevant for the considered ring location. As the dimensions of the accelerators varies greatly, the signal might be acquired, digitized in the accelerator tunnel and then sent to the surface electronics to be processed – as it happens in the LHC – or the complete processing may occur in a shielded facility closely located. In the former case, radiation tolerant electronics is required.

In the LHC, when a threshold is exceeded, the beam permit signal is revoked and the circulating particles are directed towards the dump line. In machines employing warm magnets – such as the PS Booster – the beam parameters are tuned before the next injection, to increase the quality of the beam.

A discrete components design of a current digitizer based on the current-to-frequency converter (CFC) principle has been studied in this work. The design targets at rather high input current compared to similar acquisition systems, with a maximum equal to 100 mA and a minimum of 1 nA, as required by the ionization chamber that will be employed in the Proton Synchrotron and Booster accelerators as well as in the LINAC 4. It allows the integral acquisition of currents of both polarities without requiring any configuration and provides a digital number having an LSB equal to a reference charge complemented with an additional fractional count through an ADC, to increase the resolution.

Several architectural choices we considered for the front-end circuit, including charge balance integrators, dual-integrator input stages, integrators with switchable-capacitor, in both synchronous and asynchronous versions.

The signal is processed by an FPGA and transmitted over a VME64x bus.

## Acknowledgements

I am very grateful to Dr. Bernd Dehning, for giving me valuable advice and answering in detail all my questions, even during lunch breaks or late in the evening. I surely appreciated his back-of-the-envelope calculations and how he showed me that from simple concepts great things can be built. I'm surely very grateful also to my supervisor, Ewald Effinger who closely followed my work throughout the year.

During these demanding – but overall surely happy – years at Politecnico I had the pleasure of being a student and having as supervisor Prof Marco Sampietro, to whom I am supremely grateful.

Many thanks to Christos Zamantzas, for helping me out many times, sometimes they were small but important things and for sharing with me his insight in digital design. And for being a friend.

I surely appreciated the time spent with the other students in the BE-BI-BL section, my "office-mate" Mohamed, Javier, Til, Aurelian, Christoph and Daniel.

Outside the time spent in the lab or in front of the PC, I was very luck to meet some good friends, Daniel, Ling and Lourdes. If this year has been so pleasant, they're surely responsible.

## **Abbreviations**

ADC Analog Digital Converter

**BLM** Beam Loss Monitoring

**BJT** Bipolar Junction Transistor

**CERN** European Organisation for Nuclear Research

CFC Current-to-Frequency Converter

**DAC** Digital to Analog Converter

**DPDT** Double Pole Double Throw

**DR** Dynamic Range

**ENC Equivalent Noise Charge**

FCC Frequency-to-Current Converter

FF Flip-Flop register

FPGA Field Programmable Gate Array

GBW Gain Bandwidth Product

IC Integrated Circuit

**LEIR** Low Energy Ion Ring

**LHC** Large Hadron Collider

LINAC Linear Accelerator

LSB Least Significant Bit

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

**OA** Operational Amplifier

PS or CPS (CERN) Proton Synchrotron

**SNR** Signal to Noise Ratio

**SPDT** Single Pole Double Throw

**SPS** Super Proton Synchrotron (CERN)

**SPST** Single pole Single Throw

VFC Voltage-to-Frequency Converter

VHDL VHSIC Hardware Description Language

## **Contents**

| 1 | CEI | RN - Eu                     | ropean Organization for Nuclear Research                                                             | 3  |

|---|-----|-----------------------------|------------------------------------------------------------------------------------------------------|----|

|   | 1.1 | CERN                        | experiments                                                                                          | 4  |

|   | 1.2 | The C                       | ERN Accelerator Complex                                                                              | 4  |

|   |     | 1.2.1                       | The Large Hadron Collider                                                                            | 6  |

|   |     | 1.2.2                       | The Super Proton Synchrotron                                                                         | 8  |

|   |     | 1.2.3                       | The Proton Synchrotron and the Proton Synchrotron Booster                                            | 10 |

| 2 | The | Beam I                      | Loss Monitoring System                                                                               | 11 |

|   | 2.1 | The Bo                      | eam Loss Monitors                                                                                    | 11 |

|   | 2.2 | Princip                     | ples of operation of ionization chambers                                                             | 11 |

|   |     | 2.2.1                       | Energy loss by heavy charged particles                                                               | 12 |

|   |     | 2.2.2                       | Energy per ionization event, mobility of the charge carriers and region of operation of the detector | 14 |

|   |     | 2.2.3                       | Ramo's theorem                                                                                       | 16 |

|   |     | 2.2.4                       | Parallel plate capacitor                                                                             | 18 |

|   | 2.3 | 2.3 BLM ionization chambers |                                                                                                      | 20 |

|   | 2.4 | Specifi                     | ications                                                                                             | 23 |

| 3 | Circ | uit architectures for DC current measurements                                    | 26 |

|---|------|----------------------------------------------------------------------------------|----|

|   | 3.1  | High dynamic range and bandwidth                                                 | 26 |

|   | 3.2  | Transimpedance amplifier with switched gain                                      | 31 |

|   | 3.3  | Charge amplifier                                                                 | 35 |

|   |      | 3.3.1 Alternative implementations of a charge amplifier                          | 38 |

|   | 3.4  | Amplifier with a nonlinear characteristic                                        | 40 |

|   | 3.5  | Logarithmic Amplifier                                                            | 44 |

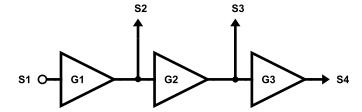

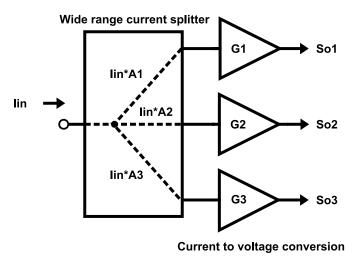

|   | 3.6  | Multiple stages transimpedance amplifier and single stage with current splitting | 48 |

|   | 3.7  | Direct digital acquisition                                                       | 50 |

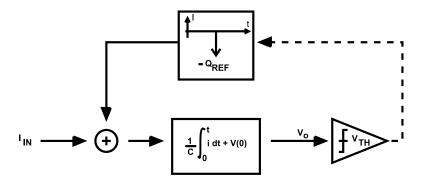

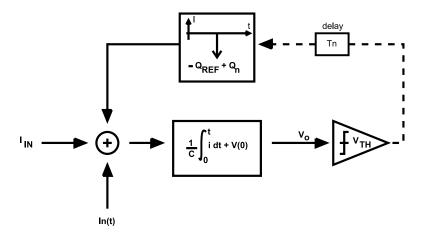

|   | 3.8  | Current to frequency converter                                                   | 50 |

|   |      | 3.8.1 Current steering multivibrator                                             | 51 |

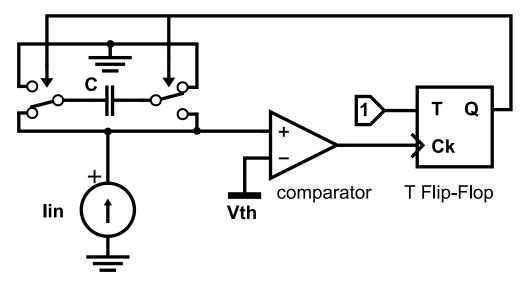

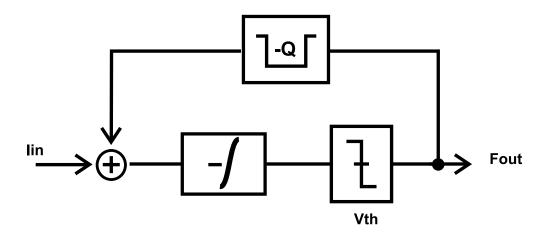

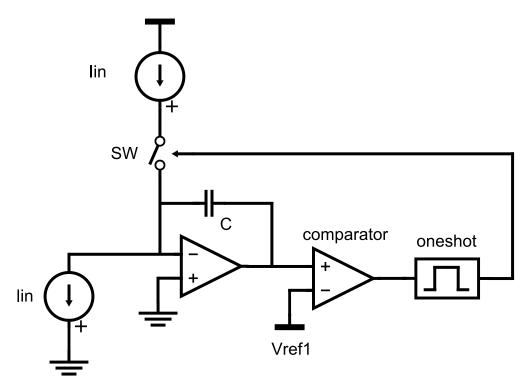

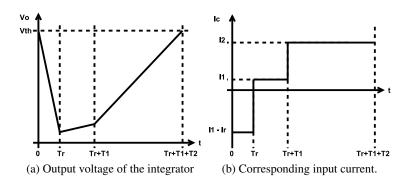

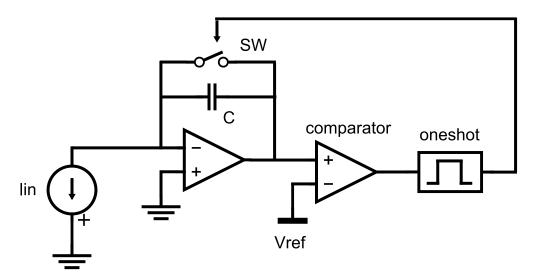

|   |      | 3.8.2 Charge balance integrator and derived architectures                        | 52 |

|   |      | 3.8.3 CFC with voltage reset of the integrating capacitor                        | 57 |

|   | 3.9  | $\Delta\Sigma$ current quantizer                                                 | 60 |

|   | 3.10 | Current to frequency converter with feedback                                     | 63 |

| 4 | Circ | euit architectures for single bunch losses measurements                          | 66 |

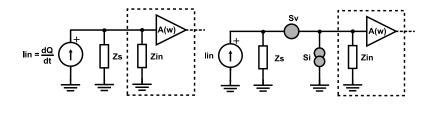

|   | 4.1  | Overview of the system                                                           | 66 |

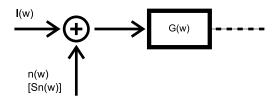

|   | 4.2  | A universal limit on the signal to noise ratio                                   | 67 |

|   | 4.3  | Noise and signal at the input of the amplifier                                   | 69 |

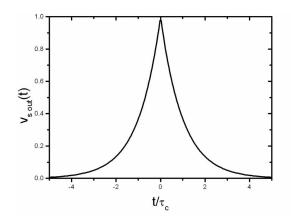

|   | 4.4  | Practical signal processing                                                      | 73 |

|   | 4.5  | Detector output capacitance                                                      | 75 |

| 5  | Ana              | log and  | digital circuits, board design                                       | 77  |  |  |

|----|------------------|----------|----------------------------------------------------------------------|-----|--|--|

|    | 5.1              | Analog   | g front-end circuits                                                 | 77  |  |  |

|    |                  | 5.1.1    | Extension of a current to frequency converter to dual input polarity | 78  |  |  |

|    |                  | 5.1.2    | Current to frequency converter with a switched capacitor             | 79  |  |  |

|    |                  | 5.1.3    | Charge balance integrator                                            | 84  |  |  |

|    |                  | 5.1.4    | Timing                                                               | 88  |  |  |

|    |                  | 5.1.5    | Dual integrator stage                                                | 90  |  |  |

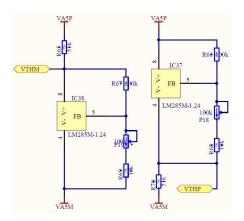

|    |                  | 5.1.6    | Common analog parts                                                  | 91  |  |  |

|    | 5.2              | Limita   | tions of the analog channels designed                                | 93  |  |  |

|    |                  | 5.2.1    | Voltage range at the input of the ADC                                | 93  |  |  |

|    |                  | 5.2.2    | Resolution limit of the current to frequency converter               | 95  |  |  |

|    |                  | 5.2.3    | Maximum output frequency                                             | 100 |  |  |

|    |                  | 5.2.4    | Minimum detectable input current                                     | 100 |  |  |

|    | 5.3              | Digital  | circuits                                                             | 101 |  |  |

|    |                  | 5.3.1    | Fractional counts                                                    | 102 |  |  |

|    |                  | 5.3.2    | Data processing: running sum                                         | 102 |  |  |

|    |                  | 5.3.3    | VMEbus Controller                                                    | 103 |  |  |

| 6  | Con              | clusions |                                                                      | 105 |  |  |

| Bi | Bibliography 105 |          |                                                                      |     |  |  |

|                                             | CONTENTS |

|---------------------------------------------|----------|

| List of Figures                             | 111      |

| A Key events of the history of CERN         | 115      |

| B PS accelerator loss measurements          | 117      |

| C LHC ionization chamber: technical drawing | 121      |

| D SPS ionization chamber: technical drawing | 123      |

| E Circuit simulations                       | 125      |

| F VHDL code                                 | 127      |

## Introduction

This work was carried out at CERN during an one year internship in the BE-BI-BL section.

The main objectives of this work are summarized as follows:

- Evaluation of the different architectures available at the state of the art to measure the current signal

- Design, review and simulation, where applicable, of selected circuits conforming to the specifications.

- Design of the digital electronics required for processing and data transmission.

- Realization of a prototype printed circuit board (PCB).

- Review of the results and future developments.

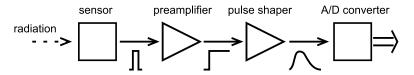

The first chapter introduces CERN, its accelerator complex and the Beam Loss Monitoring system.

The second chapter is dedicated to the Beam Loss Monitoring (BLM) system, in particular to the particle detectors, their outcoming signal and the electrical circuit.

Chapter 3 reviews the possible state-of-the-art design choiches for the measurement of currents extending to DC over a wide dynamic range.

In Chapter 4, the techniques for fast measurement of the charge of the single pulses due to each bunch are described, with focus on minimizing the noise of the measurement, thereby increasing the dynamic range.

The first part of Chapter 5 describes the selected circuits, deals with the modifications to their architectures introduced in this work, describes the expected results front-end analog part of the acquisition board. The second part of the chapter is dedicated to the digital circuits: the section covers the signal acquisition and its processing, the choice of the FPGA and the VHDL code written.

Possibilities for further developments are part of the topic of the Conclusions.

## **Chapter 1**

# **CERN - European Organization for Nuclear Research**

CERN, the European Organization for Nuclear Research, is the world's largest particle physics laboratory. The acronym originates from the initial French name "Conseil Européen pour la Recherche Nucléaire", or European Council for Nuclear Research, a provisional body founded in 1952 with the mandate of establishing a world-class fundamental physics research organization in Europe.

When the laboratory officially was founded in 1954, the organization was given the name European Organization for Nuclear Research, although the name CERN was retained. CERN was one of Europe's first joint ventures and it includes presently 20 member states.

The research center is located across the Franco-Swiss border near Geneva, besides the Jura mountains.

CERN's main function is to provide to scientists the particle accelerators, detectors and other infrastructure needed for high-energy physics research. Even advancements in other fields are due to the work of the scientists working at the laboratory, the most popular being the World Wide Web. Numerous experiments focused on different aspects have been constructed at CERN and the access is provided to universities and research group spread around the world. A large computer center provides the powerful data processing facilities for experimental data analysis, the data storage and a wide area networking hub allows the access.

The key events of the history of CERN from its first conception in 1954, to the first beam in the LHC in 2008 can be found in appendix A.

#### 1.1 CERN experiments

The bleeding edge research is currently carried out in the Large Hadron Collider, whose operation is scheduled to restart in October 2009. The LHC has four main experiments, each is constituted by an assembly of detectors centered around a collision point, tracking the trajectories and measuring the energies of the generated particles at the four beam crossings in the machine. These detectors are specifically targeted at searching for the Higgs boson and evidence of supersymmetry.

The experiments are ATLAS, A Toroidal LHC ApparatuS, CMS, the Compact Muon Solenoid, ALICE, A Large Ion Collider Experiment and LHCb, which stands for LHC beauty.

The ATLAS detector is 44 meters long and 25 meters in diameter, weighing about 7 thousand tonnes. It employs silicon pixels and strips, and a straw-tube based transition radiation detector inside a superconducting solenoid with a SI2T magnetic field. The region surrounding the inner core, closest to the interaction point, is constituted by a electromagnetic calorimeter enclosed by ironscintillator and Cu/W-LAr hadronic calorimeters. The outer shell is the ATLAS muon system, composed of muon drift tubes, thin gap chambers and resistive plate chambers embedded in a large array of 8 air-core toroid magnets.

CMS is a general-purpose detector, capable of studying many aspects of proton collisions. It contains subsystems which are designed to measure the energy and momentum of photons, electrons, muons, and other particles produced in collision. It is formed by five layers, the innermost being a silicon-based tracker, itself composed by silicon pixels and microstrips. Surrounding it is a scintillating crystal electromagnetic calorimeter, followed by a sampling calorimeter for hadrons. The tracker and the calorimetry are fitted inside a superconducting solenoid which generates a magnetic field of 4 T. Outside the magnet is the muon system, which is composed of drift tubes, cathode strip chambers and resistive plate chambers inserted between iron layers of the flux return. [43]

#### 1.2 The CERN Accelerator Complex

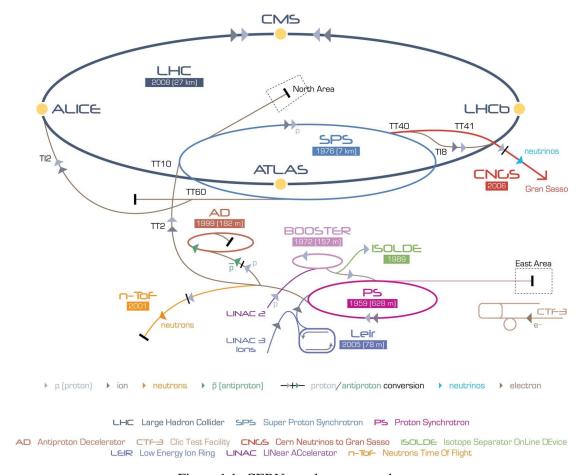

The protons collided in the experiments described are accelerated through a chain of five accelerators:

$LINAC2 \rightarrow Booster \rightarrow PS \rightarrow SPS \rightarrow LHC$

Figure 1.1: CERN accelerator complex

On the other hand, the path for ions is,

LINAC3

$$\rightarrow$$

LEIR  $\rightarrow$  PS  $\rightarrow$  SPS  $\rightarrow$  LHC

This complex has been enhanced and upgraded over many years, the Proton Synchrotron (PS) was one of the first accelerators commissioned at CERN, and almost fifty years later is still working with very high efficiency. In PS, the protons are accelerated an energy equal to 28 GeV, from here they are passed to the SPS where they are accelerated to 450 GeV, finally they are transferred to LHC, where acceleration will bring protons to an energy of 7 TeV, determining a collision energy of 14 TeV.

CERN accelerator complex is shown in fig. 1.1, where other experiments are also visible. One of the most notable is the CERN Neutrinos to Gran Sasso (CNGS), where a beam consisting of only muon-type neutrinos from the SPS accelerator is sent to the Gran Sasso National Laboratory (LNGS) of the INFN in Italy. Since neutrinos interact very rarely with matter, the beam is received at a distance of 730 km. Other experiments are the neutron time-of-flight facility (n\_TOF), a pulsed neutron source operative since 2001, ISOLDE, a line dedicated to the production of several different radioactive ion beams, the CLIC Test Facility (CTF3) a linear electron-positron accelerator aimed at demonstrating the feasibility of the proposed Compact Linear Collider (CLIC) study and the CERN Antiproton Decelerator (AD).

#### 1.2.1 The Large Hadron Collider

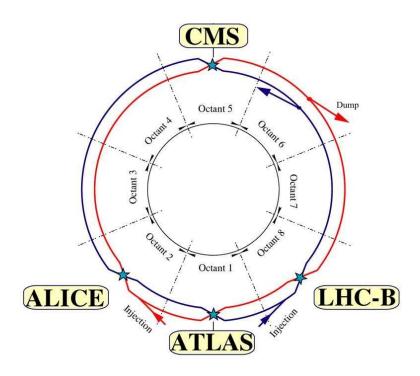

The Large Hadron Collider (LHC) is the latest accelerator built at CERN, first operational in September, 2008 and scheduled for restart in October, 2009. [21]

Characterized by a circumference length of 27 km, it is divided in eight sectors, or octant, each 3.3 km in length. The particles in the machine are concentrated into bunches, spaced by 25 ns and 1.12 ns long. Each ring hosts an effective number of 2808 bunches with an intensity of  $1.1 \times 10^{11}$  per bunch of protons. The revolution time is 88.9 µs corresponding to a frequency of  $11.246\,\mathrm{kHz}$ .

The particles are kept in a circular orbit by cooled magnets, providing a magnetic field of 8.3 T. The magnets are made from superconducting NbTi, supporting a current of about 12 kA and storing, during the operation, a total amount of energy of about 10 GJ. Each sector is served by a cryoplant, in which is housed a helium refrigerator, providing superfluid helium at 4.5 K or 1.9 K.

Figure 1.2: Structure of the LHC, with experiment locations in evidence

| Beam Parameter                      | Value                                                 |

|-------------------------------------|-------------------------------------------------------|

| Proton Energy at Injection          | 450 GeV                                               |

| Proton Energy at Collision          | 7 TeV                                                 |

| Protons per Bunch                   | $1.15 \times 10^{11}$                                 |

| Number of Bunches in LHC            | 2808                                                  |

| Protons in LHC                      | $3.23 \times 10^{14}$                                 |

| Number of Bunches in SPS extraction | 216 or 288                                            |

| Protons at SPS extraction           | $2.48 \times 10^{13} \text{ or } 3.31 \times 10^{13}$ |

| Number of Bunches at PS extraction  | 72                                                    |

| Protons at PS extraction            | 8.27 1012                                             |

Table 1.1: Beam Parameters of the LHC. [21]

The luminosity  $\mathcal{L}$  of a storage ring determines the secondary particle rate and therefore the discovery potential. It is a measurement of the number of collisions that can be produced in a detector per cm<sup>2</sup> and per second and it is a parameter optimized in the design of a storage ring.

$$\mathcal{L} \approx \frac{N^2 f}{4\pi\sigma_x \sigma_y} \tag{1.1}$$

N are the number of particles per bunch of beam, supposed to be equal for both beams

f is the rate of bunches with protons [Hz]

$\sigma_x$  and  $\sigma_y$  are the standard deviations that characterize the Gaussian transverse beam profile [cm]

The luminosity of the LHC will be approximatively  $1 \times 10^{34}$  /cm<sup>2</sup>/s, which multiplied by the interaction cross section determines the average rate of collisions per seconds.

The other main parameters of the machine are listed in tab. 1.1. Its performances will surpass comparable machines in energy by a factor 7, in luminosity by a factor of 100 and in beam intensity by a factor of 23.

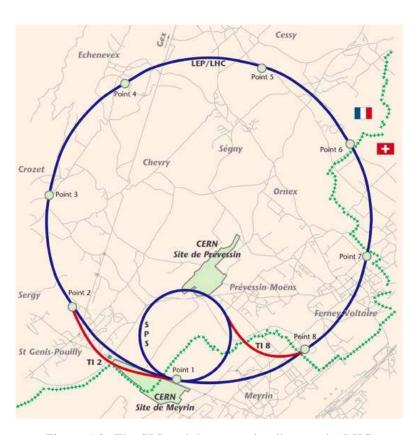

#### 1.2.2 The Super Proton Synchrotron

The SPS is a circular proton accelerator operational since 1976, with a circumference of 7 km. At the end of the 70's, it was used also as a proton - antiproton collider, revealing the W and

Figure 1.3: The SPS and the extraction lines to the LHC

Z bosons, for whose discovery the Nobel Prize was awarded to Simon van der Meer and Carlo Rubbia. SPS is currently in use as a proton or heavy ion accelerator, with a maximum energy of 450 GeV. Two transfer lines, TI2 and TI8, have been added to the machine, permit the injection of the beam in the LHC. The SPS, the transfer lines and their connection to the LHC are shown in fig. 1.3.

#### 1.2.3 The Proton Synchrotron and the Proton Synchrotron Booster

Figure 1.4: A picture of the PSB tunnel, showing the four ring circular accelerator.

The CERN Proton Synchrotron (PS or CPS) is a circular accelerator with a circumference of 628.3 m. It is currently the oldest machine in operation at CERN (built in 1950), due to its extreme versatility: it is capable of accelerating protons, antiprotons, electrons, positrons and various species of ions. Over the years, major upgrades have improved its performances by more than a factor of 1000 since its initial operation in 1959.

The protons are injected in PS from the Proton Synchrotron Booster (PSB), the smallest circular proton accelerator in the CERN accelerator complex, built in 1972 and measuring 160 meters. It receives protons at an energy of 50 MeV from the linear accelerator Linac2 and accelerates them up to 1.38 GeV, when they are injected into the Proton Synchrotron.

## **Chapter 2**

## The Beam Loss Monitoring System

#### 2.1 The Beam Loss Monitors

The ionization chamber is the main Beam Loss Monitor (BLM) currently in use in CERN accelerator complex. As it will be explained more in detail in the next sections, the ionization chamber provide a charge on the electrodes proportional to the amount of particles that traversed the active volume. The incoming particles ionize the nitrogen gas within the chamber, freeing electrons from the gas molecules. The positively charged ions and electrons are separated through an applied electric field and collected at the electrodes.

This chapter introduces the principles of the operation of ionization chambers and gives a basic introduction to energy loss of charged particles in matter [19, 45].

#### 2.2 Principles of operation of ionization chambers

When energetic particles pass through matter a certain amount of their energy is lost in the interaction. The amount of lost energy and the different processes responsible for its transfer depend on the characteristics of the particle, such as charge and mass, energy and the material.

Several types of interaction that may occur, here the principal ones are summarized by particle type. [45]

Electrons lose energy mainly by ionization at low energies and by bremsstrahlung at high energies. Particles without charge as photons and neutrons do not directly ionize the gas, but generate secondary charges by a combination of other processes. Photons may lose their energy in the interaction with an atom and liberate an electron through the photoelectric effect. Other phenomena in which photons are of primary importance are Compton scattering and the pair creation process. If we consider neutrons, different interactions as elastic or inelastic nuclear collisions become important, depending on the energy of the particle.

#### 2.2.1 Energy loss by heavy charged particles

Particles with a mass greater than the mass of the electrons are briefly considered in this section.

Several different interactions are responsible for the transfer of energy form the heavy particle to the molecule. The ionization event is possible if the transferred energy is greater than the binding energy of an electron in the outer shell of the atom. If this condition is not verified, the effect is an increased temperature of the gas, until the energy is transferred elsewhere and the gas returns at rest.

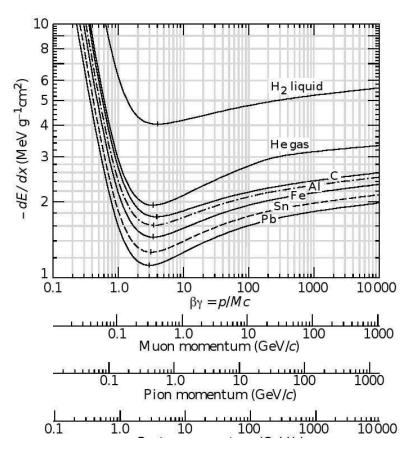

For particles of energies of the order of 0.1 to 100 GeV, the Bethe-Bloch equation (eq. 2.1) gives the average energy lost by a charged particle (dE) as it travels a length equal to dx [16]. The quantity dE/dx is also referred to as stopping power of the material.

$$-\frac{dE}{dx} = Kz^{2} \frac{Z}{A} \frac{1}{\beta^{2}} \left[ \frac{1}{2} \ln(\frac{2m_{e}c^{2}\beta^{2}\gamma^{2}T_{max}}{I^{2}}) - \beta^{2} - \frac{\delta}{2} \right]$$

(2.1)

$$\gamma = (1 - \beta^2)^{-1/2}$$

Z is the atomic number of the gas

A is the atomic mass of the medium

z is the charge of the heavy charged particle

$\beta$  is the velocity of the particle normalized to the speed of light c

$\delta$  is a density effect correction

K is defined as  $4\pi N_A r_e^2 m_e c^2$

Figure 2.1: Stopping power of different materials, from [57, 45]

$N_A$  is Avogadro's number

$r_e$  is the classical electron radius

$T_{max} = 2m_e c^2 \beta^2 \gamma^2$  is the maximum transferable energy in a single collision of an electron

The mean energy loss rate in different materials for muons, pions and protons depending on their kinetic energy is shown in fig. 2.1.

## 2.2.2 Energy per ionization event, mobility of the charge carriers and region of operation of the detector

Nitrogen gas  $(N_2)$  was chosen for the BLM monitors. The first ionization potential of the electron is at about 15.5 eV, this corresponds to the minimum energy that a charged particle or a photon must have in order of be detected, for lower energies, a single particle interaction can't free an electron.

Since other processes, in addition to ionization events, contribute to the energy loss of the particle, the average energy required per creation of ion-electron pair is greater than the ionization energy. Its value is called the W-factor and it is in the range 25 eV-35 eV depending on the type of the incoming particle and gas. The average number of electron-ion pairs created is proportional to the energy lost by the particle and inversely proportional to the W-factor. [45]

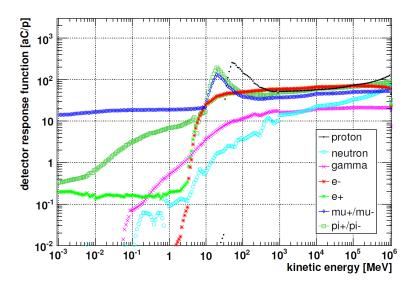

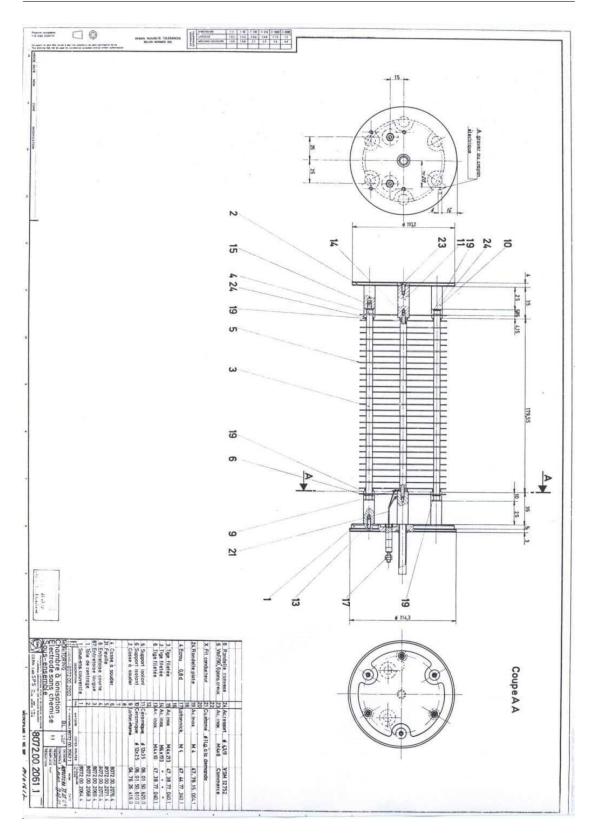

The simulated LHC BLM detector response function for different particle types is shown in fig. 2.2. The impact angle of the particles relative to the detector axis is  $60^{\circ}$ , the detector structure is described in sect. 2.3.

The drift velocity of a charged particle in the pressurized gas where a uniform electric field E is present can be described by the law:

$$v = \mu \frac{E}{P} \tag{2.2}$$

$\mu$  is a constant called mobility, associated with the considered carrier [m Pa<sup>-1</sup> V<sup>-1</sup>]

E is the electric field [V m<sup>-1</sup>]

P is the pressure of the gas [Pa]

Figure 2.2: Collected charge for different particles at different energies. From [45].

Ions have much lower mobility – a factor  $1 \times 10^3$  or more – than electrons and therefore drift at a lower velocity and are collected at the electrodes after a longer time.

Two main observations led to the choice of  $N_2$  as filling gas for the ionization chamber: it is, between the possible choices, the gas with the highest ion mobility and it is a gas common in the air, therefore a ionization chamber with leakage would still provide an output signal. [45]

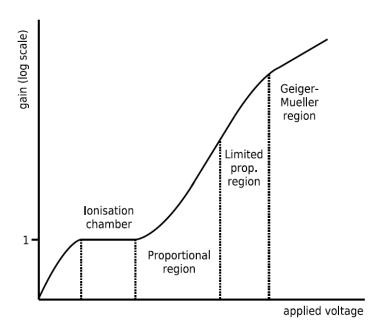

Another important observation concerns the operating mode of the ionization chamber as the applied voltage is varied. The gain of the ionization chamber is defined as the proportionality factor between the initially ionized charge and the charge overall collected.

A plot of the gain is shown in fig. 2.3, it is possible to distinguish several operating conditions, the three most important will be mentioned here.

At low voltages, the induced field in the ionization chamber is low, producing a slow drift of the carriers which will have greater chances of recombining before reaching the electrodes. The zone labeled "ionization chamber" is the region of standard operation, here the gain is constant and approximatively equal to one. In this region, a fixed ratio of the ionized charge is collected, independently of the applied field and therefore the gain has a very low dependence on the fluctuations of the supply. Increasing further the applied potential, multiplication effects begin to appear. The carriers can gain enough energy to collide and ionize other molecules. The collected charge will again be proportional to the initial ionized charge, but through a multiplication factor, greater than one, that depends on the applied voltage. In fig. 2.3, this

Figure 2.3: Gain of a ionization chamber with applied voltage, from [45].

region is labeled "proportional region". In the next zones, other non-linear effects will modify the gain. To preserve the linearity of the detector, the operating point of the ionization chamber is kept out of these regions.

#### 2.2.3 Ramo's theorem

The current induced on the electrodes by a charge generated in the medium can be derived with the Ramo-Shockley theorem.[37, 41, 44]

Consider a structure delimited by an arbitrary number of electrodes and assume that all the conductors are at ground potential. A charge q is situated in the region. If the potential of the electrostatic field between the conductors is V, then we can write

$$\nabla^2 V = 0 \tag{2.3}$$

A small equipotential sphere can be chosen to surround the charge q. Let  $V_q$  be the potential on its surface  $S_s$ . Applying Gauss' Law,

$$\int_{S_s} \frac{\partial V}{\partial n} ds = 4\pi q \tag{2.4}$$

If the charge is removed and a conductor is biased at 1 V, calling the potential in this situation  $V_1$ , it is still true that  $\nabla^2 V_1 = 0$ , again in the region between the electrodes.

From Green's theorem,

$$\int_{Volume} (V_1 \nabla^2 V - V \nabla^2 V_1) dv = -\int_{S_{boundary}} \left[ V_1 \frac{\partial V}{\partial n} - V_1 \frac{\partial V}{\partial n} \right] dS \tag{2.5}$$

If the volume in eq. 2.5 is chosen to be delimited by the surfaces of the electrodes (the surface of the biased electrode is called  $S_1$  in the following) and the surface of the sphere ( $S_s$ ), the left-hand side integral is null and the right hand integral can be split in three components:

- The integral over the grounded conductors, which is null, since V and  $V_1$  are both zero.

- The integral over the surface of the biased electrode. Here V=0 V and  $V_1=1$  V and the integral reduces to  $-\int_{S_1} \frac{\partial V}{\partial n} ds$ .

- The integral over the surface of the sphere, which can be written as the sum  $-V_{q1}\int_{S_s} \frac{\partial V}{\partial n} dS$  and  $V_q \int_{S_s} \frac{\partial V_1}{\partial n} dS$ , the latter integral corresponds to Gauss' Law in the second situation, when there is no charge between the conductors and it is therefore null.

Eq. 2.5 can be rewritten as:

$$0 = -\int_{S_1} \frac{\partial V}{\partial n} ds - V_{q1} \int_{S_2} \frac{\partial V}{\partial n} ds = 4\pi Q_i - 4\pi q V_{q1}$$

(2.6)

Where  $Q_i$  is the charge induced on the biased electrode.

$$Q_i = qV_{q1} (2.7)$$

Differentiating  $Q_i$  with respect to time, if the charge is moving in a direction x, we get the induced current:

$$i_{i} = \frac{dQ_{i}}{dt} = q \frac{dV_{q1}}{dt} = q \frac{\partial V_{q1}}{\partial x} \frac{\partial x}{\partial t} = q \frac{\partial \Phi}{\partial x} v_{x}$$

(2.8)

Where  $\Phi$  is a weighting potential associated with the considered electrode that describes the coupling of the potential to the considered conductor. It is calculated biasing the electrode under study to 1 V while all the others are connected to ground. The electric field in a given

geometry determines the trajectory of the particles and it coincides with the weighting field, obtained from the weighting potential, only in presence of two electrodes.

From the Ramo-Shockley Theorem, the following conclusions can be drawn:

• A charge q moving from position  $p_1$  to position  $p_2$  along any path induces a net charge on the electrode n given by:

$$Q_n = q \left( \Phi_n(p_2) - \Phi_n(p_1) \right) \tag{2.9}$$

• The instantaneous current can be written in terms of weighting field as  $i_i = -q\vec{v} \cdot \nabla \Phi_n$ . The electric field s responsible of the trajectory of the particle, while the weighting field is responsible of the induced current.

#### 2.2.4 Parallel plate capacitor

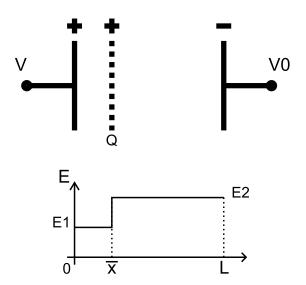

A plane capacitor with gas insulator is a basic structure for a ionization chamber. In this section, the signal induced on the electrodes by a plane layer of charge Q emitted from the anode and moving towards the cathode is derived, with and without Ramo's theorem and the results are compared. If, at a time  $\bar{t}$ , the layer of charge is located at the coordinate  $\bar{x}$ , the electric field in the device is as shown in fig. 2.4.

Figure 2.4: Electric field in a plane capacitor

The difference  $E_2 - E_1$  can be evaluated applying Gauss' Law:

$$\epsilon(E_2 - E_1) = Q/A \tag{2.10}$$

Where *A* is the area of the plates of the capacitor.

The anode voltage is given by,

$$V = \int_0^L E(x)dx + V_0 = E_1\bar{x} + E_2(L - \bar{x}) + V_0$$

(2.11)

Where L is the distance between the parallel plates and  $V_0$  is the cathode voltage.

Substituting 2.10 in 2.11, we get:

$$V = E_2 L - \frac{Q\bar{x}}{\epsilon A} + V_0 \tag{2.12}$$

The charge on the anode is equal to:

$$Q_a = -\epsilon A E_2 = -\frac{\epsilon A}{L} \left( V - V_0 + \frac{Q\bar{x}}{\epsilon A} \right) \tag{2.13}$$

The current flowing in the capacitor is the derivative in time of the charge on the anode,  $Q_a$ .

$$I = -\frac{dQ_a}{dt} = \frac{\epsilon A}{L} \left( \frac{dV}{dt} + \frac{Q}{\epsilon A} \frac{d\bar{x}}{dt} \right) = C \frac{dV}{dt} + \frac{QV}{L}$$

(2.14)

The two components are the current due to the capacitive coupling of the voltage applied on one electrode to the other and the current induced by the moving charges. Setting dV/dt = 0, integrating at both sides eq. 2.14, we get:

$$\int_0^T Idt = \int_0^L \frac{Q}{L} dx = Q \tag{2.15}$$

The integral of the induced current is equal to Q. It can be shown that if two layers of charge of the same absolute value Q and opposite sign are generated in an arbitrary position within the chamber, each of them will induce a current signal and the integral of their sum will again evaluate to Q.

The result in eq. 2.14 can be confronted with the one provided by Ramo's Theorem.

The weighting field is found setting the anode voltage to 1 V,

$$\Phi = \frac{1 \,\mathrm{V}}{L} \tag{2.16}$$

And therefore, from eq. 2.8, the current is I = Qv/L. If the voltage applied to the anode is constant, eq. 2.14 gives the same result.

#### 2.3 BLM ionization chambers

The ionization chamber in use in the BLM system are parallel plate chambers, more complex than the simple parallel plates capacitor considered previously.

The main parameters that affect the operation of this type detectors are the choice of the gas that fills it, its pressure, as the determine the sensitivity and mobility of the carriers, and the bias voltage, which determines the operating region. The BLM ionization chambers are filled with nitrogen at a pressure of 100mbar and the bias voltage applied to the detector 1.5 kV is applied to the electrodes.

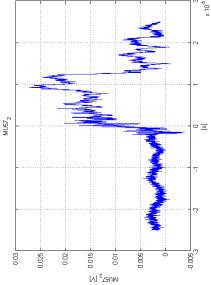

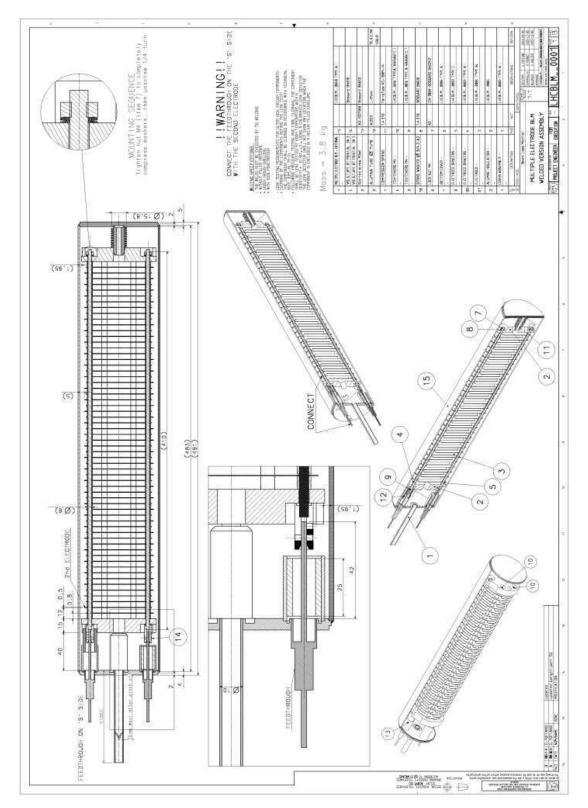

Two sensors having a very similar structure are in use: both of them have a circular section, electrodes of the same shape, orthogonal to the main axis of the chamber, with a thickness of 0.5 mm, equally spaced by 5.75 mm. Alternatively, one plate is connected to the output connector and the next to the high voltage input. The smaller ionization chamber, in use mainly in the SPS contains a total of 31 electrodes, while the bigger ionization chamber, in use mainly in the LHC but planned to be used in other accelerators as well, has a total of 61. They are hold in place by six stainless steel rods traversing longitudinally the whole structure and secured to the top and bottom plates by insulating ceramic bindings. [17, 45]

The two ionization detectors are enclosed in a stainless steel tube, with a wall thickness of 2 mm, and of a diameter equal to 75 mm, in the case of the LHC BLM (fig. 2.5), while the other (fig. 2.6) is wider and has a diameter of 93 mm.

Two cover plates are present: the bottom one, made of stainless steel as well and 4 mm (SPS BLM) or 5 mm thick; the top cover holds the connectors for the high voltage supply and the

Figure 2.5: BLM ionization chamber introduced for the LHC. Metallic enclosure removed.

Figure 2.6: BLM ionization chamber developed for SPS. Metallic enclosure removed.

output signal. Under it, a RC filter is located. The purpose of the low pass filter is to reject any picked up interference or residual ripple on the high voltage, to avoid an unintended modulation of the gain of the detector. The values of the componets are  $R=1\,\mathrm{M}\Omega$ ,  $C=0.5\,\mu\mathrm{F}$ , threfore the time constant of the filter is  $\tau=0.5\,\mathrm{s}$ .

The mechanical drawing of the LHC and SPS ionization chambers can be found in the appendix C and D.

The capacitance of the LHC monitor has been measured and is equal to 350 pF.

Another type of detector that has a limited use as a beam loss detector is the Secondary Emission Monitors (SEM), employed in the locations where an higher intensity of particle flux is expected and shown in fig. 2.7. Its design is similar to the ionization chambers, but the principle of operation is different. Three titanium electrodes are enclosed in a stainless steel tube kept under vacuum. The incident particles free electrons colliding with the electrodes, through a physical process known as secondary emission those particles are accelerated and collected on the electrode of the opposite polarity and as in the previous case, the induced signal is measured.

Figure 2.7: Secondary emission monitor. Metallic enclosure removed.

# 2.4 Specifications

The electronics studied in this will replace the existing electronics in two accelerators, the PS and the PSB. Additionally, it will be employed in the replacement of LINAC 2, the LINAC 4, as soon as its construction is completed, expected in 2011. [35]

The specifications for the design are reported in tab. 2.1. From them, the specifications for the front-end listed in tab. 2.2 were derived.

From the reported specifications, the following observations can be made: the number of lost particles from the beam has to be measured on different fixed windows. Those values, stored in a local memory over several windows, constitute the post mortem buffer and should be supplied when requested. The post mortem buffer is useful in case the machine cannot be operated because as soon as it is started one or more of the maximum particle loss thresholds are exceeded. In this situation, the buffer provides detailed information about the last seconds of operation of the machine, allowing the debugging of its settings.

Moreover, the highest instantaneous loss corresponds to 100 mA and the front-end electronics should be able to acquire this current without saturating.

A last observation regards the synchronization: the beginning of the measurement has to be synchronized with the beginning of the cycle or pulse, if the accelerator is linear.

|                                 | PS                                           | PSB                                                                     | LINAC 4                              |

|---------------------------------|----------------------------------------------|-------------------------------------------------------------------------|--------------------------------------|

| Time resolution                 | 2 µs                                         | 500 ns                                                                  | 2 µs                                 |

| Largest loss                    | Loss of $4 \times 10^{13}$ protons at 26 GeV | Loss of $4 \times 10^{13}$ protons at 26 GeV                            | $1.4 \times 10^9 \ H^- \text{ ions}$ |

| Integration windows             | 1 ms and 1.2 s                               | 1 ms and 1.2 s                                                          | 2 µs and 400 µs                      |

| Max window                      | 5 basic periods, or 6s                       | 1 basic period, or 1.2 s                                                | 400 µs                               |

| Post mortem                     | Not strictly necessary                       | Not strictly necessary                                                  | Yes                                  |

| Post mortem buffer length 6000, |                                              | maximum and minimum windows   1200, maximum and minimum windows   42000 | 42000                                |

| Logging frequency               | Once per cycle                               | Once per cycle                                                          | 2 Hz                                 |

| Synchronization                 | Start of cycle and revolution frequency      | Start of cycle and revolution frequency Start of pulse                  | Start of pulse                       |

Table 2.1: Specifications for the electronics

| Parameter                      | Value                      |

|--------------------------------|----------------------------|

| Maximum input current          | 100 mA                     |

| Minimum detected input current | 1 nA                       |

| Signal to noise ratio          | $1 \times 10^3$ or greater |

| Maximum linearity error        | 20                         |

Table 2.2: Specifications for the electronics

# **Chapter 3**

# Circuit architectures for DC current measurements

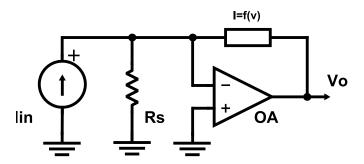

### 3.1 High dynamic range and bandwidth

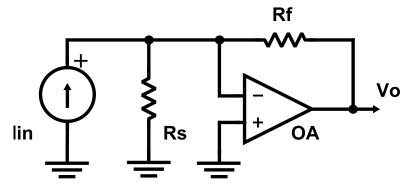

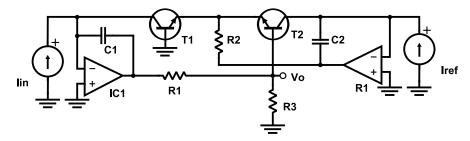

There are several possible circuit architectures regarding the measurement of a current. The most immediate method to implement a current-to-voltage converter is through a transimpedance amplifier with resistive feedback, as shown in fig. 3.1. The input current  $I_{in}$  is supposed to be of a single polarity, ie positive.

Figure 3.1: Transimpedance amplifier.

If we consider all components as ideal, in particular if we assume that the current source has no output capacitance, that the amplifier has a transfer function A(s) and that the input and output

resistance of the amplifier are, respectively, infinite and null, then the circuit may be studied with the linear network theory, as follows.

Under the stated hypothesis, the circuit has a shunt-shunt feedback. The forward gain is  $A_f(s) = -(R_s // R_f)A(s)^1$  and the feedback transfer function is  $\beta(s) = -R_s/(R_f + R_s)$ . The loop gain is hence:

$$G_{loop}(s) = A(s)\beta(s) = -A(s)R_s/(R_f + R_s)$$

(3.1)

The corresponding linear input-output characteristic is,<sup>2</sup>

$$\frac{V_o(s)}{I_{in}(s)} = \frac{A_f(s)}{1 - G_{loop}(s)} = -\frac{R_s R_f A(s)}{(1 + A(s))R_s + R_f}$$

(3.3)

In the following text, the closed-loop transfer function will be referred to as G(s).

From eq. 3.3, it is easily shown that for all angular frequencies for which  $|A(s)|_{s=j\omega} \gg -1/\beta$ , the input-output characteristic reduces to  $V_o = -R_f I_{in}$ .

The approximation is reasonable until a decade before the loop gain angular frequency, which is defined as the angular frequency  $\omega_p$  where:

$$|G_{loop}(s)|_{s=j\omega_p} = 1 (3.4)$$

Or, equivalently:

$$|A(s)|_{s=j\omega_p} = -1/\beta \tag{3.5}$$

$$\frac{V_o(s)}{I_{in}(s)} = -\frac{Z_f(s)}{1 + \frac{Z_s(s)/|Z_d(s) + Z_f(s)}{A(s)(Z_s(s))/|Z_d(s))}}$$

(3.2)

<sup>&</sup>lt;sup>1</sup>The operator // is here defined as:  $a \parallel b = ab/(a+b)$ .

<sup>&</sup>lt;sup>2</sup>The output resistance of a current source may be of the same order of magnitude of resistance  $R_d$  at input of the operational amplifier. In this case, the approximation  $R_d \approx +\infty$  no longer holds. To take it in account, it is possible to substitute  $R_s \parallel R_d$  to  $R_s$  in eq. 3.3. A more general equation that considers both the finite input resistance and the reactive part of the elements composing the circuit is the following, written in the standard form:

If the operational amplifier is internally compensated and its gain bandwidth product (GBW) is known, neglecting the effect of the other singularities, the loop gain angular frequency is equal to:

$$\omega_p = GBW \frac{R_s}{R_s + R_f} \approx GBW \tag{3.6}$$

if the value of the output resistance of the current source is much greater than the value of the feedback resistance,  $R_f$ .

Therefore, under the stated hypothesis, the circuit bandwidth doesn't depend on the gain. Furthermore, in the present discussion, we will assume that the bandwidth of the circuit may be selected independently from the gain of the amplifier.

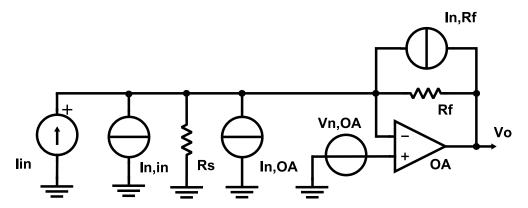

The circuit is redrawn in fig. 3.2 along with its noise sources: the Johnson-Nyquist noise of  $R_f$ ,  $i_{n,R_f}$ , the equivalent inverting current noise and voltage noise of the operational amplifier,  $v_{n,OA}$  and  $i_{n,OA}$  respectively and the input signal noise  $i_{n,in}$ .  $R_s$  is the equivalent output resistance of the source and may be dynamic. If this is the case, it doesn't have a thermal noise associated to it. In the present discussion, its noise is included in  $i_{n,in}$ . Other types of noises, such as flicker or burst noise, are not considered here.

The output noise is given by:

$$V_{o,n}(s) = -\frac{A(s)}{(1+A(s))R_s + R_f} \left[ R_s R_f \left( i_{n,in} + i_{n,OA} + i_{n,R_f} \right) + (R_s + R_f) v_{n,OA} \right]$$

(3.7)

Within the circuit bandwidth, where  $|G_{loop}(s)|_{s=j\omega} \gg 1$ , the previous expression reduces to:

$$V_{o,n}(s) = -R_f (i_{n,in} + i_{n,OA} + i_{n,R_f}) + \left(1 + \frac{R_f}{R_s}\right) v_{n,OA}$$

(3.8)

The amplifier shall be chosen so that it doesn't increase the magnitude of the overall output noise. For low minimum current applications, the op-amp must have low noise characteristics.

The maximum input current is determined by the amplifier saturation voltage, which are here supposed to be symmetric (ie  $V_{o,MAX} = -V_{o,MIN}$ ).

Figure 3.2: Transimpedance amplifier: noise sources.

Then:

$$I_{in,MAX} = \frac{V_{o,MAX}}{R_f} \tag{3.9}$$

Supposing that the output noise is due to the feedback resistor noise, the output voltage noise and its root mean square value are:

$$V_{o,n}(s) = -R_f i_{n,R_f} (3.10)$$

$$V_{o,n,rms} = R_f i_{n,R_f,rms} = \sqrt{4kTR_f B}$$

(3.11)

Where:

k is the Boltzmann's constant, equal to  $1.38 \times 10^{-23} \,\mathrm{J \, K^{-1}}$ .

T is the temperature in Kelvin degrees.

B is the equivalent single-sided noise bandwidth of the circuit [Hz], defined as,

$$B = \int_0^{+\infty} \left[ \frac{G(s)}{G(0)} \right]_{s=j\omega} \frac{d\omega}{2\pi}$$

(3.12)

The dynamic range is:

$$DR = \frac{I_{in,MAX}}{I_{in,MIN}} \tag{3.13}$$

Supposing the the minimum detectable amplitude of  $V_o$  corresponds to a SNR equal to 1, we have:

$$I_{in,MIN} = \frac{V_{o,n,rms}}{R_f} \tag{3.14}$$

And substituting, the DR can be expressed as:

$$DR = \frac{I_{in,MAX}}{V_{o,n,rms}/R_f} = \frac{V_{o,MAX}}{R_f} / \sqrt{\frac{4kTB}{R_f}} = \frac{V_{o,MAX}}{\sqrt{4kTR_fB}}$$

(3.15)

From which we get:

$$DR B = \frac{V_{o,MAX} I_{in,MIN}}{4kT}$$

(3.16)

Hence the dynamic range is inversely proportional to the circuit bandwidth, if we keep the minimum detectable current constant. [28]

This can be intuitively explained with the following argument: if we increase the circuit bandwidth,  $R_f$  has to be increased of the same factor to keep the minimum detectable current  $i_{n,R_f}$  constant. The amplifier will therefore saturate for a input current  $I_{in}$  which is a factor  $1/R_f$  lower. Hence, the dynamic range is reduced of the same factor, giving a constant DRB product.

For example, if  $|I_{in,MAX}| = 100 \text{ mA}$ , T = 300 K and  $V_{o,MAX} = 10 \text{ V}$ , requiring a dynamic range of 9 decades leads to a bandwidth of approximatively 60 Hz and  $R_f = 100 \Omega$ .

The maximum output voltage  $V_{o,MAX}$  may be increased changing the value of the supplies, on the other hand, this would increase the power dissipation of the circuit.

A different type of circuit is necessary for wideband high dynamic range measurements.

The possibilities to overcome the problem may be: taking into account the shape of the input signal to filter effectively the noise, thus reducing the minimum detectable signal, as described in chap. 4, using amplifiers with a compressive input-output characteristic (sect. 3.2, 3.3, 3.4, 3.5), multiple linear amplifiers selecting the desidered output (sect. 3.6) and converting the signal to a variable that is not affected by the limits the same limits of a voltage level (sect. 3.8).

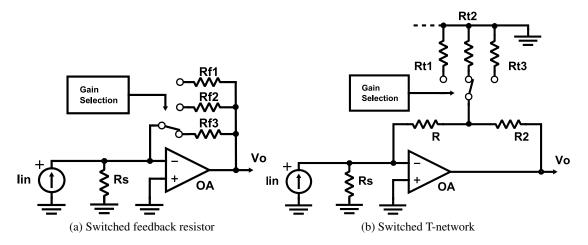

# 3.2 Transimpedance amplifier with switched gain

A direct extension of the circuit that has been previously considered can be obtained switching the feedback resistor according to the level of the input signal, as schematically illustrated in fig. 3.3a.

Figure 3.3: Transimpedance amplifiers with switchable gain: simplified schematic.

Once a feedback resistor is connected, the circuit is the same as the one considered in sect. 3.1. The stability of this configuration may be compromised by the stray capacitance due to the signal source and the input of the operational amplifier. [2]

The amplifer is therefore reviewed and greater emphasis is given to the stability issues. The circuit is shown in fig. 3.4.

Figure 3.4: Transimpedance amplifier with stray capacitances

The feedback transfer ratio is equal to:

$$\beta = -\frac{R_d \ /\!\!/ \ R_f \ /\!\!/ \ R_s}{R_f} \frac{1 + sC_f R_f}{1 + s(C_d + C_f + C_s)(R_d \ /\!\!/ \ R_f \ /\!\!/ \ R_s)}$$

(3.17)

The expressions for its characterstic values are as follows:

$$\beta(0) = -\frac{R_d /\!\!/ R_f /\!\!/ R_s}{R_f}$$

(3.18)

$$\omega_z = \frac{1}{C_f R_f} \tag{3.19}$$

$$\omega_p = \frac{1}{(C_d + C_f + C_s)(R_d /\!\!/ R_f /\!\!/ R_s)}$$

(3.20)

$$\lim_{\omega \to +\infty} \beta(s)|_{s=j\omega} = \frac{C_f}{C_d + C_f + C_s}$$

(3.21)

As  $C_s$  depends on the source and its connecting cables, it is not known exactly,  $C_f$  may be specified to ensure stability of the system, which shall be verified for every resistor composing the  $\{R_{fn}\}$  set. While increasing  $C_f$  is straightforward, decreasing it under the limit provided by the stray capacitance of the feedback resistor  $R_f$  requires special layout techniques. For example, replacing  $R_f$  with two resistors of half its value connected in series, assuming that the stray capacitance doesn't change, reduces the overall capacitance seen between input and output node of a factor two.

The phase margin is equalt to 45° for:

$$C_f = \frac{1 + \sqrt{1 + 4(C_d + C_s)GBWR_f}}{2GBWR_f}$$

(3.22)

The last result may be simplified to:

$$C_f = \sqrt{\frac{C_d + C_s}{GBWR_f}}, \quad for \quad 4(C_d + C_s)GBWR_f \gg 1$$

(3.23)

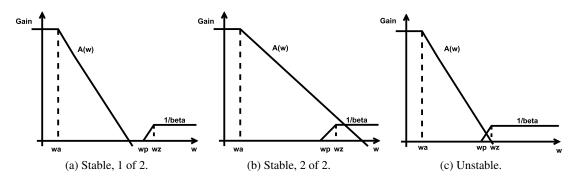

The result corresponds to the bode plot in fig. 3.5b, a case in which  $GBW > \omega_p$ ,  $\omega_z$  is shown in fig. 3.5a, while fig. 3.5c depicts an unstable configuration.

Figure 3.5: Noise gain for the transimpedance amplifier

A stable configuration has a transimpedance gain equal to:

$$\frac{V_o(s)}{I_{in}(s)} = Z_T(s) = -R_f \frac{A_0 \omega_a \omega_x}{s^2 + (\omega_p + \omega_a + \omega_a \frac{\omega_x}{\omega_z} A_0) s + \omega_a \omega_p + A_0 \omega_a \omega_x}$$

(3.24)

$A_0$  is the low frequency gain of the operational amplifier.

$\omega_{pa}$  is the angular frequency of the first pole of the transfer function of the operational amplifier [rad s<sup>-1</sup>]. Hence  $GBW = A_0\omega_a$

$\omega_x$  is equal to  $1/C_f(R_d \parallel R_f \parallel R_s)$ , [rad s<sup>-1</sup>]

Comparing eq. 3.24 to the canonical form for a second order system (3.25), we find:

$$T(s) = \frac{T_0}{s^2 + 2\xi\omega_n s + \omega_n^2}$$

(3.25)

$\omega_n$  natural frequency of the system:

$$\omega_n = \sqrt{A_0 \omega_a \omega_x} \tag{3.26}$$

$\xi$  damping factor:

$$\xi = \frac{1}{2} \left( \frac{\omega_p + \omega_a}{\omega_n} + \frac{\omega_n}{\omega_z} \right) \tag{3.27}$$

If the gain is considered infinite  $(A_0 \to +\infty)$ , then the transfer impedance  $Z_T(s)$  reduces to its ideal counterpart:

$$\lim_{A_0 \to +\infty} Z_T(s) = -\frac{R_f}{1 + sC_f R_f}$$

(3.28)

Which in turn reduces to the result found in sect. 3.1, if  $C_f$  is trascurable.

The output voltage due to DC errors is equal to:

$$V_o = (-I_{in} + I_b)R_f + V_{os} \left(1 + \frac{R_f}{R_s /\!\!/ R_d}\right)$$

(3.29)

$I_b$  is the input bias current of the operational amplifier. [A]

$V_{os}$  is the input offset voltage of the operational amplifier. [V]

A fundamental drawback of this solution is that high value resistors are required in order to provide high gain for low currents. For example, to have a 1 V output with a 1 nA current input, a 1  $G\Omega$  resistor is required. This kind of resistors are usually made from carbon film or deposit ceramic oxide, glass-sealed to prevent their value from changing because of humidity and are bulky and expensive.[52]

This problem is overcome by the transimpedance amplifier with a T-network feedback shown in fig. 3.3b.

It can be shown that the output voltage corresponding to a DC input, including the effect of the input voltage and the input bias current, is:

$$V_o = \left(-I_{in} + I_b + \frac{V_{os}}{R_s}\right) \left[R\left(1 + \frac{R_2}{R_{in}}\right) + R_2\right] + V_{os}$$

(3.30)

$R_{tn}$  is the selected resistor among those available for setting the gain. [ $\Omega$ ]

As some of the current is flowing towards ground, the sensitivity is augmented avoiding the usage of high-value resistors. From eq. 3.30, the transfer is linearly dependent on a term  $(1 + R_2/R_{tn})$ , hence decreasing  $R_{tn}$  provides an increased transimpedance gain. On the other hand, the circuit is affected by a higher noise gain and the loop gain is decreased. The contribution of the offset voltage, bias current and root mean value of the output voltage due to the input current and voltage noises are also linearly dependent on the same factor, deteriorating the DR.

These circuit architectures require a system to select the appropriate gain. An effortless solution is setting the gain beforehand according to the expected signal from each detector. The signal level expectations may be used to preset the configuration of the interface electronics, avoiding

Figure 3.6: Charge amplifier

output saturation. The dynamic range of each configuration is the same as previously considered for the transimpedance amplifier, only the maximum and minimum current are scaled according to the gain.

A more elaborate switching system may be implemented, so that the gain changes with the input signal level. This leads to several more difficulties: the input signal has edges with rising times of some tens of nanoseconds, which would require an equally fast gain switching. On the other hand, rapidly switching the gain value will produce spurious spikes at the output.

The output due to voltage offset and offset current at the input is variable, as the gain is. In addition, the stability depends on the gain configuration, each of them has to be stable.

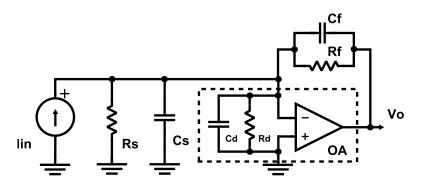

# 3.3 Charge amplifier

A charge amplifier<sup>3</sup> provides an output signal proportional to the electric charge produced by a device connected to its input. Its is intended to be used with a sensor that yields an output charge proportional to a measured physical quantity.

The schematic of a charge amplifier is the same as the one of the transimpedance amplifier shown in fig. 3.4, only in this case, the feedback capacitor is the element that provides the desidered functionality and  $R_f$  is composed by the shunt resistance of the capacitor (representing the leakage current) and any additional resistor added to ensure direct current stability.

Therefore, it is possible to analyze the stability of the circuit through the noise gain found in sect. 3.2.

<sup>&</sup>lt;sup>3</sup>In this section, the charge amplifier is considered in its simpler configuration, ie with a fixed integration capacitor. About the possibility of switching the capacitor to modify the gain, the remarks concerning the switching of the feedback resistor in a transimpedance amplifier apply.

From eq. 3.24, we can derive the closed loop transfer function Being  $I_{in} = Q'_{in}$ , applying the Laplace Transform to both sides we get:

$$\mathcal{L}(I_{in}(t))(s) = \mathcal{L}(Q'_{in}(t))(s) = s\mathcal{L}(Q_{in}(t))(s) = sQ_{in}(s)$$

(3.31)

Substituting in 3.24, we get:

$$\frac{V_o(s)}{Q_{in}(s)} = -\frac{1}{C_f} \frac{sA_0\omega_a \frac{\omega_x}{\omega_z}}{s^2 + (\omega_p + \omega_a + \omega_a \frac{\omega_x}{\omega_z} A_0)s + \omega_a \omega_p + A_0\omega_a \omega_x}$$

(3.32)

All the parameters are the same as those introduced in sect. 3.2.

The transfer function has two poles and a zero. If the two poles are distant from each other enough, the following approximation can be used to estimate their position: at low frequency eq. 3.32 simplifies to:

$$\frac{V_o(s)}{Q_{in}(s)} = -\frac{1}{C_f} \frac{sR_f C_f}{sC_f R_f + 1}$$

(3.33)

While at higher frequencies,

$$\frac{V_o(s)}{Q_{in}(s)} = -\frac{1}{C_f} \frac{A_0 \omega_a \frac{\omega_x}{\omega_z}}{s + (\omega_p + \omega_a + \omega_a \frac{\omega_x}{\omega_z} A_0)}$$

(3.34)

Therefore, the positions of the poles are approximatevely:

$$\omega_l \approx \frac{1}{C_f R_f} \tag{3.35}$$

$$\omega_h \approx \frac{GBW\omega_p}{\omega_z} \approx GBW \frac{C_f}{C_f + C_s + C_d}$$

(3.36)

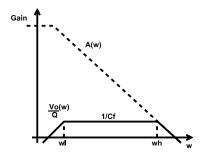

The gain between the two poles can be estimated as  $-1/C_f$ . Fig. 3.7 shows a bode plot of the transfer function, superimposed to the transfer function of the operational amplifier,  $A(\omega)$ .

The output due to the DC errors has the same expression as the one affecting the transimpedance amplifier (eq. 3.29).

Figure 3.7: Bode plot of the transfer function of a charge amplifier.

The output drift is a characteristic parameter of the charge sensitive amplifier and it takes into account the effect of the discharge of the feedback capacitor  $C_f$  through its leakage resistor,  $R_f$ , and the effect of the input bias current of the operational amplifier,  $I_b$  on the output. It is expressed by the following relationship:

$$OD = \frac{V_o}{C_f R_f} + \frac{I_b}{R_f} \tag{3.37}$$

The feedback capacitor  $C_f$  is a key element in this design. In order to obtain a large sensitivity,  $C_f$  should be kept small, but at the same time, reducing the feedback capacitor decreases  $\omega_h$  and increases  $\omega_l$ , deteriorating the transfer function and potentially undermining the stability of the circuit. To prevent gain drift,  $C_f$  should be as stable as possible. Moreover, it should be chosen among those who have a low leakage. Suitable dielectrics are polypropylene and polystyrene, for example.

To improve the stability of the circuit, the signal may be connected to the inverting input of the operational amplifier through a resistor. [2] The input resistor also protects the input, limiting the maximum current flowing into the charge amplifier when a voltage source is connected to the input. It introduces a pole at an angular frequency equal to:

$$\omega_{p1} \approx \frac{1}{C_s R_r} \tag{3.38}$$

$R_x$  is the resistor connected in series with the input.

This pole sets the high frequency limit, if  $\omega_{p1} < \omega_h$ .

A FET input operational amplifier should be used to reduce errors, since the input bias current of the operational amplifier is summed to the signal current.

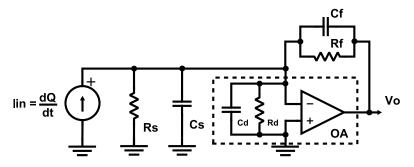

Figure 3.8: Alternative charge amplifier

A discrete resistor shunting the feedback capacitor may be omitted, but, in that case, a switch or another suitable reset mechanism should be included in the circuit to prevent saturation, as the already mentioned bias currents would drive the output voltage to one of the supply rails in absence of signal. When the feedback resistor is included, there is a trade-off between low frequency response – as  $R_f$  directly affects the position of  $\omega_l$  – and DC offset voltage at the output. A high-value resistor determines a large DC error at the output, while a low-value resistor moves the lower end of the transfer function to higher frequencies.

#### 3.3.1 Alternative implementations of a charge amplifier

An alternative charge amplifier is shown in fig. 3.8 [34]. This design has some key differences from the previous one: the feedback resistor  $R_f$  provides a DC path for the input bias current  $I_b$  without affecting the charge stored on the feedback capacitor  $C_f$ .

The transfer function is:

$$\frac{V_o(s)}{Q_{in}(s)} = -\frac{1}{C_f} \frac{sR_f C_a}{(1 + sR_a C_s) \left(1 + \frac{C_a}{C_f} + sR_f C_a\right) + \frac{C_s}{C_f}}$$

(3.39)

The location of the two poles may be approximated with the following expressions, if they are situated at a distance of at least one decade.

$$\omega_l \approx \frac{1}{\frac{C_a C_f}{C_a + C_f + C_s} R_f} \tag{3.40}$$

$$\omega_h \approx \frac{1}{R_a C_s} \tag{3.41}$$

Figure 3.9: Charge amplifier without virtual ground at the input.

In the range between  $\omega_l$  and  $\omega_h$ , the transfer function is  $1/C_f$ . Therefore, the introduction of  $R_a$  and  $C_a$  allows greater freedom in the independent choice of the frequency response and sensitivity.

Being AC coupled, the input of the amplifier is protected against DC overloads.

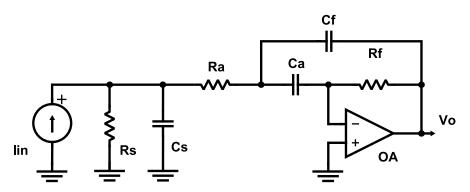

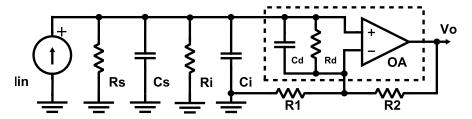

It is also possible to integrate passively the input current on a capacitor and the resulting voltage may be successively amplified through an amplifier with an high input resistance. This setup is shown in fig. 3.9.

Ideally, all the input current flows in  $C_i$  and it is integrated. The voltage across the integrating capacitor is the amplified of a factor  $G_{\nu}(s)$ , given by eq. 3.42, where the input resistance and capacitance of the operational amplifier are not taken into account. To provide a path for the input bias current,  $R_i$  has been added to the circuit.

$$G_{\nu}(s) = \left(1 + \frac{R_2}{R_1}\right) \frac{1}{1 + s/\omega_{pa}} \tag{3.42}$$

The pole can be shown to be:

$$\omega_{pa} = GBW \frac{R_1}{R_1 + R_2} \tag{3.43}$$

On the whole, the transfer function of the charge amplifier is:

$$\frac{V_o(s)}{Q_{in}(s)} = \frac{1}{C_i + C_s} \left( 1 + \frac{R_2}{R_1} \right) \frac{1}{1 + s/\omega_{pa}} \frac{s(R_i + R_s)(C_i + C_s)}{1 + s(R_i + R_s)(C_i + C_s)}$$

(3.44)

The stability of the operational amplifier is easily ensured and this design has potentially a very wide bandwidth, depending on the choice of the operational amplifier. On the other hand, this setup is more sensitive to the characteristics of the current source and the length of the cable. As it can be seen in eq. 3.44, the effective capacitance that integrates the input signal is composed

of the capacitor  $C_i$  and the cable and source capacitance  $C_s$ . Moreover, the lower frequency pole is also set by the the current source and therefore, a different source or a different cable length directly affects the gain.

#### 3.4 Amplifier with a nonlinear characteristic

An amplifier with a defined nonlinearity may also be employed; linear frequency independent input-output relationships arise from the use of components with a linear frequency independent characteristic at the input or in the feedback loop of an amplifier. As reactive componets produce frequency dependent relationships, nonlinear elements determine a nonlinear relationship.

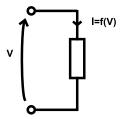

Figure 3.10: Nonlinear element.

Both compressive and expanding characteristics may be implemented – the former being suitable for our purposes – and the relationship may be an arbitrary or a well known mathematical function. Logarithmic amplifiers are considered in sect. 3.5.

Figure 3.11: Operational amplifier with nonlinear feedback path.

A key role is played by the element providing the required nonlinearity: it is required to adhere accurately to the ideal characteristic over a wide range of currents with low temperature sensitivity. Such components may be constituted by a single nonlinear component or by a network of linear and nonlinear elements, where the nonlinear elements are used as switches.

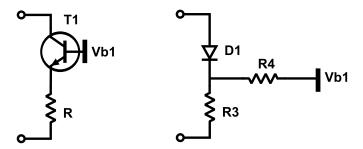

Figure 3.12: Possible building blocks for nonlinear feedback networks

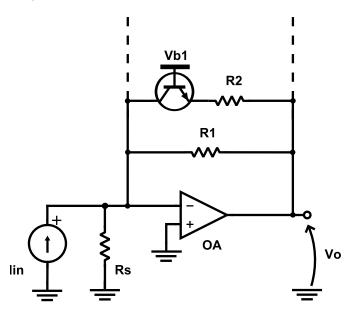

Two examples of networks of the latter type are shown in figure 3.12. Referring to the right-hand figure, the external bias voltage and the resistor set the voltage required to turn on the diode. A very similar results may be achieved with a network based on a bipolar transistor, as seen in the left-hand figure.

Figure 3.13: Nonlinear amplifier using the network shown in fig. 3.12

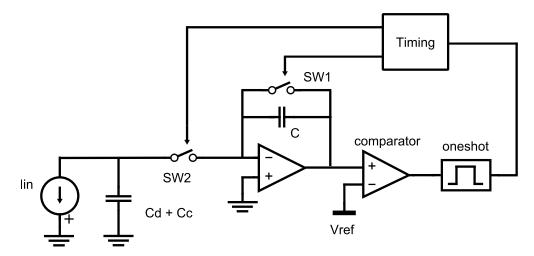

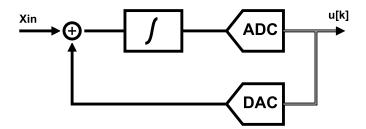

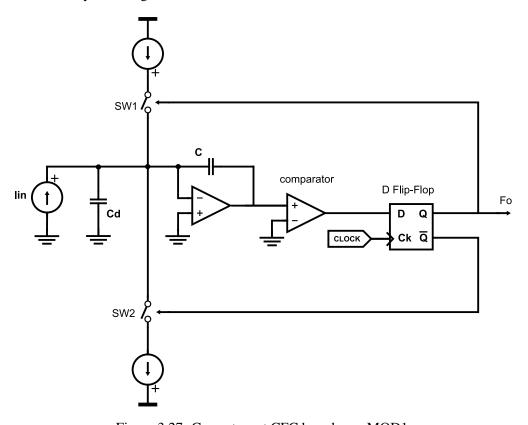

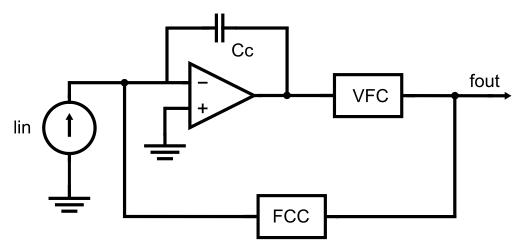

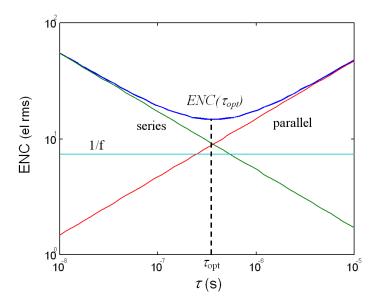

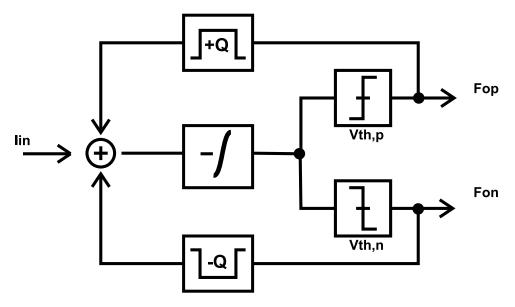

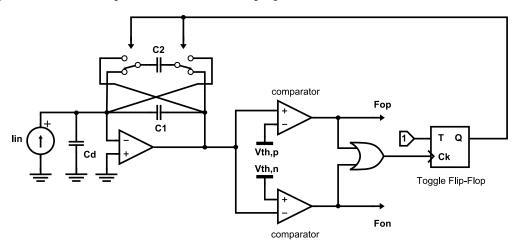

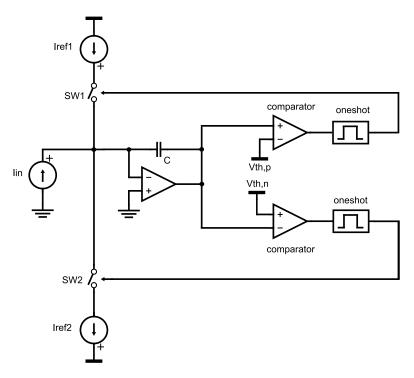

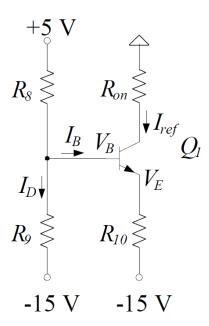

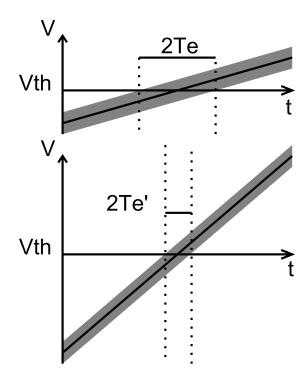

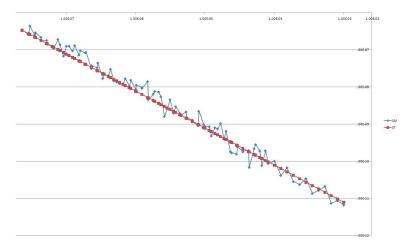

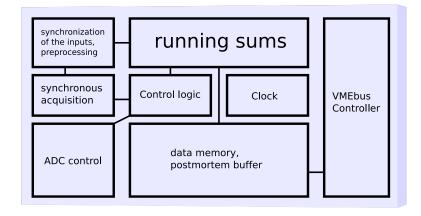

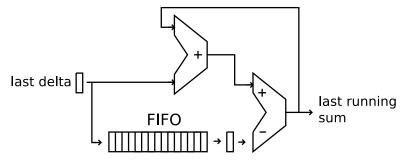

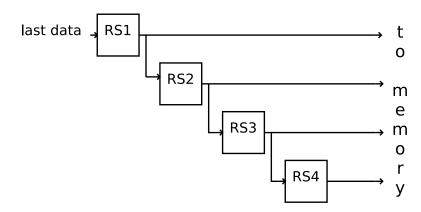

A nonlinear amplifier is depicted in fig. 3.13. The ideal characteristic shows a transconductance gain equal to  $R_1$  until the output reaches  $V_{bi} - V_{BE}$ , where  $V_{BE}$  is the approximative forward bias required to turn on the diode, after that the gain is  $R_1 \ /\!/ R_2$ . The same happens for the successive breakpoints.