Ash for find vessan!

Tests of the SCT Front-end Chip of the ATLAS Detector at the Large Hadron Collider

Thesis for the degree of Master of Science in Physics

Supervisor: prof. Allan Clark Jury: prof. Maria Kienzle Candidate: András Zsenei<sup>1</sup>

Presented on the  $14^{th}$  of August 1998 at the Department of Physics of the Geneva University

ر+ (535) 1998-Zsene

<sup>1</sup>Andras.Zsenei@cern.ch

CERN LIBRARIES, GENEVA

CM-P00065797

## Contents

| 1 | Intr                            | oducti                                                                        | on                                         | 5                                                  |  |  |  |  |  |  |  |

|---|---------------------------------|-------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|

| 2 | Phy                             | sics in                                                                       | ATLAS                                      | 7                                                  |  |  |  |  |  |  |  |

|   | 2.1                             | iew of the experimental apparatus                                             | 7                                          |                                                    |  |  |  |  |  |  |  |

|   |                                 | 2.1.1                                                                         | The Large Hadron Collider (LHC)            | 7                                                  |  |  |  |  |  |  |  |

|   |                                 | 2.1.2                                                                         | ATLAS                                      | 7                                                  |  |  |  |  |  |  |  |

|   |                                 | 2.1.3                                                                         | The Inner Detector                         | 9                                                  |  |  |  |  |  |  |  |

|   | 2.2                             | Theor                                                                         | etical overview                            | 12                                                 |  |  |  |  |  |  |  |

|   |                                 | 2.2.1                                                                         | The Standard Model                         | 12                                                 |  |  |  |  |  |  |  |

|   |                                 | 2.2.2                                                                         | CP-violation                               | 12                                                 |  |  |  |  |  |  |  |

|   |                                 | 2.2.3                                                                         | The Cabibbo Angle                          | 14                                                 |  |  |  |  |  |  |  |

|   |                                 | 2.2.4                                                                         | Generalization to three doublets           | 16                                                 |  |  |  |  |  |  |  |

|   |                                 | 2.2.5                                                                         | The unitarity triangle                     | 18                                                 |  |  |  |  |  |  |  |

|   | 2.3                             | B phy                                                                         | sics in ATLAS                              | 22                                                 |  |  |  |  |  |  |  |

|   |                                 | 2.3.1                                                                         | CP-violation in ATLAS                      | 22                                                 |  |  |  |  |  |  |  |

| 3 | The Semiconductor Tracker (SCT) |                                                                               |                                            |                                                    |  |  |  |  |  |  |  |

|   |                                 | 3.0.2                                                                         | Detectors                                  | 30                                                 |  |  |  |  |  |  |  |

|   |                                 |                                                                               |                                            |                                                    |  |  |  |  |  |  |  |

|   |                                 | 3.0.3                                                                         | Electronics                                | 31                                                 |  |  |  |  |  |  |  |

|   |                                 | $3.0.3 \\ 3.0.4$                                                              | Electronics                                | 31<br>31                                           |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4                                                                         |                                            |                                                    |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4                                                                         | Modules                                    | 31                                                 |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4<br>Modul                                                                | Modules                                    | $\frac{31}{32}$                                    |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4<br>Modul<br>3.1.1                                                       | Modules          les          Introduction | 31<br>32<br>32                                     |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4<br>Modul<br>3.1.1<br>3.1.2                                              | Modules                                    | 31<br>32<br>32<br>32                               |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4<br>Modul<br>3.1.1<br>3.1.2<br>3.1.3                                     | Modules                                    | 31<br>32<br>32<br>32<br>32                         |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4<br>Modul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                            | Modules                                    | 31<br>32<br>32<br>32<br>32<br>33                   |  |  |  |  |  |  |  |

|   | 3.1                             | 3.0.4<br>Modul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6          | Modules                                    | 31<br>32<br>32<br>32<br>32<br>33<br>35             |  |  |  |  |  |  |  |

|   |                                 | 3.0.4<br>Modul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6          | Modules                                    | 31<br>32<br>32<br>32<br>32<br>33<br>35<br>35       |  |  |  |  |  |  |  |

|   |                                 | 3.0.4<br>Modul<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>Reado | Modules                                    | 31<br>32<br>32<br>32<br>32<br>33<br>35<br>35<br>36 |  |  |  |  |  |  |  |

4 CONTENTS

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2       The road of the data       48         4.2.1       Commands       51         4.2.2       The calibration logic       52         5       Testing       55         5.1       Introduction       55         5.1.1       What was measured       55         5.1.2       Overview of the measurements       56         5.2       Tests involving a single chip on a PCB-board       56         5.2.1       The setup       56         5.2.2       Testing the basic functionalities of the chip       62         5.2.3       Preamplifier and shaper bias dependance – what went wrong       68         5.3       Testing a single chip with a baby-detector connected to it       78 |

| 4.2       The road of the data       48         4.2.1       Commands       51         4.2.2       The calibration logic       52         5       Testing       55         5.1       Introduction       55         5.1.1       What was measured       55         5.1.2       Overview of the measurements       56         5.2       Tests involving a single chip on a PCB-board       56         5.2.1       The setup       56         5.2.2       Testing the basic functionalities of the chip       62         5.2.3       Preamplifier and shaper bias dependance – what went wrong       68         5.3       Testing a single chip with a baby-detector connected to it       78 |

| 4.2.1 Commands       51         4.2.2 The calibration logic       52         5 Testing       55         5.1 Introduction       55         5.1.1 What was measured       55         5.1.2 Overview of the measurements       56         5.2 Tests involving a single chip on a PCB-board       56         5.2.1 The setup       56         5.2.2 Testing the basic functionalities of the chip       62         5.2.3 Preamplifier and shaper bias dependance – what went wrong       68         5.3 Testing a single chip with a baby-detector connected to it       73                                                                                                                   |

| 4.2.2 The calibration logic       52         5 Testing       55         5.1 Introduction       55         5.1.1 What was measured       55         5.1.2 Overview of the measurements       56         5.2 Tests involving a single chip on a PCB-board       56         5.2.1 The setup       56         5.2.2 Testing the basic functionalities of the chip       62         5.2.3 Preamplifier and shaper bias dependance – what went wrong       68         5.3 Testing a single chip with a baby-detector connected to it       73                                                                                                                                                   |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.1.1 What was measured                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.1.2 Overview of the measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.2 Tests involving a single chip on a PCB-board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.2.1 The setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

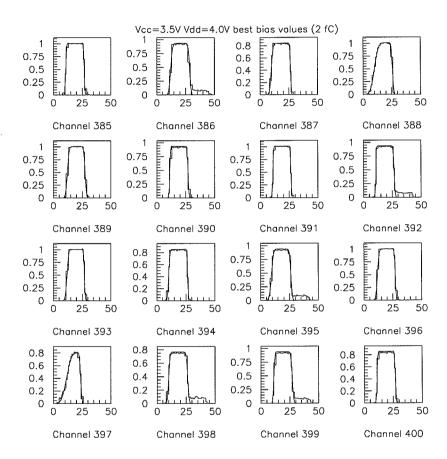

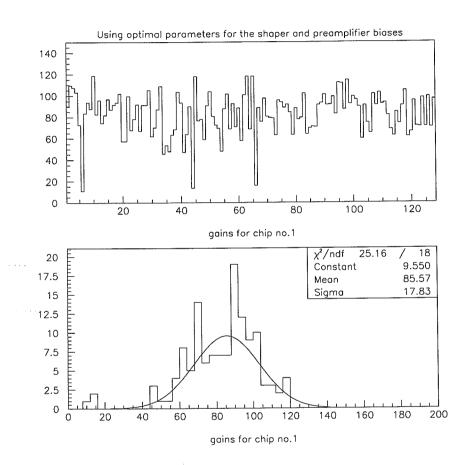

| 5.2.2 Testing the basic functionalities of the chip 62 5.2.3 Preamplifier and shaper bias dependance – what went wrong 68 5.3 Testing a single chip with a baby-detector connected to it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.2.3 Preamplifier and shaper bias dependance – what went wrong 68 5.3 Testing a single chip with a baby-detector connected to it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

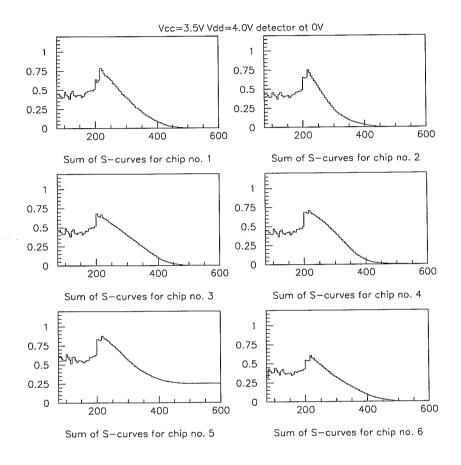

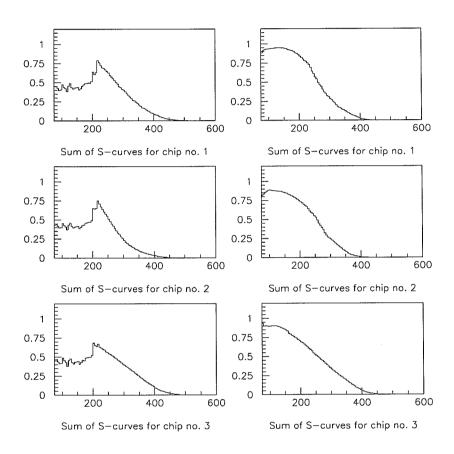

| 5.3 Testing a single chip with a baby-detector connected to it 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| o.o results a single comp with a say accepted composed to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

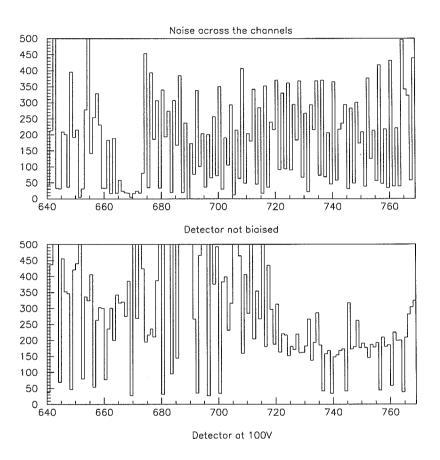

| 5.4 Module testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.4.1 The setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.4.2 Tests without the detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.4.3 Measurements with the detector connected 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.5 Conclusions of the tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6 Conclusions 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7 Appendix 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

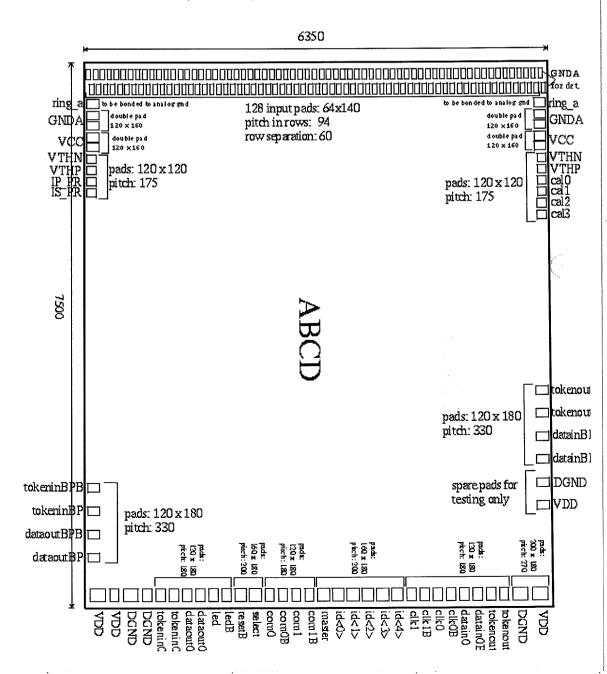

| .1 Pinout of the ABCD chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .2 Slow control commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| .3 DC supply and control characteristics of the ABCD chip 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| .4 Oslo-hybrid layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| .4 Osio-nybita tayout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| abstract and acknowledgements to be written maybe list of figures, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## Chapter 1

## Introduction

In 1994 the European Organization for Nuclear Research (CERN) approved the construction of the Large Hadron Collider (LHC), a new proton-proton (pp) collider with a center of mass energy of 14 TeV, which is planned to be operational in the year 2005.

Four experiments are currently planned for LHC. Two of them, ATLAS (A Toroidal LHC ApparatuS) and CMS are general purpose pp experiments and are designed to fully exploit the discovery potential of the LHC. The third experiment, LHC-B is dedicated to B-physics. While the fourth one, ALICE will explore heavy ion physics.

The ATLAS detector optimization is guided by physics issues such as sensitivity to the largest possible Higgs mass range. Other important goals are the investigation of CP violation in B-decays, the searches for heavy W- and Z-like objects, for supersymmetric particles, for compositeness of the fundamental fermions, as well as detailed studies of the top quark. The ability to cope well with a broad variety of possible physics processes is expected to maximize the detector's potential for the discovery of new, unexpected physics.

The ATLAS detector consists of several parts. These are the Inner Detector (ID), the different calorimeters (Hadronic Tile, EM Accordion, Forward LAr and Hadronic LAr End Cap Calorimeters), and the Muon Sectrometer. The work presented here concerns the readout of the Silicon Tracker (SCT) of the Inner Detector of ATLAS. As the detector will operate at very high luminosities (10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>), this puts very serious demands on the performance of the detectors in LHC. In order to fully take advantage of the this high luminosity, new electronics systems have been developed. They must be reliable, accurate and efficient in order to survive in the SCT environement for several years. One of them is the ABCD readout chip. The aim of this paper is to present the tests performed on this chip, in order to see if its performance meets the requirements.

After this introduction chapter 1 will describe the ATLAS detector with emphasis on the ID. It will also introduce the basic elements of particle physics and the physics which will be studied in ATLAS, especially B-physics. Chapter 3 will concentrate on the Silicon Tracker (SCT) of the Inner Detector, its

structure, its modules. The design of the readout chip ABCD will be presented in chapter 4. Chapter 5 is devoted to the measurements carried out to test and better understand the ABCD chip. Finally, chapter 6 gives a conclusion to the work that has been done.

## Chapter 2

## Physics in ATLAS

#### 2.1 Overview of the experimental apparatus

#### 2.1.1 The Large Hadron Collider (LHC)

The Large Hadron Collider, which is being built at CERN, represents the next generation of colliders. It will be installed in the 27~km tunnel where the LEP collider is located, and should be operational in 2005. It will be a proton-proton collider capable of producing collisions with a total collision energy of 14~TeV and luminosity of  $10^{34}~cm^{-2}~s^{-1}$ . The LHC will use the existing accelerators for the injection of the particles. Since the LHC will be colliding beams of particles with identical charge two separate beam-lines are necessary in order to allow the two proton beams to circulate in opposite directions. The frequency of bunch-crossing will be 40~MHz.

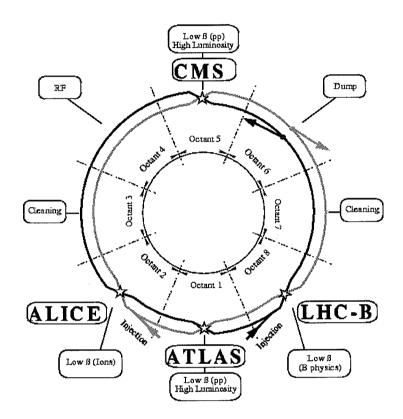

There will be 4 interaction points, and as many experiments. Two of them, ATLAS (A Toroidal LHC ApparatuS) and CMS are general purpose pp experiments and are designed to fully exploit the discovery potential of the LHC. The third experiment, LHC-B is dedicated to B-physics. While the fourth one, ALICE will explore heavy ion physics.

#### 2.1.2 ATLAS

The ATLAS¹ Collaboration proposes to build a general-purpose pp detector which is designed to exploit the full discovery potential of the LHC.

The LHC offers a large range of physics opportunities, among which the origin of mass at the electroweak scale is a major focus of interest for ATLAS. The detector optimization is therefore guided by physics issues such as sensitivity to the largest possible Higgs mass range. Other important goals are the investigation of CP violation in B-decays, the searches for heavy W- and Z-like objects, for supersymmetric particles, for compositeness of the fundamental

<sup>&</sup>lt;sup>1</sup>A Toroidal LHC ApparatuS

Figure 2.1: Experiments at the LHC

fermions, as well as detailed studies of the top quark. The ability to cope well with a broad variety of possible physics processes is expected to maximize the detector's potential for the discovery of new, unexpected physics.

Many of the interesting physics questions at the LHC require high luminosity, and so the primary goal is to operate at high luminosity ( $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>) with a detector that provides as many signatures as possible using electron, gamma, muon, jet, and missing transverse energy measurements, as well as b-quark tagging. The variety of signatures is considered to be important in the high-rate environment of the LHC in order to achieve robust and redundant physics measurements with the ability of internal cross-check.

Emphasis is also put on the performance necessary for the physics accessible during the initial lower luminosity running  $(10^{33} \text{ cm}^{-2} \text{ s}^{-1})$ , using more complex signatures such as tau-lepton detection and heavy-flavour tags from secondary vertices.

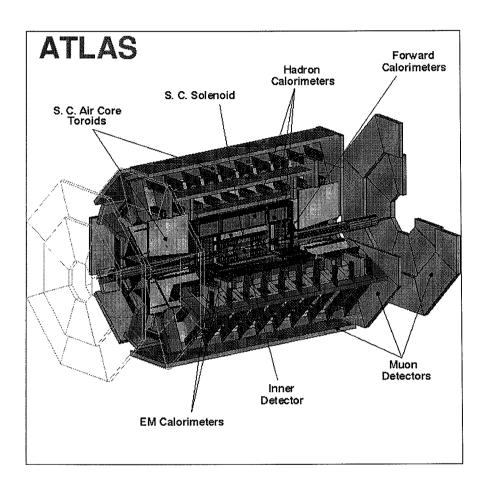

The overall layout of the detector is presented on fig. 2.2. It is approximately  $35\ m$  long and its radius is around  $10\ m$ . It consists of three sub-systems: muon spectrometer, calorimeters and the Inner Detector. The primary goal of the first one is to identify heavy quark events with prompt muon and produce a trigger essential for all heavy quark studies. The second will provide a good electromagnetic calorimetry for the identification and measurement of photons and electrons, and accurate jet and missing transverse energy measurements. The third sub-system is the theme of the next section.

#### 2.1.3 The Inner Detector

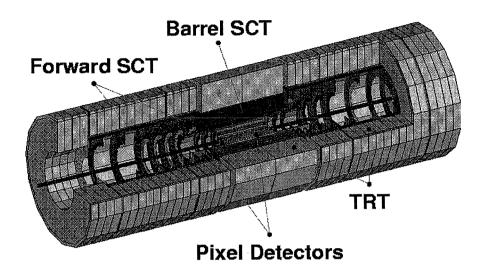

The purpose of the Inner Detector is to make high-precision measurements of the kinematic parameters of charged tracks with maximum capability for pattern recognition, particle identification and triggering. In order to maximise the capability for resolving the inevitable ambiguities caused by overlapping tracks, secondary interactions and detector inefficiencies, it is desirable to make a large number of measurements along the track. A combination of high-precision "discrete" (i.e. few point) and low-precision "continuous" (i.e. many point) tracking will offer the best possible track finding and track fitting capabilities. The discrete tracking will be provided by the silicon pixel and strip detectors at radii close to the beam axis. Silicon strip detectors come in two configurations: barrel silicon tracker and forward silicon tracker. The difference between strips and pixels is mainly geometric, pixels being closely spaced pads capable of good two dimensional reconstruction, while strips give better spatial resolution in one coordinate than the other. Pixels are also more resistant concerning the radiation damage, so they are placed closer to the beam. The continuous tracking will be provided by straw drift tubes situated at higher radii. The Semiconductor Tracker will be described in greater detail in chapter 3.

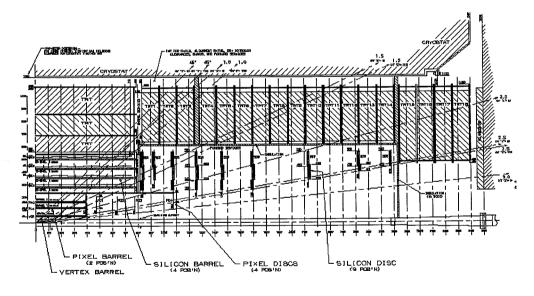

Figure 2.2: Cross-section of the ATLAS detector

Figure 2.3: The Inner Detector of ATLAS (fig 1-i)

Figure 2.4: Cross section of the Inner Detector along the beam axis (fig1-1)  $\,$

| Quarks           | d      | u       | S     | ¢          | b    | t,          |

|------------------|--------|---------|-------|------------|------|-------------|

| Mass $(GeV/c^2)$ | 0.008  | 0.004   | 0.15  | 1.2        | 4.7  | 170         |

| Charge           | -1/3   | +2/3    | -1/3  | +2/3       | -1/3 | +2/3        |

| Leptons          | e      | $ u_e $ | $\mu$ | $ u_{\mu}$ | au   | $\nu_{	au}$ |

| Mass             | 0.0005 | 0       | 0.105 | 0          | 1.8  | 0           |

| Charge           | -1     | 0       | -1    | 0          | -1   | 0           |

Table 2.1: Main properties of the fermions

#### 2.2 Theoretical overview

#### 2.2.1 The Standard Model

The experimental and theoretical developments of the last 50 years have led to the development of the Standard Model (SM) of particle physics. Since it is described in great detail in many textbooks, the discussion given here will be brief.

The most important concept of the modern fundamental physics is that of symmetry. Noether's theorem states that to every symmetry corresponds a conserved quantity. For example invariance under translations, time displacements, rotations and Lorentz transformations leads to the conservation of momentum, energy, and angular momentum. Apart from the discrete symmetries, like the ones just mentioned, there are also local gauge symmetries: the phase variation permitted by a local symmetry is reconciled by a field which is considered to be the mediator of interactions between matter particles. The Standard Model describes the fundamental particles and their interactions via three of the four known forces: electromagnetic, weak and strong. The gravity is negligeably small at particle level and is not described by the SM.

The SM has three types of particles:

- fermions which are the matter particles and have spin  $\frac{1}{2}$

- bosons which represent the interactions between fermions and have spin 1

- Higgs-boson which is a consequence of the spontaneous symmetry breaking, and has spin 0

The main properties of the fermions are summarized in table 2.1

#### 2.2.2 CP-violation

Not all symmetries are conserved by all interactions. The weak interactions are not invariant under the parity transformation P; the cleanest evidence for this is the fact that the antimuon emitted in pion decay

$$\pi^+ \to \mu^+ + \nu_\mu \tag{2.1}$$

Figure 2.5: Diagram responsible for  $K^0 \leftrightarrow \overline{K}^0$  mixing

always is produced left-handed. Nor are the weak interactions invariant under C, for the charge-conjugated version of reaction 2.1 would be

$$\pi^- \to \mu^- + \overline{\nu}_{\mu} \tag{2.2}$$

with a left-handed muon, whereas in fact the muon is always produced with a right-handed helicity. However, combining the two operations gives a true picture: CP turns the left-handed anti-muon into a right-handed muon, which is exactly what is observed in nature. The parity transformation was replaced by CP as the one believed to be conserved.

As it turned out to be, once again the intuition was false. The contradiction of this belief came from the neutral K mesons. The  $K^0$ , with strangeness +1, can turn into its antiparticle  $\overline{K}_0$ , strangeness -1

$$K^0 \leftrightarrow \overline{K}^0$$

(2.3)

through a second-order weak interaction represented by the diagram in figure 2.5  $^2$ . As a result, the particles that are normally observed in the laboratory are not  $K^0$  and  $\overline{K}_0$ , but rather some linear combination of the two. In particular, eigenstates of CP can be formed, as follows. Because the K's are pseudoscalars

$$P|K^{0}> = -|K^{0}>, P|\overline{K}^{0}> = -|\overline{K}^{0}>$$

(2.4)

on the other hand, from

$$C|p\rangle = |\overline{p}\rangle \tag{2.5}$$

$$C|K^0>=|\overline{K}^0>, \quad C|\overline{K}^0>=|K^0>$$

(2.6)

Accordingly

$$CP|K^0> = -|\overline{K}^0>, \quad CP|\overline{K}^0> = -|K^0>$$

(2.7)

and hence the normalized eigenstates of CP are

$$|K_1> = (1/\sqrt{2})(|K^0> -|\overline{K}^0>)$$

and  $|K_2> = (1/\sqrt{2})(|K^0> +|\overline{K}^0>)$  (2.8)

with

$$CP|K_1>=|K_1> \quad and \quad CP|K_2>=-|K_2>$$

(2.9)

Assuming CP is conserved in the weak interactions,  $K_1$  can only decay into a state with CP = +1, whereas  $K_2$  must go to a state with CP = -1. Typically, neutral kaons decay into two or three pions. The two-pion configuration carries

<sup>&</sup>lt;sup>2</sup>????see griffiths

a parity of +1, and three pion system has P=-1; both have C=+1. So the  $K_1$  decays into two pions (never three);  $K_2$  decays into three pions (never two):

$$K_1 \to 2\pi, \quad K_2 \to 3\pi$$

(2.10)

Now, the  $2\pi$  decay is much faster, because the energy released is greater. So if initially the beam consists of  $K^0$ 's

$$|K^{0}\rangle = (1/\sqrt{2})(|K_{1}\rangle + |K_{2}\rangle)$$

(2.11)

the  $K_1$  component will quickly decay away, and down the line the beam should contain only  $K_2$ 's. Near the source there should be a lot of  $2\pi$  events, but farther along only  $3\pi$  decays are expected.

Experimentally the two lifetimes are

$$\tau_1 = 0.89 \times 10^{-10} sec \tag{2.12}$$

$$\tau_2 = 5.2 \times 10^{-8} sec \tag{2.13}$$

so the  $K_1$  's are mostly decayed after a few centimeters, whereas the  $K_2$ 's can travel many meters.

The neutral kaons provide a perfect experimental system for testing CP invariance. By using a sufficiently long beam, it is possible to produce an arbitrarily pure sample of the long-lived species. If at this point a  $2\pi$  decay is observed, CP has been violated. Such an experiment was reported by Cronin and Fitch in 1964. At the end of a beam 57 feet long, they found 45 two-pion events in a total of 22700 decays. That's a tiny fraction, but unmistakable evidence of CP violation. Evidently the long-lived neutral kaon is not a perfect eigenstate of CP after all, but contains a small admixture of  $K_1$ :

$$|K_L> = \frac{1}{\sqrt{1+|\epsilon|^2}}(|K_2> + \epsilon|K_1>)$$

(2.14)

The coefficient  $\epsilon$  is a measure of nature's departure from perfect CP invariance; experimentally its magnitude is about  $2.3 \times 10^{-3}$ .

#### 2.2.3 The Cabibbo Angle

CP violation can be parametrised (though not explained) by means of a phase in the Cabbibo-Kobayashi-Maskawa (CKM) matrix. In the following the CKM formalism is introduced. Leptons and quarks participate in weak interactions through charged V-A currents constructed from the following pairs of (left-handed) fermion states:

$$\begin{pmatrix} \nu_e \\ e^- \end{pmatrix}, \quad \begin{pmatrix} \nu_\mu \\ \mu^- \end{pmatrix}, \quad and \quad \begin{pmatrix} u \\ d \end{pmatrix}$$

(2.15)

All these charged currents couple with a universal coupling constant G. It is natural to extend this uiversality to embrace the doublet

$$\begin{pmatrix} c \\ s \end{pmatrix} \tag{2.16}$$

Figure 2.6: The decay  $K^+ \to \mu^+ \nu_\mu$  HAL12.16

formed from heavier quark states. However this cannot be quite correct. For instance, the decay  $K^+ \to \mu^+ \nu_\mu$  occurs, so there must be a weak current which couples a u to an  $\overline{s}$  quark (see fig. 2.6). This contradicts the above scheme which only allows weak transition between  $u \leftrightarrow d$  and  $c \leftrightarrow s$ .

Instead of introducing new couplings to accommodate observations like  $K^+ \to \mu^+\nu_\mu$ , it is more elegant to keep universality but modify the quark doublets. Assuming that the charged current couples "roated" quark states

$$\begin{pmatrix} u \\ d' \end{pmatrix}, \begin{pmatrix} c \\ s' \end{pmatrix}, ...,$$

(2.17)

where

$$d' = d\cos\theta_c + s\sin\theta_c \tag{2.18}$$

$$s' = -d\sin\theta_c + s\cos\theta_c \tag{2.19}$$

This introduces an arbitrary parameter  $\theta_c$ , the quark mixing angle, known as he Cabibbo angle. Cabibbo first introduced the doublet u,d' to account for the weak decays of strange particles. Indeed, the mixing of the d and s quark can be determined by comparing  $\Delta S=1$  and  $\Delta S=0$  decays. For example

$$\frac{\Gamma(K^+ \to \mu^+ \nu_\mu)}{\Gamma(\pi^+ \to \mu^+ \nu_\mu)} \sim \sin^2 \theta_c \tag{2.20}$$

After taking into account the kinematic factors arising from the different particle masses, the data show that the  $\Delta S=1$  transitions are suppressed by a factor of about 20 as compared to the  $\Delta S=0$  transitions. This corresponds to a Cabibbo angle  $\theta_{\rm c}\approx 13^{\rm o}$

So instead of the simplistic charged current now there are "Cabibbo favored" transitions (proportional to  $\cos\theta_c$ ) and "Cabibbo suppressed" ones and similar diagrams for the charge-lowering transitions.

It is possible to summarize the above scheme as follows. The charged (or flavor-changing) current couples  $u \leftrightarrow d'$  states or  $c \leftrightarrow s'$  (left-handed) quark states, where d' and s' are orthogonal combinations of the physical (i.e., mass) eigenstitates of quarks of definite flavor d, s:

$$\begin{pmatrix} d' \\ s' \end{pmatrix} = \begin{pmatrix} \cos \theta_c & \sin \theta_c \\ -\sin \theta_c & \cos \theta_c \end{pmatrix} \begin{pmatrix} d \\ s \end{pmatrix}$$

(2.21)

The quark mixing is described by a single parameter, the Cabibbo angle.

#### 2.2.4 Generalization to three doublets

Now consider the generalization of the Cabibbo-GIM ideas to more than four quark flavors. Imagine for a moment that weak ineractions operate on N doublets of left-handed quarks,

$$\begin{pmatrix} u_i \\ d'_i \end{pmatrix} \quad with \quad i = 1, 2, ..., N$$

(2.22)

where  $d_i'$  are mixtures of he mass eigenstates  $d_i$ :

$$d_i' = \sum_{j=1}^{N} U_{ij} d_j \tag{2.23}$$

U is a unitary  $N \times N$  matrix to be determined by the flavor-changing weak process. How many observable parameters does U contain? We can change the phase of each of the 2N quark states independently without altering the physics. Therefore U contains

$$N^2 - (2N - 1) \tag{2.24}$$

real parameters. One phase is omitted as an overall phase change still leaves U invariant. On the other hand, an orthogonal  $N \times N$  matrix has only  $\frac{1}{2}N(N-1)$  real parameters. Therefore, by redefining the quark phases, itt is not possible, in general, to make U real. U must contain

$$N^{2} - (2N - 1) - \frac{1}{2}N(N - 1) = \frac{1}{2}(N - 1)(N - 2)$$

(2.25)

residual phase factors. Thus, for we doublets (N=2), there is one real parameter  $(\theta_c)$ , whereas for three doublets, there are three real parameters and one phase factor,  $e^{i\delta}$ . This phase leading to an imaginary part of the CKM matrix is a necessary ingredient to describe CP violation within the framework of the Standard Model.

The matrix that connects the weak eigenstates (d', s', b') and the corresponding mass eigenstates d, s, b is

$$\begin{pmatrix} d' \\ s' \\ b' \end{pmatrix} = \begin{pmatrix} V_{ud} & V_{us} & V_{ub} \\ V_{cd} & V_{cs} & V_{cb} \\ V_{td} & V_{ts} & V_{tb} \end{pmatrix} \begin{pmatrix} d \\ s \\ b \end{pmatrix}$$

(2.26)

Let us introduce the notation  $c_{ij} = \cos \theta_{ij}$  and  $s_{ij} = \sin \theta_{ij}$  with i and j being generation labels (i, j = 1, 2, 3). The standard parametrization is then given as follows [8]:

$$V = \begin{pmatrix} c_{12}c_{13} & s_{12}c_{13} & s_{13}e^{-i\delta} \\ -s_{12}c_{23} - c_{12}s_{23}s_{13}e^{i\delta} & c_{12}c_{23} - s_{12}s_{23}s_{13}e^{i\delta} & s_{23}c_{13} \\ s_{12}s_{23} - c_{12}c_{23}s_{13}e^{i\delta} & -s_{23}c_{12} - s_{12}c_{23}s_{13}e^{i\delta} & c_{23}c_{13} \end{pmatrix}, (2.27)$$

where  $\delta$  is the phase necessary for CP violation.  $c_{ij}$  and  $s_{ij}$  can all be chosen to be positive and  $\delta$  may vary in the range  $0 \le \delta \le 2\pi$ . However, the measurements of CP violation in K decays force  $\delta$  to be in the range  $0 < \delta < \pi$ .

The extensive phenomenology of the last years has shown that  $s_{13}$  and  $s_{23}$  are small numbers:  $\mathcal{O}(10^{-3})$  and  $\mathcal{O}(10^{-2})$ , respectively. Consequently to an excellent accuracy  $c_{13} = c_{23} = 1$  and the four independent parameters are given as

$$s_{12} = |V_{us}|, \quad s_{13} = |V_{ub}|, \quad s_{23} = |V_{cb}|, \quad \delta$$

(2.28)

with the phase  $\delta$  extracted from CP violating transitions or loop processes sensitive to  $|V_{td}|$ . The latter fact is based on the observation that for  $0 \le \delta \le \pi$ , as required by the analysis of CP violation in the K system, there is a one-to-one correspondence between  $\delta$  and  $|V_{td}|$ .

For numerical evaluations the use of the standard parametrization is strongly recommended. However once the four parameters in (2.28) have been determined it is often useful to make a change of basic parameters in order to see the structure of the result more transparently. This brings us to the Wolfenstein parametrization.

The original Wolfenstein parametrization is an approximate parametrization of the CKM matrix in which each element is expanded as a power series in the small parameter  $\lambda = |V_{us}| = 0.22$ ,

$$V = \begin{pmatrix} 1 - \frac{\lambda^2}{2} & \lambda & A\lambda^3(\varrho - i\eta) \\ -\lambda & 1 - \frac{\lambda^2}{2} & A\lambda^2 \\ A\lambda^3(1 - \varrho - i\eta) & -A\lambda^2 & 1 \end{pmatrix} + \mathcal{O}(\lambda^4), \qquad (2.29)$$

and the set (2.28) is replaced by

$$\lambda, \quad A, \quad \varrho, \quad \eta.$$

(2.30)

The Wolfenstein parameterization has several nice features. In particular it offers in conjunction with the unitarity triangle a very transparent geometrical representation of the structure of the CKM matrix and allows the derivation of several analytic results to be discussed below. This turns out to be very useful in the phenomenology of rare decays and of CP violation.

When using the Wolfenstein parametrization one should keep in mind that it is an approximation and that in certain situations neglecting  $\mathcal{O}(\lambda^4)$  terms may give wrong results. The question then arises how to find  $\mathcal{O}(\lambda^4)$  and higher order terms. The point is that since (2.29) is only an approximation the *exact* definition of the parameters in (2.30) is not unique by terms of the neglected order  $\mathcal{O}(\lambda^4)$ . This is the reason why in different papers in the literature different  $\mathcal{O}(\lambda^4)$  terms can be found. They simply correspond to different definitions of the parameters in (2.30). Obviously the physics does not depend on this choice. Here we will follow a definition which allows for simple relations between the parameters (2.28) and (2.30). This will also restore the unitarity of the CKM matrix which in the Wolfenstein parametrization as given in (2.29) is not satisfied exactly.

To this end we go back to (2.27) and we impose the relations

$$s_{12} = \lambda$$

,  $s_{23} = \Lambda \lambda^2$ ,  $s_{13}e^{-i\delta} = A\lambda^3(\varrho - i\eta)$  (2.31)

to all orders in  $\lambda$ . It follows then that

$$\varrho = \frac{s_{13}}{s_{12}s_{23}}\cos\delta, \qquad \eta = \frac{s_{13}}{s_{12}s_{23}}\sin\delta.$$

(2.32)

We observe that (2.31) and (2.32) represent simply the change of variables from (2.28) to (2.30). Making this change of variables in the standard parametrization (2.27) we find the CKM matrix as a function of  $(\lambda, A, \varrho, \eta)$  which satisfies unitarity exactly! We also note that in view of  $c_{13} = 1 - \mathcal{O}(\lambda^6)$  the relations between  $s_{ij}$  and  $|V_{ij}|$  in (2.28) are satisfied to high accuracy.

In order to improve the accuracy of the unitarity triangle discussed below one includes also the  $\mathcal{O}(\lambda^5)$  correction to  $V_{td}$ . In summary then  $V_{us}$ ,  $V_{cb}$ ,  $V_{ub}$ ,  $V_{td}$  and  $V_{ts}$  are given to an excellent approximation as follows:

$$V_{us} = \lambda, \qquad V_{cb} = A\lambda^2 \tag{2.33}$$

$$V_{ub} = A\lambda^3(\varrho - i\eta), \qquad V_{td} = A\lambda^3(1 - \bar{\varrho} - i\bar{\eta})$$

(2.34)

$$V_{ts} = -A\lambda^2 + \frac{1}{2}A(1 - 2\varrho)\lambda^4 - i\eta A\lambda^4$$

(2.35)

with

$$\bar{\varrho} = \varrho(1 - \frac{\lambda^2}{2}), \qquad \bar{\eta} = \eta(1 - \frac{\lambda^2}{2}).$$

(2.36)

The advantage of this generalization of the Wolfenstein parametrization over other generalizations found in the literature is the absence of relevant corrections to  $V_{us}$ ,  $V_{cb}$  and  $V_{ub}$  and an elegant change in  $V_{td}$  which allows a simple generalization of the unitarity triangle.

#### 2.2.5 The unitarity triangle

The unitarity of the CKM-matrix leads to the following set of equations:

$$|V_{ud}|^2 + |V_{cd}|^2 + |V_{td}|^2 = 1 (2.37)$$

$$|V_{us}|^2 + |V_{cs}|^2 + |V_{ts}|^2 = 1 (2.38)$$

$$|V_{ub}|^2 + |V_{cb}|^2 + |V_{tb}|^2 = 1 (2.39)$$

$$|V_{ud}|^2 + |V_{us}|^2 + |V_{ub}|^2 = 1 (2.40)$$

$$|V_{cd}|^2 + |V_{cs}|^2 + |V_{cb}|^2 = 1 (2.41)$$

$$|V_{td}|^2 + |V_{ts}|^2 + |V_{tb}|^2 = 1 (2.42)$$

$$V_{ud}V_{us}^* + V_{cd}V_{cs}^* + V_{td}V_{ts}^* = 0 (2.43)$$

$$V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0 (2.44)$$

$$V_{us}V_{ub}^* + V_{cs}V_{cb}^* + V_{ts}V_{tb}^* = 0 (2.45)$$

$$V_{ud}V_{cd}^* + V_{us}V_{cs}^* + V_{ub}V_{cb}^* = 0 (2.46)$$

$$V_{ud}V_{td}^* + V_{us}V_{ts}^* + V_{ub}V_{tb}^* = 0 (2.47)$$

$$V_{cd}V_{td}^* + V_{cs}V_{ts}^* + V_{cb}V_{tb}^* = 0. (2.48)$$

Whereas (2.37)-(2.39) and (2.40)-(2.42) describe the normalization of the columns and rows of the CKM-matrix, respectively, (2.43)-(2.45) and (2.46)-(2.48) originate from the orthogonality of different columns and rows, respectively. The orthogonality relations (2.43)-(2.48) are of particular interest since they can be represented as six "unitarity" triangles in the complex plane. Note that the set of equations (2.37)-(2.48) is invariant under the CKM phase-transformations specified in (ref?? maybe explain it??). If one performs such transformations, the triangles corresponding to (2.43)-(2.48) are rotated in the complex plane. Since the angles and the sides (given by the moduli of the elements of the mixing matrix) in these triangles remain unchanged and do therefore not depend on the CKM-phase convention, these quantities are physical observables.

It can be shown that all six triangles have the same area which is related to the measure of CP violation  $J_{\text{CP}}$ :

$$|J_{\rm CP}| = 2 \cdot A_{\Delta}, \tag{2.49}$$

where  $A_{\Delta}$  denotes the area of the unitarity triangles.

Let us briefly analyze the shape of the six unitarity triangles by using the original Wolfenstein parametrization. Then we find that most of these triangles are very squashed ones, since the Wolfenstein-structure both of eqs. (2.43)-(2.45) and (2.46)-(2.48), respectively, is given as follows:

$$\mathcal{O}(\lambda) + \mathcal{O}(\lambda) + \mathcal{O}(\lambda^5) = 0 \tag{2.50}$$

$$\mathcal{O}(\lambda^3) + \mathcal{O}(\lambda^3) + \mathcal{O}(\lambda^3) = 0 \tag{2.51}$$

$$\mathcal{O}(\lambda^4) + \mathcal{O}(\lambda^2) + \mathcal{O}(\lambda^2) = 0. \tag{2.52}$$

Consequently, only in the unitarity triangles corresponding to (2.44) and (2.47), all three sides are of comparable magnitude  $(\mathcal{O}(\lambda^3))$ , while in those described by (2.43), (2.46) and (2.45), (2.48) one side is suppressed relative to the remaining ones by  $\mathcal{O}(\lambda^4)$  and  $\mathcal{O}(\lambda^2)$ , respectively. The triangles related to (2.44) and (2.47) agree at the  $\mathcal{O}(\lambda^3)$  level and differ only through  $\mathcal{O}(\lambda^5)$  corrections. Neglecting the latter subleading contributions they describe the unitarity triangle that appears usually in the literature.

Let us next concentrate on the most interesting unitarity triangle described by

$$V_{ud}V_{ub}^* + V_{cd}V_{cb}^* + V_{td}V_{tb}^* = 0. (2.53)$$

Phenomenologically this triangle is very interesting as it involves simultaneously the elements  $V_{ub}$ ,  $V_{cb}$  and  $V_{td}$ .

In most analyses of the unitarity triangle present in the literature only terms  $\mathcal{O}(\lambda^3)$  are kept in (2.53). It is, however, straightforward to include the next-to-leading  $\mathcal{O}(\lambda^5)$  terms. We note first that

$$V_{cd}V_{cb}^* = -A\lambda^3 + \mathcal{O}(\lambda^7). \tag{2.54}$$

Thus to an excellent accuracy  $V_{cd}V_{cb}^*$  is real with  $|V_{cd}V_{cb}^*|-A\lambda^3$ . Keeping  $\mathcal{O}(\lambda^5)$  corrections and rescaling all terms in (2.53) by  $A\lambda^3$  we find

$$\frac{1}{A\lambda^3}V_{ud}V_{ub}^* = \bar{\varrho} + i\bar{\eta}, \qquad \qquad \frac{1}{A\lambda^3}V_{td}V_{tb}^* = 1 - (\bar{\varrho} + i\bar{\eta}) \qquad (2.55)$$

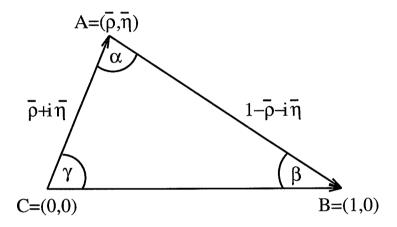

with  $\bar{\varrho}$  and  $\bar{\eta}$  defined in (2.36). Thus we can represent (2.53) as the unitarity triangle in the complex  $(\bar{\varrho},\bar{\eta})$  plane. This is shown in fig. 2.7. The length of the side CB which lies on the real axis equals unity when eq. (2.53) is rescaled by  $V_{cd}V_{cb}^*$ . We observe that beyond the leading order in  $\lambda$  the point A does not correspond to  $(\varrho,\eta)$  but to  $(\bar{\varrho},\bar{\eta})$ . Clearly within 3% accuracy  $\bar{\varrho}=\varrho$  and  $\bar{\eta}=\eta$ . Yet in the distant future the accuracy of experimental results and theoretical calculations may improve considerably so that the more accurate formulation will be appropriate.

Figure 2.7: Unitarity Triangle.

For numerical calculations the following procedure for the construction of the unitarity triangle should be recommended:

- Use the standard parametrization in phenomenological applications to find  $s_{12},\,s_{13},\,s_{23}$  and  $\delta.$

- Translate to the set  $(\lambda, A, \varrho, \eta)$  using (2.31) and (2.32).

- Calculate  $\bar{\varrho}$  and  $\bar{\eta}$  using (2.36).

Using simple trigonometry one can express  $\sin(2\phi_i)$ ,  $\phi_i = \alpha, \beta, \gamma$ , in terms of  $(\bar{\rho}, \bar{\eta})$  as follows:

$$\sin(2\alpha) = \frac{2\bar{\eta}(\bar{\eta}^2 + \bar{\varrho}^2 - \bar{\varrho})}{(\bar{\varrho}^2 + \bar{\eta}^2)((1 - \bar{\varrho})^2 + \bar{\eta}^2)}$$

(2.56)

$$\sin(2\beta) = \frac{2\bar{\eta}(1-\bar{\varrho})}{(1-\bar{\varrho})^2 + \bar{\eta}^2} \tag{2.57}$$

$$\sin(2\gamma) = \frac{2\bar{\varrho}\bar{\eta}}{\bar{\varrho}^2 + \bar{\eta}^2} = \frac{2\varrho\eta}{\varrho^2 + \eta^2}.$$

(2.58)

The lengths CA and BA in the rescaled triangle of fig. 12 to be denoted by  $R_b$  and  $R_t$ , respectively, are given by

$$R_b \equiv \frac{|V_{ud}V_{ub}^*|}{|V_{cd}V_{cb}^*|} = \sqrt{\bar{\varrho}^2 + \bar{\eta}^2} = (1 - \frac{\lambda^2}{2}) \frac{1}{\lambda} \left| \frac{V_{ub}}{V_{cb}} \right|$$

(2.59)

$$R_t \equiv \frac{|V_{td}V_{tb}^*|}{|V_{cd}V_{cb}^*|} = \sqrt{(1-\bar{\varrho})^2 + \bar{\eta}^2} = \frac{1}{\lambda} \left| \frac{V_{td}}{V_{cb}} \right|. \tag{2.60}$$

The expressions for  $R_b$  and  $R_t$  given here in terms of  $(\bar{\varrho}, \bar{\eta})$  are excellent approximations. Clearly  $R_b$  and  $R_t$  can also be determined by measuring two of the angles  $\phi_i$ :

$$R_b = \frac{\sin(\beta)}{\sin(\alpha)} = \frac{\sin(\alpha + \gamma)}{\sin(\alpha)} = \frac{\sin(\beta)}{\sin(\gamma + \beta)}$$

(2.61)

$$R_t = \frac{\sin(\gamma)}{\sin(\alpha)} = \frac{\sin(\alpha + \beta)}{\sin(\alpha)} = \frac{\sin(\gamma)}{\sin(\gamma + \beta)}.$$

(2.62)

The angles  $\beta$  and  $\gamma$  of the unitarity triangle are related directly to the complex phases of the CKM-elements  $V_{td}$  and  $V_{ub}$ , respectively, through

$$V_{td} = |V_{td}|e^{-i\beta}, \quad V_{u\bar{b}} = |V_{ub}|e^{-i\gamma}.$$

(2.63)

The angle  $\alpha$  can be obtained through the relation

$$\alpha + \beta + \gamma = 180^{\circ} \tag{2.64}$$

expressing the unitarity of the CKM-matrix.

The triangle depicted in fig. 12 together with  $|V_{us}|$  and  $|V_{cb}|$  gives a full description of the CKM matrix. Looking at the expressions for  $R_b$  and  $R_t$ , we observe that within the Standard Model the measurements of four CP conserving decays sensitive to  $|V_{us}|$ ,  $|V_{ub}|$ ,  $|V_{cb}|$  and  $|V_{td}|$  can tell us whether CP violation ( $\eta \neq 0$ ) is predicted in the Standard Model. This is a very remarkable property of the Kobayashi-Maskawa picture of CP violation: quark mixing and CP violation are closely related to each other.

There is of course the very important question whether the KM picture of CP violation is correct and more generally whether the Standard Model offers a correct description of weak decays of hadrons. In order to answer these important questions it is essential to calculate as many branching ratios as possible, measure them experimentally and check whether they all can be described by the same set of the parameters  $(\lambda, A, \varrho, \eta)$ . In the language of the unitarity triangle this means that the various curves in the  $(\bar{\varrho}, \bar{\eta})$  plane extracted from different decays should cross each other at a single point. Moreover the angles  $(\alpha, \beta, \gamma)$  in the resulting triangle should agree with those extracted one day from CP-asymmetries in B-decays.

#### 2.3 B physics in ATLAS

An important chapter of LHC physics will be the study of heavy-quark systems. In fact, already at initial lower luminosities the LHC will be a high-rate beauty- and top-quark factory. A particularly rich field will be available in B-physics, the main emphasis being on the precise measurement of CP-violation in the  $B_d^0$  system and the determination of the angles in the Cabibbo-Kobayashi-Maskawa unitarity triangle. In addition, investigations of  $B\overline{B}$  mixing in the  $B_s^0$  system, rare B decays, and general spectroscopy of states with b-quarks will be of great interest. The goal of the ATLAS Collaboration to address also these physics topics has had an important impact on the detector design. Precise secondary vertex determination, full reconstruction of final states with relatively low- $p_T$  particles, an example being  $B_d^0 \to J/\psi K_S^0$  followed by  $J/\psi \to \ell^+\ell^-$  and  $K_S^0 \to \pi^+\pi^-$ , and low- $p_T$  lepton first-level trigger thresholds as well as second-level track triggering capability are all necessary requirements for the experiment.

#### 2.3.1 *CP*-violation in ATLAS

The neutral kaon system discussed in section??? is the only evidence of the CP-violation that was measured up till now, so scientists were looking for another ecxperiment that would confirm it. They were seeking also for a bigger effect than that of  $2.3 \times 10^{-3}$  of the neutral kaon system. In fact, the Standard Model predicts a much bigger effect in the case of B-mesons. Of course, to produce B-mesons one has to have a much bigger energy, because of the large mass of the b-quark, and that's where the Large Hadron Collider comes into the picture. With the LHC it will be possible to reach energies, that have never been reached before resulting in a very high number of b-quarks. The ATLAS Collaboration aims to perform a wide programme of B-physics studies. These include the search for and measurement of CP-violation through the decays  $B_d^0 \to J/\psi K_S^0$ ,  $B_d^0 \to \pi^+\pi^-$ , and  $B_s^0 \to J/\psi\phi$ . Other topics are the measurement of  $B_s^0$  mixing, searches for rare decays such as  $B_d^0 \to \mu^+\mu^-$ ,  $B_s^0 \to \mu^+\mu^-$ , the study of B-baryon decay dynamics, and spectroscopy of rare B hadrons.

B-physics studies will be experimentally easiest at the initial luminosity  $\mathcal{L} \approx 10^{33} \ \mathrm{cm^{-2} \, s^{-1}}$ , where pile-up effects are small and vertex detectors very close to the beam pipe are expected to survive for several years. Much of the B physics will thus be performed during the first few years of LHC operation. It is assumed in the ATLAS Technical Proposal that the total  $b\bar{b}$  production cross-section is  $\sim 500 \ \mu b$ .

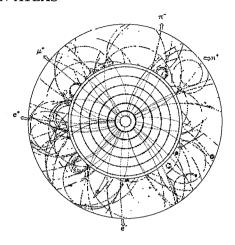

Strong features of the ATLAS detector for the B-physics programme are a powerful and flexible trigger system, high-resolution secondary-vertex measurement, and efficient track reconstruction and electron identification down to low  $p_{\rm T}$ . These have been studied in detail using full simulation of the inner detector and applying global pattern-recognition, bremsstrahlung-recovery and vertex-fitting algorithms (see for example a  ${\rm B_d^0} \to {\rm J/\psi K_S^0}$  simulation on figure 2.8).

Figure 2.8:  $B_d^0 \to J/\psi K_S^0$  event display at the inner detector

Figure 2.9:

$$B_d^0 \to J/\psi K_S^0$$

decay (tagging...)

#### $B_d^0 \to J/\psi K_S^0$ decays

The decay mode  $B_d^0 \to J/\psi K_S^0$  is a clean channel for measuring  $\sin 2\beta$ , where  $\beta$  is one of the angles in the unitarity triangle. The reconstructed B meson is tagged as having been produced as a  $B_d^0$  or a  $\bar{B}_d^0$  using the charge of the accompanying 'tag' muon (see fig. 2.9), which is assumed to come from the semileptonic decay of the other b-quark in the event.

In the decay mode  $B^0_d \to J/\psi K^0_S$ , the quark subprocess is dominated by the single tree-level transition  $b \to c\bar c s$ . The time-dependent decay rates of  $B^0_d$ ,  $\bar B^0_d \to J/\psi K^0_S$  are [3]

$$N(\mathrm{B_d^0}(t) \to \mathrm{J}/\psi \mathrm{K_S^0}) \propto \exp^{-\Gamma t} (1 - \sin 2\beta \sin \Delta m t)$$

$N(\bar{\mathrm{B}_d^0}(t) \to \mathrm{J}/\psi \mathrm{K_S^0}) \propto \exp^{-\Gamma t} (1 + \sin 2\beta \sin \Delta m t)$  (2.65)

where  $\Gamma=1/\tau$  is the average of the widths  $\Gamma_1$  and  $\Gamma_2$  of the B-meson mass eigenstates,  $\Delta m$  is the mass difference between the eigenstates, and  $\beta$  is one of the angles of the unitarity triangle. The asymmetry in the decay  $B_d^0 \to J/\psi K_S^0$ , when integrating starting from time  $t_0$ , is:

$$A = \frac{N(\mathbf{B}_{d}^{0} \to \mathbf{J}/\psi \mathbf{K}_{S}^{0}) - N(\bar{\mathbf{B}}_{d}^{0} \to \mathbf{J}\psi/\mathbf{K}_{S}^{0})}{N(\mathbf{B}_{d}^{0} \to \mathbf{J}/\psi \mathbf{K}_{S}^{0}) + N(\bar{\mathbf{B}}_{d}^{0} \to \mathbf{J}\psi/\mathbf{K}_{S}^{0})}$$

$$= 1/(1 + x_{d}^{2}) \sin 2\beta (\sin \Delta m t_{0} + x_{d} \cos \Delta m t_{0})$$

$$= D_{int} \sin 2\beta$$

(2.66)

The factor multiplying  $\sin 2\beta$  comes from the time-integration. For  $t_0=0$ ,  $D_{int}=x_d/(1+x_d)=0.47$ , with  $x_d=\Delta m/\Gamma\approx 0.69\pm 0.07$  [6]. The observed asymmetry is

$$A^{obs} = \frac{N_{total}(J/\psi K_S^0 l^+) - N_{total}(J/\psi K_S^0 l^-)}{N_{total}(J/\psi K_S^0 l^+) + N_{total}(J/\psi K_S^0 l^-)}$$

$$\simeq D_{taa} D_{back}(D_{int} \sin 2\beta + A^p)$$

(2.67)

where  $A^p$  is the production asymmetry of  $B_d^0$  and  $\overline{B}_d^0$ , estimated to be at the percent level [4]. The statistical significance of the signal is reduced by wrong-sign tags ( $D_{tag} = 1 - 2W$ , where W is the fraction of wrong-sign tags over the total number of tags). Wrong assignments of the tag-lepton are caused by

- 1. cascade decays of the b

- 2.  $B^0 \overline{B}^0$  mixing

- 3. additional c- and b-quarks created in the parton shower

- 4. hadron background

- 5. top decays

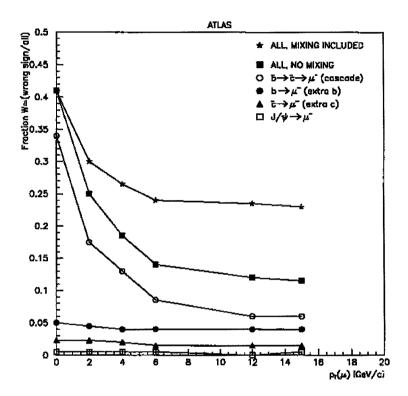

They are dominated by cascade decays and mixing. Fig. 2.10 illustrates the wrong-tag fraction as a function of the transverse-momentum threshold of the trigger muon. With the  $p_T > 6~GeV$  used at ATLAS  $D_{tag} = 0.52$ .  $D_{\rm back} = N_{\rm S}/N_{\rm total}$  is the dilution factor from background, where  $N_{\rm S}$  and  $N_{\rm total}$  are the number of signal events and the total number of events respectively; the background is assumed to be asymmetry-free.

Reconstruction of  $K_S^0 \to \pi^+\pi^-$  decays has been studied using a full detector simulation [2]. The  $K_S^0$  mass resolution was in the range 3–8 MeV for transverse decay lengths of 1–50 cm, depending on the  $K_S^0$  decay position. The average efficiency was 91% and the background under the  $K_S^0$  peak was 6% at  $\mathcal{L} = \infty \cdot 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup>. At  $\mathcal{L} = \nabla \cdot 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup>, the efficiency was 88% while the background rose to 11%.

The signal and background analyses were performed using a particle-level simulation [5]. The signal search started from the J/ $\psi$  reconstruction. For  $\mu$ -tagged J/ $\psi$   $\rightarrow$  e<sup>+</sup>e<sup>-</sup> decays, a tag muon with  $p_{\rm T} > 6$  GeV and  $|\eta| < 2.2$ , and two electrons with  $p_{\rm T} > 1$  GeV were required. For  $\mu$ -tagged J/ $\psi$   $\rightarrow$   $\mu$ <sup>+</sup> $\mu$ <sup>-</sup> decays, a tag muon with  $p_{\rm T} > 5$  GeV, and two other muons with  $p_{\rm T}(\mu^1) > 5$  GeV,  $p_{\rm T}(\mu^2) > 3$  GeV were required; in addition, one of the three muons was required to satisfy the trigger, having  $p_{\rm T} > 6$  GeV,  $|\eta| < 2.2$ . For electron-tagged J/ $\psi$   $\rightarrow$   $\mu$ <sup>+</sup> $\mu$ <sup>-</sup> events, a tag electron with  $p_{\rm T} > 5$  GeV, and two muons with  $p_{\rm T}(\mu^1) > 6$  GeV,  $|\eta(\mu^1)| < 2.2$ , and  $p_{\rm T}(\mu^2) > 3$  GeV were required.

The distance of closest approach between the two lepton candidates forming the  $J/\psi$  was required to be < 100  $\mu$ m. The distance of the  $J/\psi$  decay vertex from the primary vertex in the transverse plane was required to be > 250  $\mu$ m.

. 35.0

Figure 2.10: The sources of wrong-sign trigger muons and their fractions, as a function of the trigger threshold

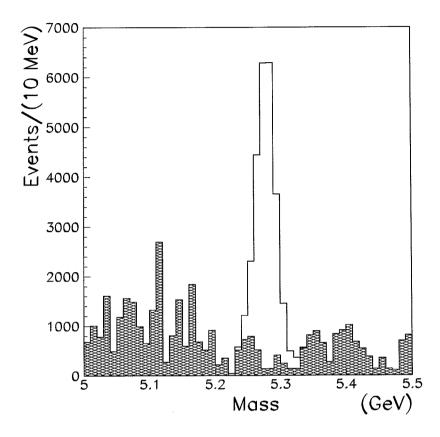

Figure 2.11: Reconstructed  $(J/\psi K_S^0)$  mass. The white histogram shows the signal and the hatched histogram shows the background.

In the  $\mu^+\mu^-$  channel, the reconstructed J/ $\psi$  mass was required to be within two standard deviations of the nominal one. In the e<sup>+</sup>e<sup>-</sup> channel, the mass window was [-400,+200] MeV around the J/ $\psi$  mass. After the above cuts, the fake-J/ $\psi$  fraction was  $\sim$  45% in the  $\mu$ -tagged  $\mu^+\mu^-$  channel, 95% in the  $\mu$ -tagged e<sup>+</sup>e<sup>-</sup> channel, and 24% in the electron-tagged  $\mu^+\mu^-$  channel.

Finally, the  $J/\psi$  and the  $K_S^0$  candidates were used to search for the  $B_d^0$ . The proper time of the B decay, measured from the distance of the  $J/\psi$  decay vertex from the primary vertex in the transverse plane, and from the reconstructed  $p_T$  of the B, was required to be > 0.5 ps. Such a cut on the proper time corresponds to  $D_{\rm int}=0.63$ . Constraining the  $K_S^0$  and the  $J/\psi$  masses to their nominal values, a  $B_d^0$  mass resolution of 16 MeV was obtained. The reconstructed  $J/\psi K_S^0$  mass distributions for the signal and background are shown in Fig. 2.11 after all the cuts except for the final two-standard-deviation cut on

the reconstructed  $B_d^0$  mass. The dominant background comes from a real  $J/\psi$  from a B decay combined with a  $K_S^0$  from the fragmentation. Fake  $J/\psi$ 's and  $K_S^0$ 's were also included in the background estimate. Cuts on the decay length of the  $J/\psi$  candidate suppress background from real  $J/\psi$  coming directly from hadronization.

The value of  $\sin 2\beta$  was obtained from a fit to the proper time distributions for the positive and negative tags. The statistical precision for  $\sin 2\beta$ , including the effect of the secondary-vertex resolution, was  $\delta(\sin 2\beta) = 0.018$ .

Theoretical uncertainties in the measurement of  $\sin 2\beta$  via the decay channel  $J/\psi K_S^0$  are expected to be less than 1%. The experimental sources of systematic error can be controlled with comparable accuracy. The background is relatively small and dominated by accidental background with a rather flat mass distribution.

$$B_d^0 \to \pi^+\pi^-$$

decays

The CP-asymmetry in the decay mode  $B_d^0 \to \pi^+\pi^-$  is sensitive to the angle  $\alpha$  in the unitarity triangle. The branching fraction of this decay has not yet been measured, and was assumed to be  $2\cdot 10^{-5}$ .

The largest experimental uncertainties in this decay mode are due to the background. Systematic errors may arise from uncertainties in the branching fractions and shapes of mass distributions of the B decays which constitute the background, since it is possible that not all these decays will have been studied before the LHC becomes operational.

In spite of the large systematic uncertainties associated with the measurement of  $\sin 2\alpha$ , it will be interesting to establish CP-violation in the  $B_d^0 \to \pi^+\pi^-$  channel, and a measurement of the asymmetry will constrain the CP-violation parameters.

#### $B_s^0 \to J/\psi \phi$ decays

The decay  $B_s^0 \to J/\psi \phi$  is related to the third angle  $\gamma$  of the unitarity triangle. The CP-asymmetry is, however, suppressed by a small factor  $D_{\rm CKM}$  and the maximum asymmetry is expected to be only  $\sim 3\%$  in the Standard Model. A large observed asymmetry would thus be an indication of new physics.

## Chapter 3

# The Semiconductor Tracker (SCT)

The SCT is a sub-detector of the ATLAS Inner Detector (ID). The SCT works with the other elements of the ID, the Transition Radiation Tracker (TRT) and the Pixel Tracker to provide the necessary tracking functions to meet the performance requirements discussed in the previous chapter. The SCT is based upon silicon microstrip detector technology, which has been used with success over the past 8 years in experiments at LEP and at the Fermilab Tevatron. Consequently there is substantial experience in the high energy physics community with the construction and operation of these devices.

The ATLAS SCT aims to operate reliably according to performance specifications over a 10-year period of high luminosity LHC operation. The design LHC luminosity aims for an average peak value of  $10^{34}\ cm^{-2}s^{-2}$  over  $10^7$  secs per year, giving an annual integrated luminosity of  $10^{41}\ cm^{-2}$ . Instantaneous rates may exceed this value. These luminosities are achieved using bunch-bunch crossings separated by 25 nsec (40 MHz) to result in a particle interaction rate  $10^9\ Hz$ .

The SCT radial envelope is defined internally by the tolerance of silicon sensors and their electronics to charged and neutral radiation, and externally by the TRT, to an active radius  $r < 52 \ cm$  in the barrel region and  $r < 56 \ cm$  for the forward silicon disks. Silicon has been chosen as the detector medium because of its fast signal speed, and excellent spatial segmentation.

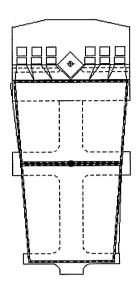

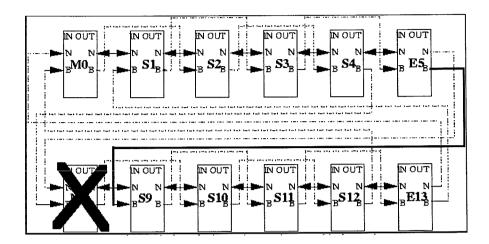

The layout consists of 4 'central' barrel layers in the radial range  $30 < R < 52 \ cm$ , and 9 disks in each of the forward and backward directions in the radial range  $26 < R < 56 \ cm$ .

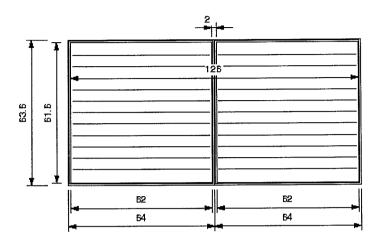

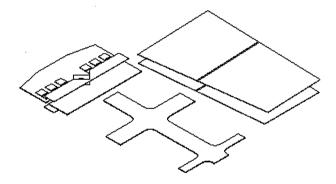

In the barrel region, each layer consists of silicon strip modules of 4 single-sided silicon detectors with active area 61.6 x 62.0  $mm^2$ , and geometric area 63.6 x 64.0  $mm^2$ . Within the module, two detectors are daisy-chained for each side of a module. On one side 768 strips of 80  $\mu m$  pitch and active length 123.2 mm are aligned precisely along the beam direction. The back-side detector pair

Figure 3.1:  $p^+n$  binary detectors, the effective bulk doping changes from n- to p type after irradiaion(strip width 22um, pitch80 um, tthickness 300 um)

is identical, but rotated by  $40\ mrad$ , to provide a z-measurement capability. The use of small-angle stereo rather than orthogonal strips is motivated by the need to reduce the number of ghost hits near a real track in high-multiplicity events. A second motivation is to retain an  $r-\phi$  measurement capability in the case of detector inefficiencies. In order to minimise the signal spread during operation in a 2 Tesla solenoidal field, the modules are mounted at an angle of  $10^o$  to the tangent. Modules are overlapped in a tile arrangement to minimise dead areas in the barrel region. The silicon detector signals will be read out by binary front-end electronics. Within the barrel region, all detectors have the same pitch, and all modules are identical.

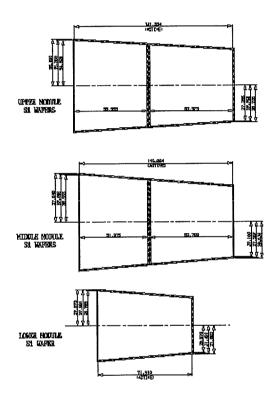

In the forward direction, the geometrical layout no longer allows the use of identical detector designs; nevertheless, the module construction is similar. Modules of daisy-chained singel-sided detector pairs with strip length  $\approx 12~cm$  and mean pitch  $\approx 80~\mu m$ , are arranged back-to-back with a 40 mrad stereo orientation.

The technical solutions for the SCT consist of a choice of silicon detector design and technology, a choice of front-end, readout, and monitoring electronics, a detector module design, a data transmission and cabling technology, a mounting scheme, and a cooling system.

#### 3.0.2 Detectors

The principal structure of the option chosen for ATLAS is shown on Figure 3.1

The effects of heavy particle irradiation on silicon detectors include an increase in leakage current, a change in effective doping  $^1$ , and a decrease in charge collection efficiency. The change in effective doping implies a change in the voltage necessary to deplete the detector and for detectors which are built on n-type bulk, the doping change will result in an effective type inversion. Projections for the SCT after 10 years of operation indicate depletion voltages of up to  $\approx 450~V$  and type inversion for all sensors. Significant uncertainties exist which may imply even higher voltages.

By constructing n-in-n detectors (n+ strips on an n-type substrate) it has been demonstrated that efficient partially depleted operation is possible after type inversion, with fast signal collection and limited charge diffusion. Because of the consequent safety margin, single-sided n-in-n sensors have been chosen. The detectors will be AC-coupled, and will be negativ-biaised from the backside to maintain only a small voltage across the capacitor oxide.

<sup>&</sup>lt;sup>1</sup>The radiation gives rise to the creation of deep level acceptor type defects.

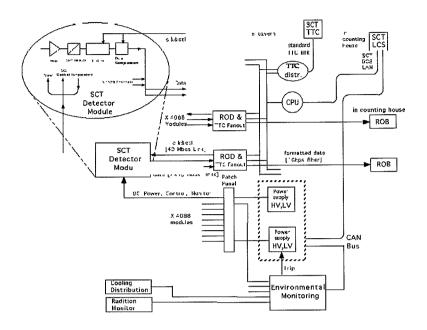

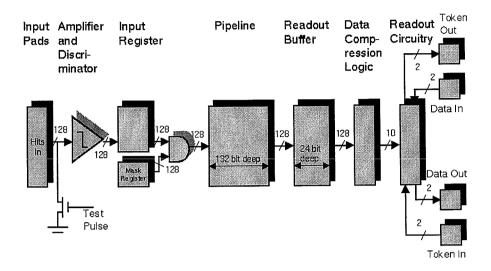

#### 3.0.3 Electronics

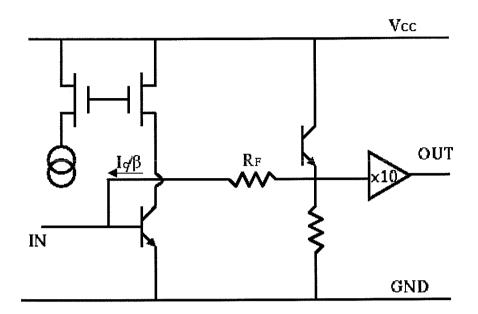

The front end electronics is based upon a one-bit digital (binary) readout architecture. This choice is supported by test-beam and bench prototype studies, and is the most cost-effective implementation meeting the performance requirements. Any strip that collects charge above an externally adjustable threshold fires a per strip discriminator. The binary output is stored in a pipeline until an ATLAS trigger initiates readout for the beam crossing. A consequence for this architecture is significant data reduction in the front end chips, meaning that the discriminator performance, thresholds, noise, and pickup must be well controlled.

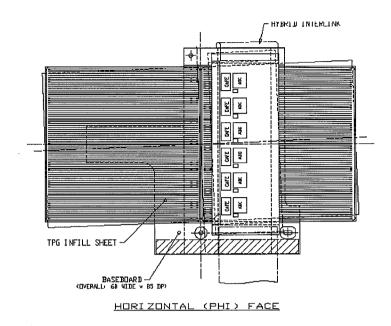

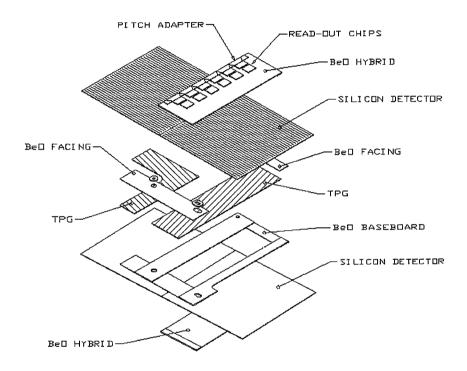

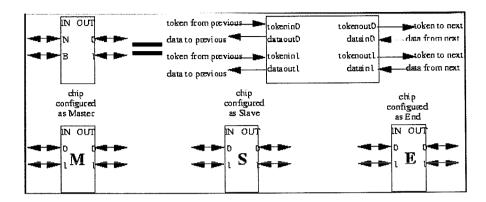

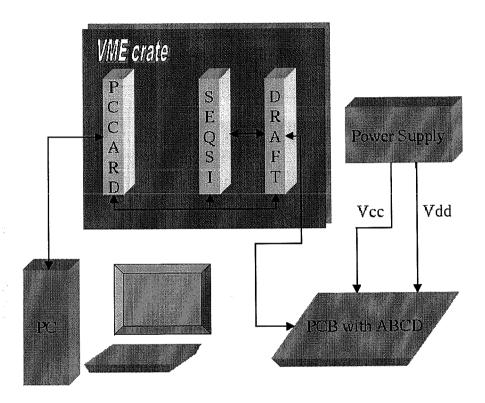

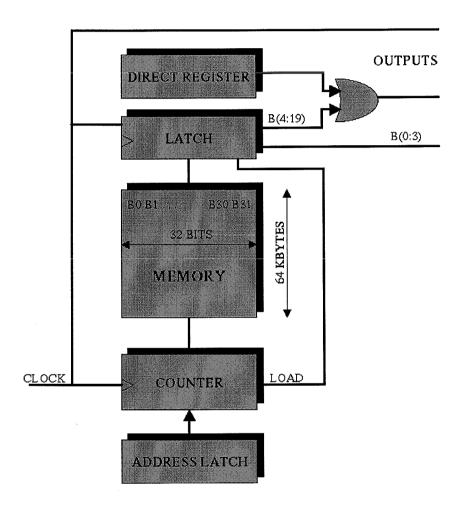

The hybrid design uses a thick film technology on a Berillium Oxide (BeO) substrate. The substrate choice is motivated by the high thermal conductivity and long radiation length of this material.