# Disclaimer

This note has not been internally reviewed by the DØ Collaboration. Results or plots contained in this note were only intended for internal documentation by the authors of the note and they are not approved as scientific results by either the authors or the DØ Collaboration. All approved scientific results of the DØ Collaboration have been published as internally reviewed Conference Notes or in peer reviewed journals.

# $\mathrm{D} \varnothing$ Silicon Tracker Technical Design Report

DØ Upgrade Collaboration

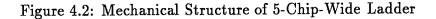

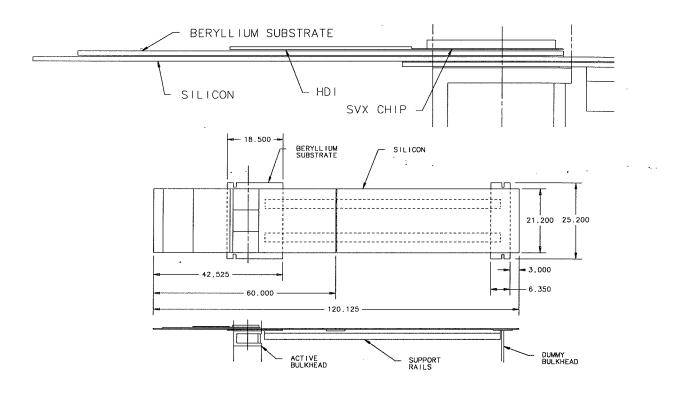

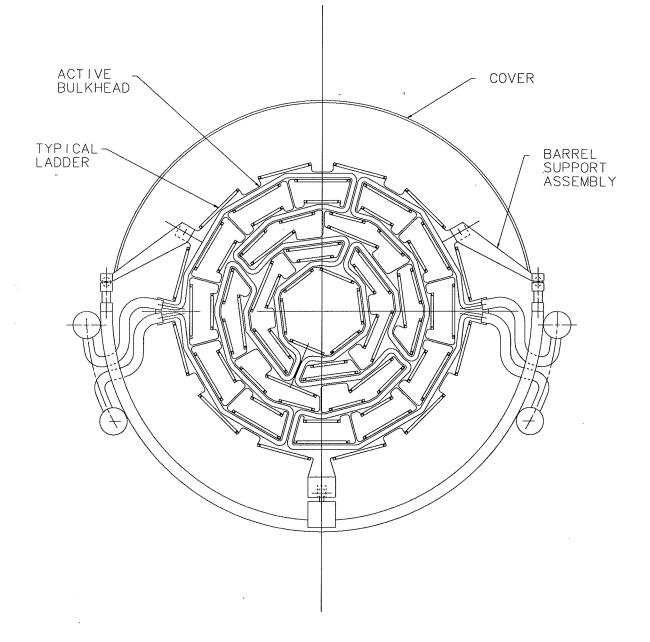

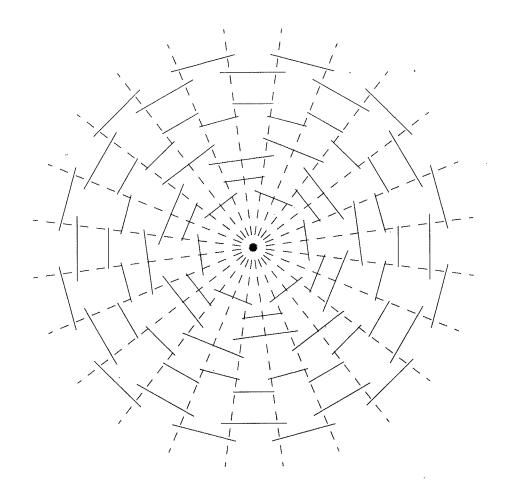

July 1, 1994

# Contents

|   |            | •                                                    |  |

|---|------------|------------------------------------------------------|--|

| 1 | Ove        | erview and Physics Motivation 4                      |  |

|   | 1.1        | Introduction                                         |  |

|   | 1.2        | Physics Goals                                        |  |

|   |            | 1.2.1 Top Physics                                    |  |

|   |            | 1.2.2 Beauty Physics                                 |  |

|   | 1.3        | Tevatron Parameters                                  |  |

|   | 1.4        | DØ Silicon Tracker Design                            |  |

|   |            | 1.4.1 Overall Design                                 |  |

|   |            | 1.4.2 Performance Considerations                     |  |

|   | 1.5        | Silicon Tracker Mass Issues                          |  |

|   | _          |                                                      |  |

| 2 |            | con Detectors 20                                     |  |

|   | 2.1        | Design and Specification of Silicon Detectors        |  |

|   |            | 2.1.1 Detector Specifications                        |  |

|   |            | 2.1.2 Wedge Detectors                                |  |

|   |            | 2.1.3 Barrel Detectors                               |  |

|   | 2.2        | Results from Wedge Detector Prototypes               |  |

|   |            | 2.2.1 Depletion Voltages                             |  |

|   |            | 2.2.2 Leakage Current and Breakdown Voltage          |  |

|   |            | 2.2.3 Coupling Capacitors 29                         |  |

|   |            | 2.2.4 Bias Resistors                                 |  |

|   |            | 2.2.5 n-side Interstrip Resistance                   |  |

|   |            | 2.2.6 Detector Strip Capacitance                     |  |

|   | 2.3        | Radiation Damage                                     |  |

|   |            | 2.3.1 Increase in Leakage Current                    |  |

|   |            | 2.3.2 Change of Full Depletion Voltage               |  |

|   | <b>2.4</b> | Plans for Production Electrical Testing              |  |

| • |            |                                                      |  |

| 3 |            | embly Alignment Constraints 42                       |  |

|   | 3.1        | Introduction                                         |  |

|   | 3.2        | Physics Constraints                                  |  |

|   | 3.3        | Tolerances Relating to the Trigger System 43         |  |

|   |            | 3.3.1 Tolerances Relating to Event Reconstruction 14 |  |

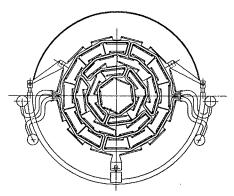

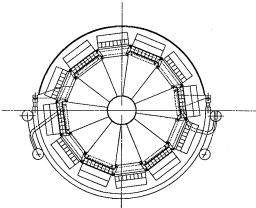

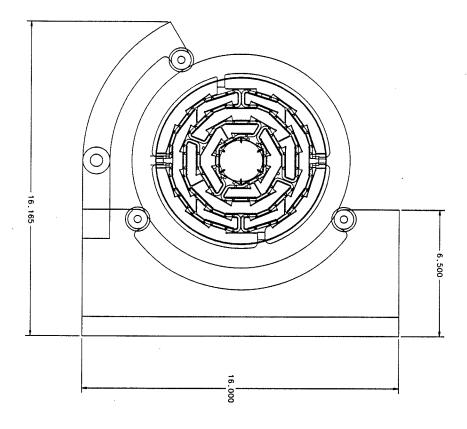

| 4 | Mee |                                                                                                              | 47  |

|---|-----|--------------------------------------------------------------------------------------------------------------|-----|

|   | 4.1 |                                                                                                              | 47  |

|   | 4.2 |                                                                                                              | 48  |

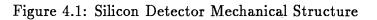

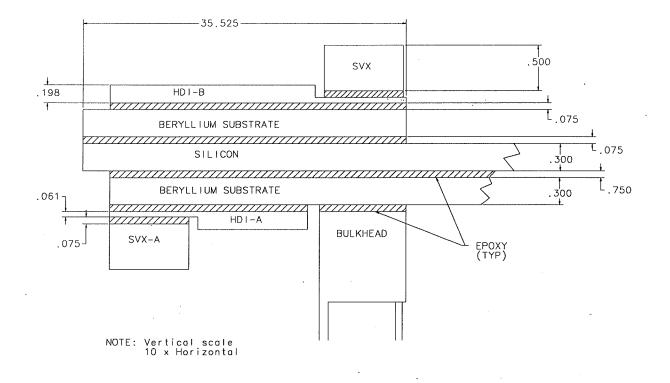

|   |     | 4.2.1 Ladders and Bulkheads                                                                                  | 48  |

|   |     | 4.2.2 Barrel Cabling                                                                                         | 58  |

|   | 4.3 |                                                                                                              | 60  |

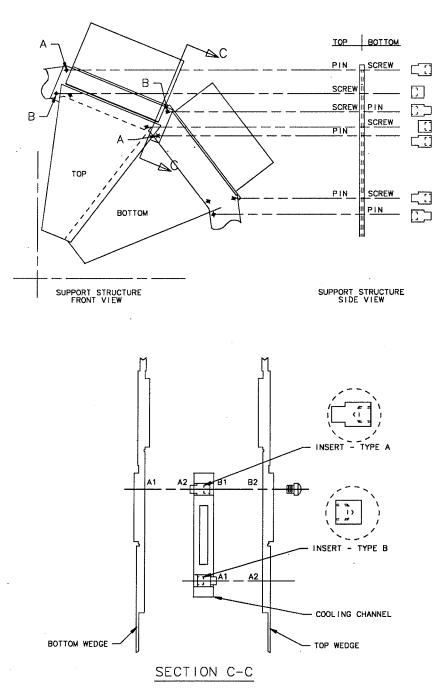

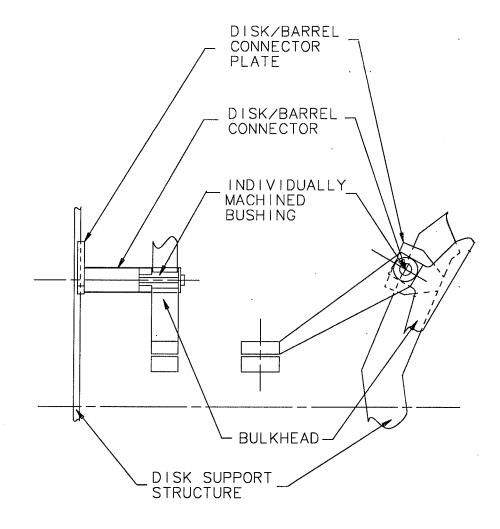

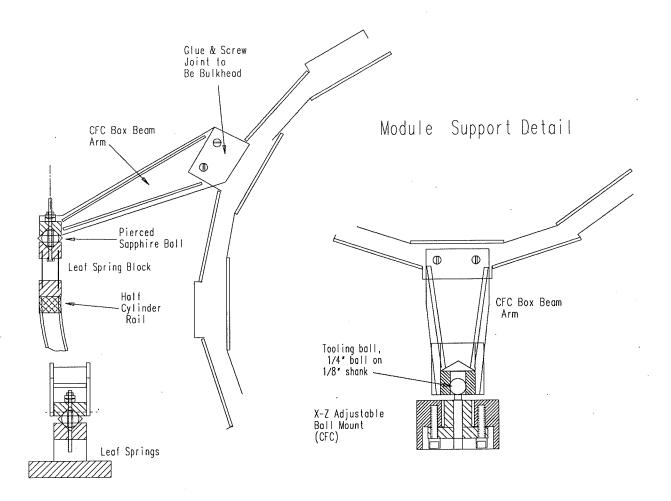

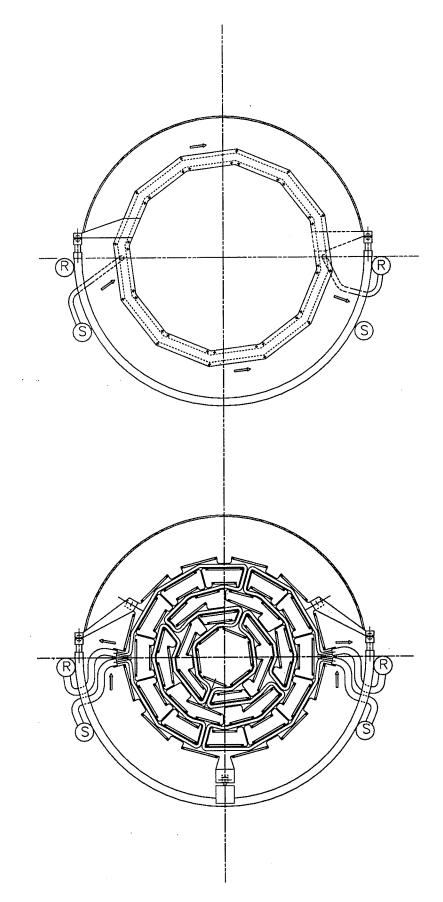

|   |     | 4.3.1 Disk and Wedge Structure                                                                               | 60  |

|   |     |                                                                                                              | 64  |

|   |     |                                                                                                              | 64  |

|   | 4.4 |                                                                                                              | 64  |

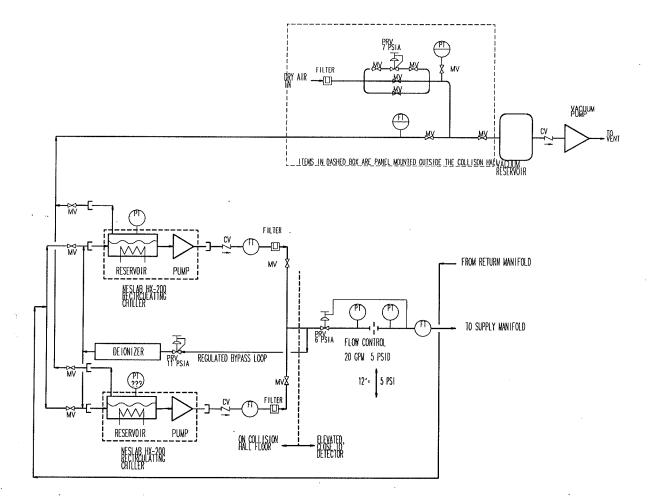

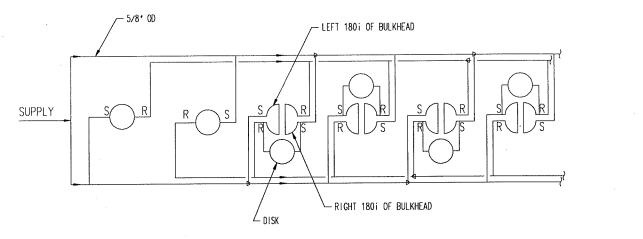

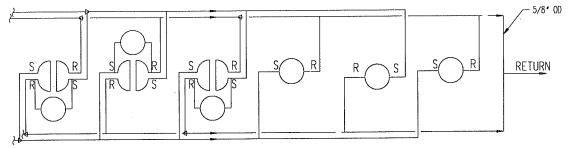

|   | 4.5 | Cooling                                                                                                      | 67  |

|   | 1.0 |                                                                                                              | 68  |

|   |     |                                                                                                              | 71  |

|   |     | 4.5.3 Wedge Temperatures                                                                                     | 71  |

|   |     | 4.5.4 Ambient Temperature Analysis                                                                           | 71  |

|   | 4.6 | Half-Cylinder                                                                                                | 74  |

|   | 4.0 |                                                                                                              | 77  |

|   | 4.7 | HOLI TOP COVER THE THE THE THE THE THE                                                                       | 77  |

|   | 4.8 | Beam Pipe                                                                                                    | 77  |

|   | 4.0 |                                                                                                              | ••• |

| 5 | Rea | adout Electronics and Trigger                                                                                | 79  |

|   | 5.1 | Readout Electronics                                                                                          | 79  |

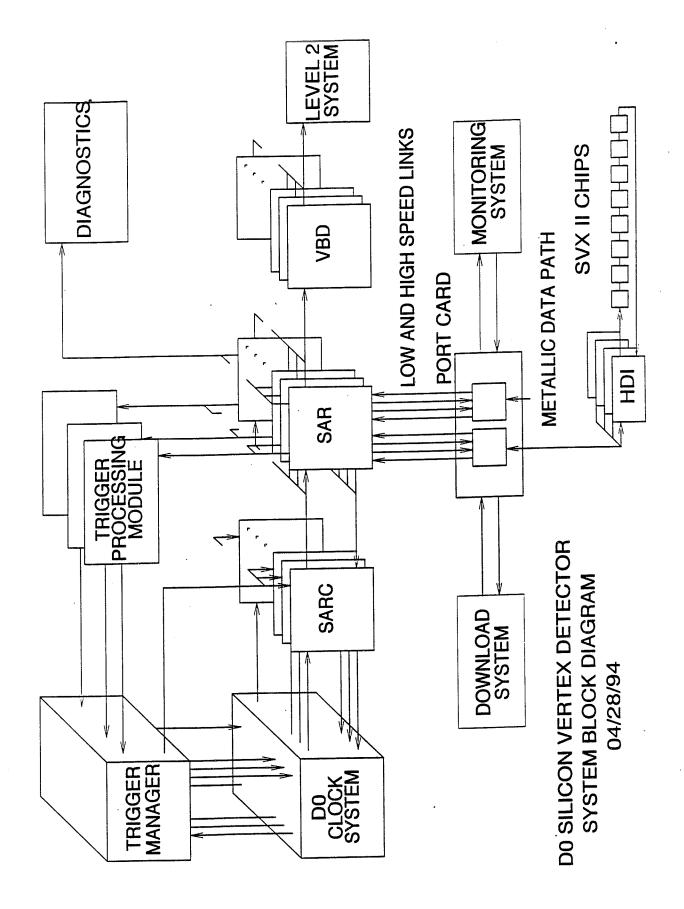

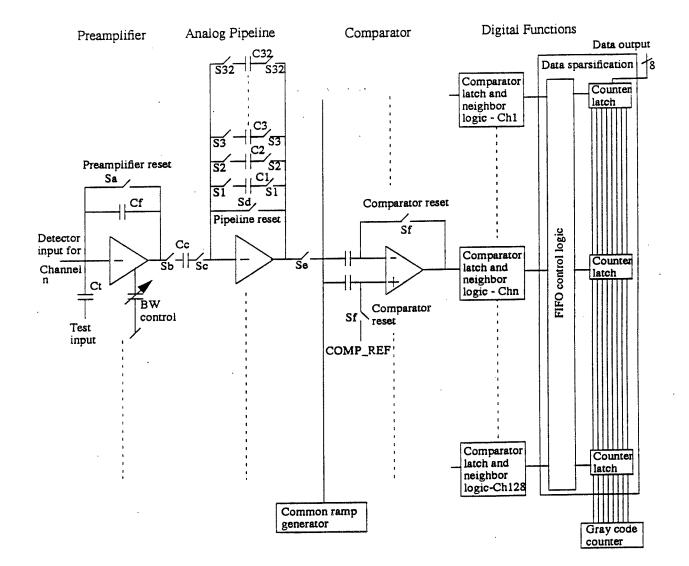

|   |     | 5.1.1 System Description                                                                                     | 79  |

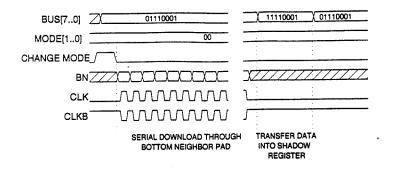

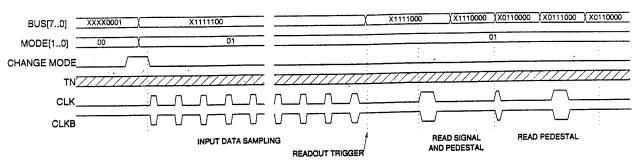

|   |     | 5.1.2 System Operation                                                                                       | 89  |

|   | 5.2 | DØ Tracking Triggers                                                                                         | 94  |

|   |     | 5.2.1 Scintillating Fiber Trigger                                                                            | 94  |

|   |     | 5.2.2 Output to Silicon Trigger                                                                              | 96  |

|   | 5.3 | The Level 1.5 Silicon Trigger                                                                                | 96  |

|   | 0.0 | 5.3.1 CDF Plans as Baseline                                                                                  | 96  |

|   |     | 5.3.2 DØ Impact Parameter Trigger                                                                            | 97  |

|   |     |                                                                                                              |     |

| 6 | Hig | in Density interconnect and castos                                                                           | .02 |

|   | 6.1 | mgn Density meerconneet and ran viv viv viv viv                                                              | 104 |

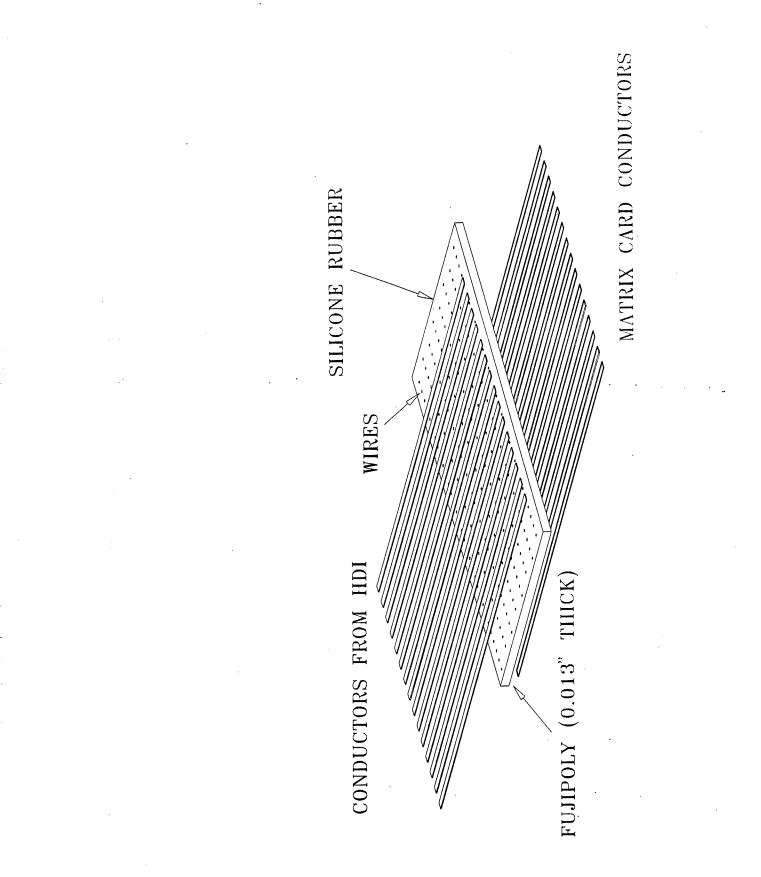

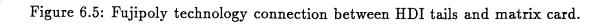

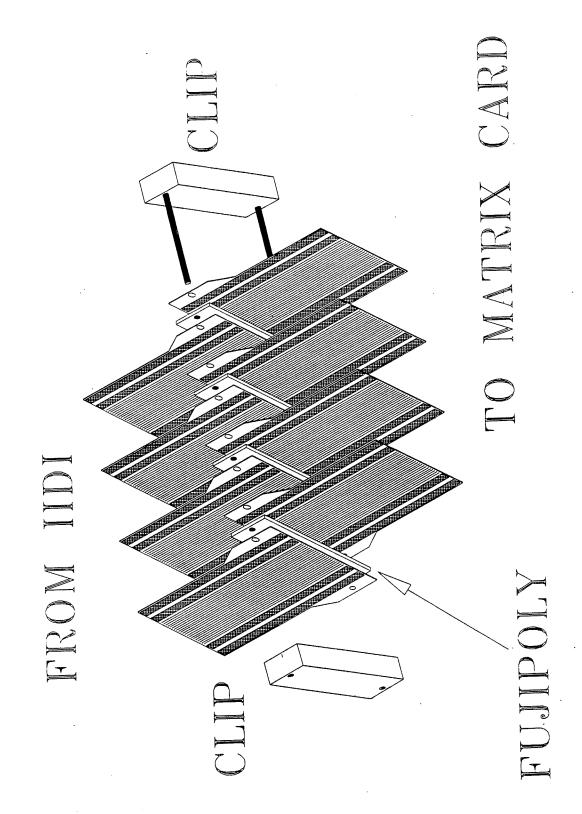

|   | 6.2 | Fujipoly Connection                                                                                          | 108 |

|   | 6.3 |                                                                                                              | 108 |

|   | 6.4 | Strip Cable                                                                                                  | 108 |

|   | 6.5 | Transition Card and Coax Cable                                                                               | 112 |

|   | 6.6 | System Mass                                                                                                  | 112 |

|   |     |                                                                                                              |     |

| 7 |     | chibiy, I foundation, and resonab                                                                            |     |

|   | 7.1 |                                                                                                              | 115 |

|   |     |                                                                                                              | 115 |

|   |     | 1.1.2 Abschibly and rebuild a contract of the test                                                           | 115 |

|   | 7.2 | Darrer Component i abrication i v v v v v v v v v v v v                                                      | 116 |

|   |     | 7.2.1 Construction $\ldots$ | 116 |

|    | 7.3<br>7.4<br>7.5<br>7.6<br>7.7 | 7.2.2 Testing117Barrel Module Fabrication118Disk Module Fabrication121Barrel Sub-Assembly Construction122End Disk Modules122Final Assembly and Installation123 |

|----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8  | Soft                            | tware 126                                                                                                                                                      |

|    | 8.1                             | Long Range Plans                                                                                                                                               |

|    |                                 | 8.1.1 Motivation                                                                                                                                               |

|    |                                 | 8.1.2 Proposal                                                                                                                                                 |

|    |                                 | 8.1.3 Functionality                                                                                                                                            |

|    |                                 | 8.1.4 Schedule                                                                                                                                                 |

|    | 8.2                             | Test Bench Plans                                                                                                                                               |

|    |                                 | 8.2.1 Motivation                                                                                                                                               |

|    |                                 | 8.2.2 Proposal                                                                                                                                                 |

|    |                                 | 8.2.3 Functionality                                                                                                                                            |

|    |                                 | 8.2.4 Schedule                                                                                                                                                 |

| 9  | Silic                           | con Tracker Beam Test Proposal 131                                                                                                                             |

| U  | 9.1                             | $\begin{array}{c} \text{Motivation} \\ \end{array}$                                                                                                            |

|    | 9.2                             | Proposed Measurements                                                                                                                                          |

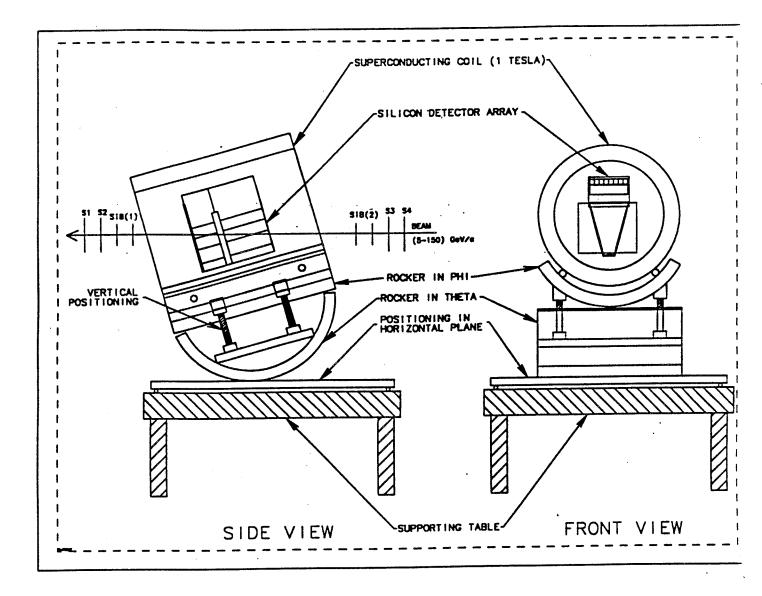

|    | 9.3                             | The Silicon Tracker Test-Beam Setup                                                                                                                            |

|    | 0.0                             | 9.3.1 Counter Arrangement                                                                                                                                      |

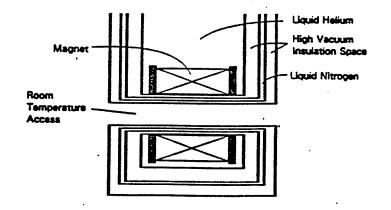

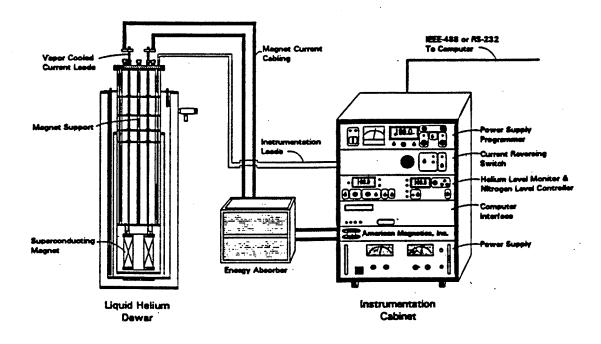

|    |                                 | 9.3.2 Magnet                                                                                                                                                   |

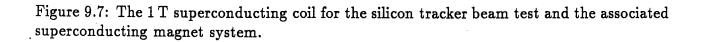

|    |                                 | 9.3.3 Readout Electronics                                                                                                                                      |

|    |                                 | 9.3.4 Controls                                                                                                                                                 |

|    | 9.4                             | Test-Beam Location and Schedule                                                                                                                                |

|    | 9.5                             | Preliminary Cost Estimate                                                                                                                                      |

|    |                                 | 9.5.1 Magnet                                                                                                                                                   |

|    |                                 | 9.5.2 Test-Beam Turn-Table                                                                                                                                     |

|    |                                 | 9.5.3 Total Cost                                                                                                                                               |

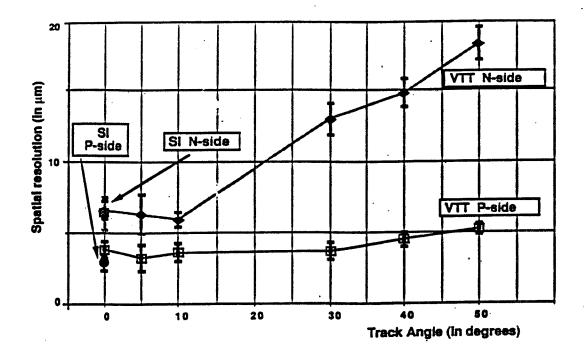

|    | App                             | endix 1: Test-Beams at Other Sites                                                                                                                             |

| 10 | <b>a</b> 1                      |                                                                                                                                                                |

| 10 |                                 | edule and Costs 145                                                                                                                                            |

|    | 10.1                            | Schedule                                                                                                                                                       |

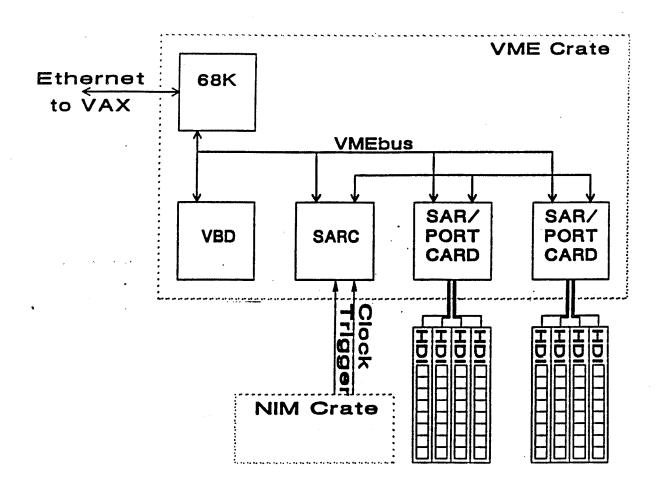

|    |                                 | 10.1.1 R&D Schedule                                                                                                                                            |

|    | 10.9                            | 10.1.2 Detector Production                                                                                                                                     |

|    | 10.2                            | Costs                                                                                                                                                          |

|    |                                 | 10.2.1         R&D Costs         150           10.2.2         Production Costs         150                                                                     |

|    |                                 | 10.2.2 Production Costs                                                                                                                                        |

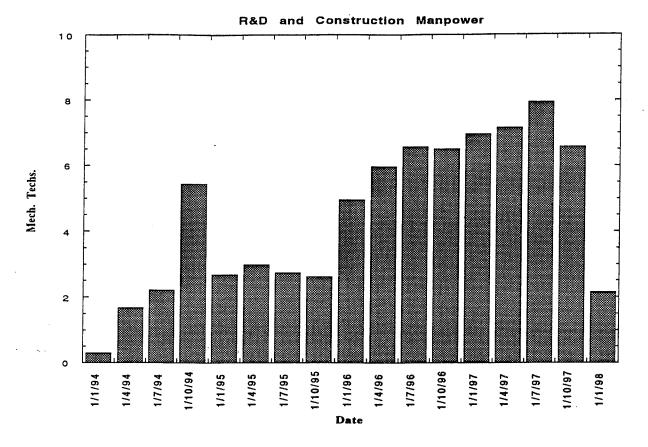

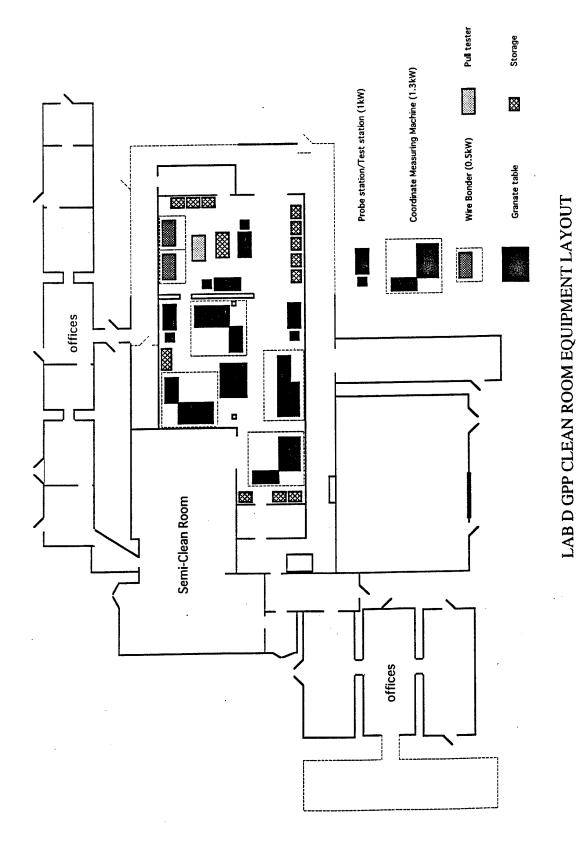

|    |                                 | 10.2.3 Manpower                                                                                                                                                |

|    |                                 | 10.2.4 Facilities                                                                                                                                              |

0

•

.

# 3

# Chapter 1

# **Overview and Physics Motivation**

## **1.1** Introduction

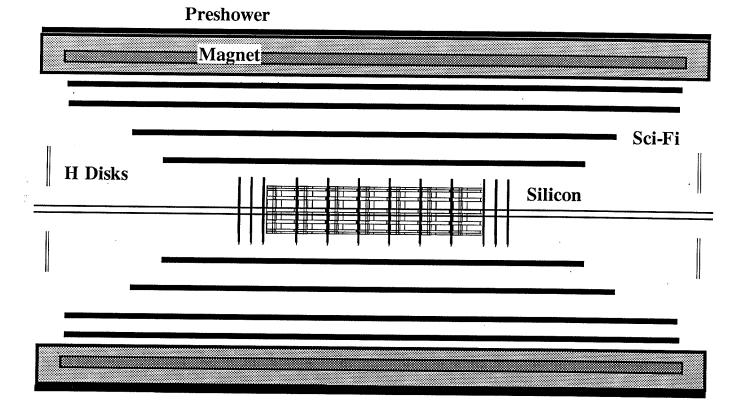

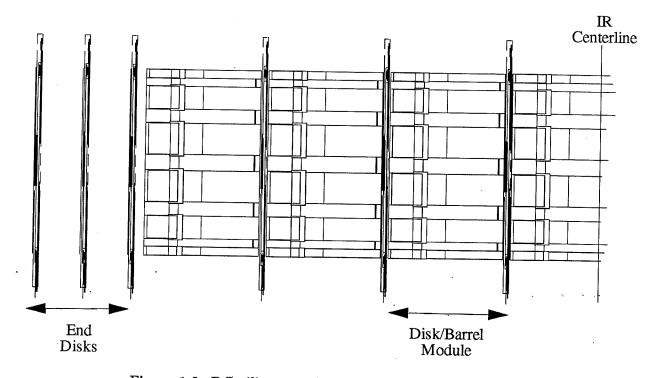

DØ was designed with the goals of efficient identification of leptons and jets over a wide rapidity region. This was achieved by using fine grained, hermetic electromagnetic and hadronic calorimetry, muon detection using thick magnetized iron, and non-magnetic inner tracking. Over changing running conditions and detector technology, we have tried to maintain our basic philosophy of full coverage for lepton and jet identification. The DØ upgrade (Fig. 1.1) extends the capability of the detector to include track momentum determination and vertexing while maintaining angular coverage to  $\eta = \pm 3$ . In addition to the silicon tracker discussed in this report the upgrade includes:

- A 2 Tesla superconducting solenoid magnet

- Four superlayers (xuvx) of scintillating fiber tracking

- A preshower detector surrounding the solenoid

- New muon system and calorimeter electronics

- Improvements to the trigger and DAQ systems

In this way  $D\emptyset$  can continue to address a wide range of collider physics topics into the next century.

## **1.2** Physics Goals

Over the next decade the collider program is likely to have a dual emphasis: top and high- $p_t$  physics, as well as lower  $p_t$  beauty and QCD physics. The two kinematic regimes impose different demands on the detectors. Our silicon tracker design represents a compromise between these two regions.

A wide range of studies have been performed on the physics capabilities of the upgraded  $D\emptyset$  detector [1, 2, 3, 4, 5] addressing a range of physics topics. We summarize here some of the physics topics which drive the design.

## 1.2.1 Top Physics

The primary role that the silicon tracker will play in top physics is *b*-jet identification. In the standard model top quarks will decay primarily through the  $t \rightarrow Wb$  mode. Backgrounds include W + jet and QCD events. W's can decay to leptons or jets, with a small fraction of *b*-jets. The detector will be asked to:

- Separate  $t\bar{t} \rightarrow lepton + b\bar{b} + W(\rightarrow 2 \ jets)$  from the background process  $W \rightarrow lepton + 4 \ jets$ .

- Identify the b-jet in top events to reduce combinatorics in top quark mass calculations.

- Identify electrons, muons, and tau leptons from both b and W decay.

Top jets are the most challenging environment for the  $D\emptyset$  tracking system. The very high top mass implies dense, collimated jets of particles at low values of rapidity. These considerations drive us to a redundant system in the central rapidity region with multiple layers and small angle stereo.

### **1.2.2** Beauty Physics

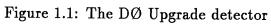

The Tevatron collider is a copious source of B mesons and b physics is likely to become an increasing focus of DØ as we gain the ability to reconstruct track momenta and vertices. B physics differs markedly from high- $p_t$  physics in that the emphasis is on high rates, low to moderate  $p_t$ , and large angular coverage. Figure 1.2 shows the rapidity and momentum distributions of B mesons at the Tevatron.

DØ's b physics goals will include CP violation in a "standard" mode, such as  $B \to \psi K_s$ , as well as modes which  $e^+e^-$  B-Factories will find difficult, such as  $B_s$  mixing. Our superb lepton identification over  $\eta = \pm 3$  is crucial to DØ's b physics plans. For b physics the detector will be asked to:

- Find vertices in three dimensions with good proper time resolution.

- Fully reconstruct multi-prong charm and beauty decay chains.

- Tag "partner" b decays using leptons, vertex reconstruction, or charm identification.

- Trigger on b candidate events using track impact parameters and lepton identification.

It is clear from Fig. 1.2 that forward acceptance is crucial for b physics. The need for full coverage becomes more apparent when one considers that a tag on the partner b, which may be separated in rapidity, is necessary for b physics studies such as mixing and CP violation. The crucial parameter in  $B_s$  mixing studies is lifetime resolution, which translates almost directly to a requirement on vertex resolution.

Figure 1.2: Rapidity and momentum distributions of B mesons produced directly and by the decay of  $140 \text{ GeV}/c^2$  top quarks at the Tevatron.

# **1.3** Tevatron Parameters

The upgraded Tevatron in Run II is expected to have the following parameters:

- Interaction region length of  $\sigma_z \approx 25 \,\mathrm{cm}$ .

- Luminosity of  $10^{32} \text{ cm}^{-2} \text{s}^{-1}$ .

- Crossing interval greater than or equal to 132 ns.

- Beam transverse sigma of less than  $50 \, \mu m$ .

Some of these parameters are expected to vary over the lifetime of the detector, for example the Run IIa crossing interval may be 396 ns, changing to 132 ns in Run IIb.

Each of the machine parameters has an effect on the silicon design. The luminosity sets a scale for the radiation damage expected over the life of the detector, which in turn dictates the operating temperature (see Section 2.3). The long interaction region length sets the length scale, and motivates our disk/barrel design. The crossing interval sets the design parameters for the electronics and readout as well as the probability that multiple interactions occur in a single crossing. Finally the small beam radius compared to a typical B track impact parameter of 300  $\mu$ m means that fast impact parameter triggers can be contemplated.

# 1.4 DØ Silicon Tracker Design

### 1.4.1 Overall Design

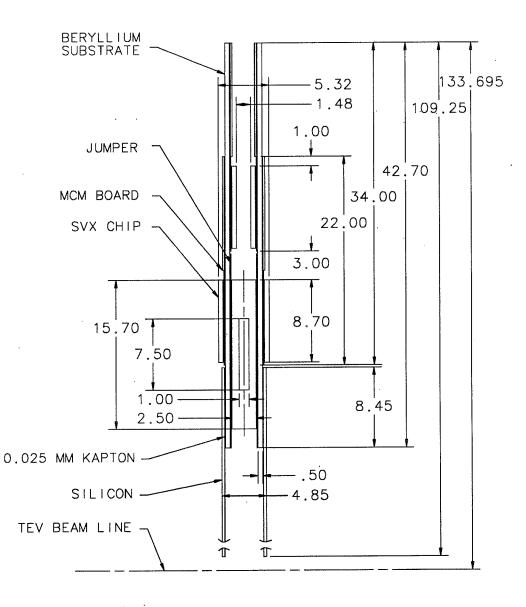

The basic philosophy of the DØ silicon tracker is to maintain track and vertex reconstruction over the full  $\eta$  acceptance of DØ. This task is complicated by the Tevatron environment. In a machine with a point source luminous region the IP could be surrounded by detectors in a roughly spherical geometry. This would allow all tracks to intersect the detector planes at approximately normal incidence and provide optimal resolution. The Tevatron IP has a  $\sigma_z$ of 25 cm. In this situation it is difficult to deploy detectors such that the tracks are generally perpendicular to detector surfaces for all  $\eta$ . This forced us to a hybrid system, with barrel detectors measuring primarily the r- $\phi$  coordinate and disk detectors which measure r-z as well as r- $\phi$ . Thus vertices for high  $\eta$  particles are reconstructed in three dimensions by the disks, and vertices of particles at small values of  $\eta$  are measured in the barrels.

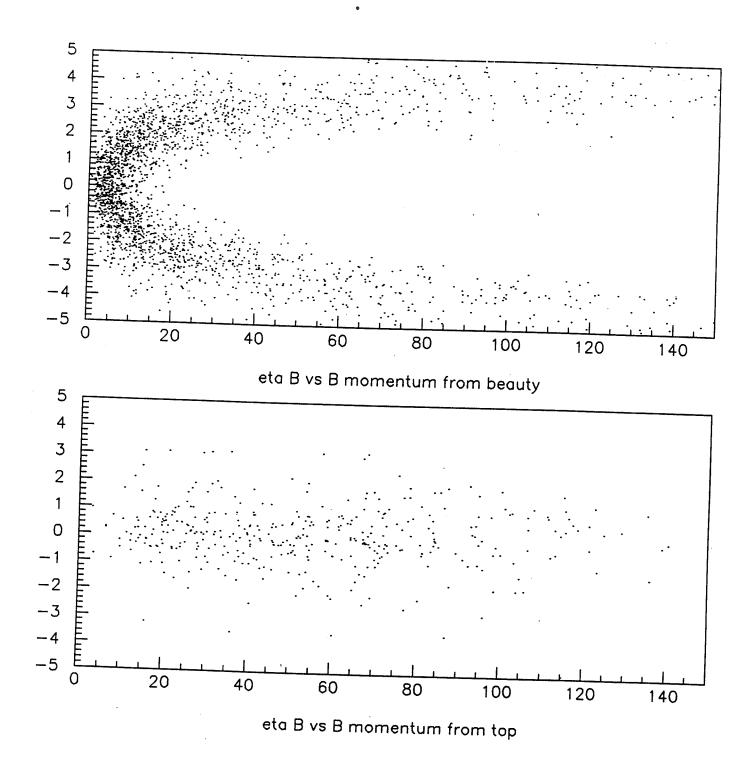

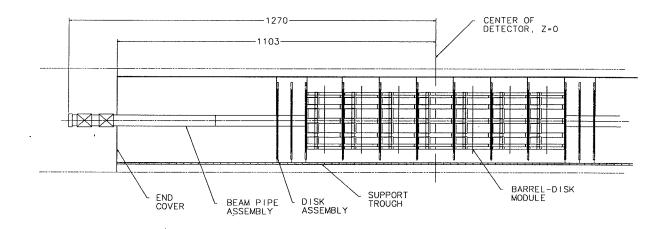

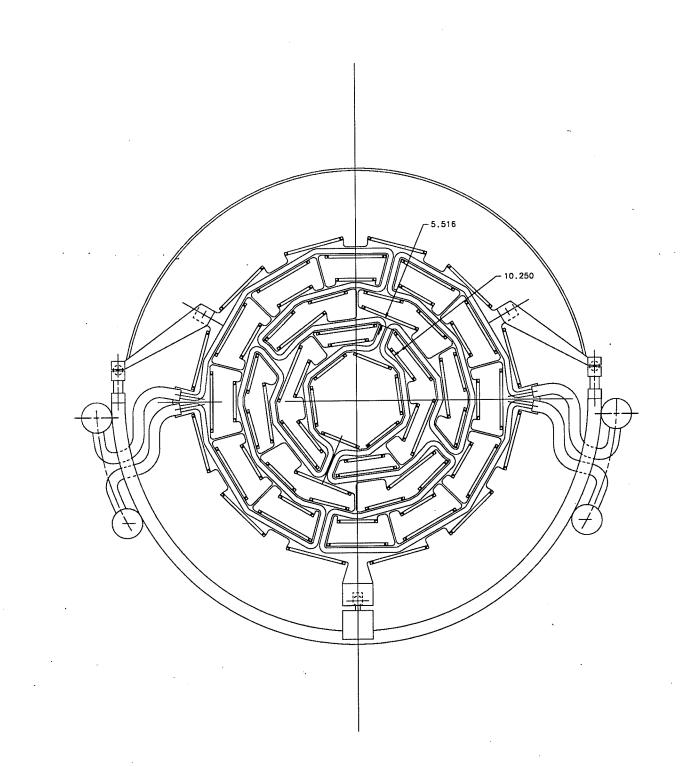

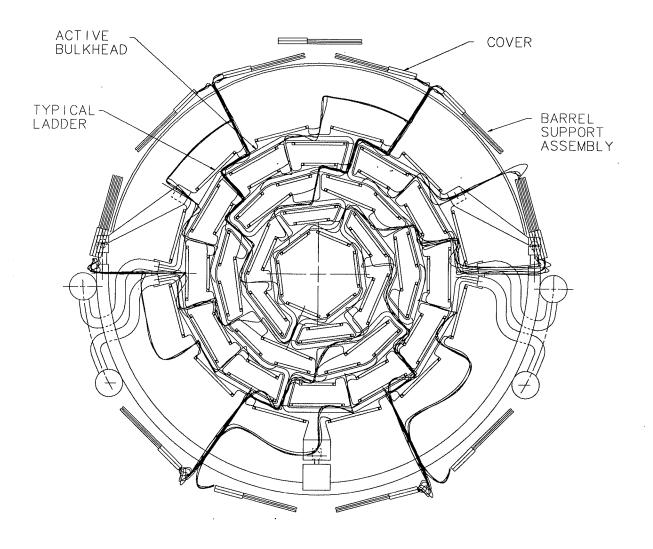

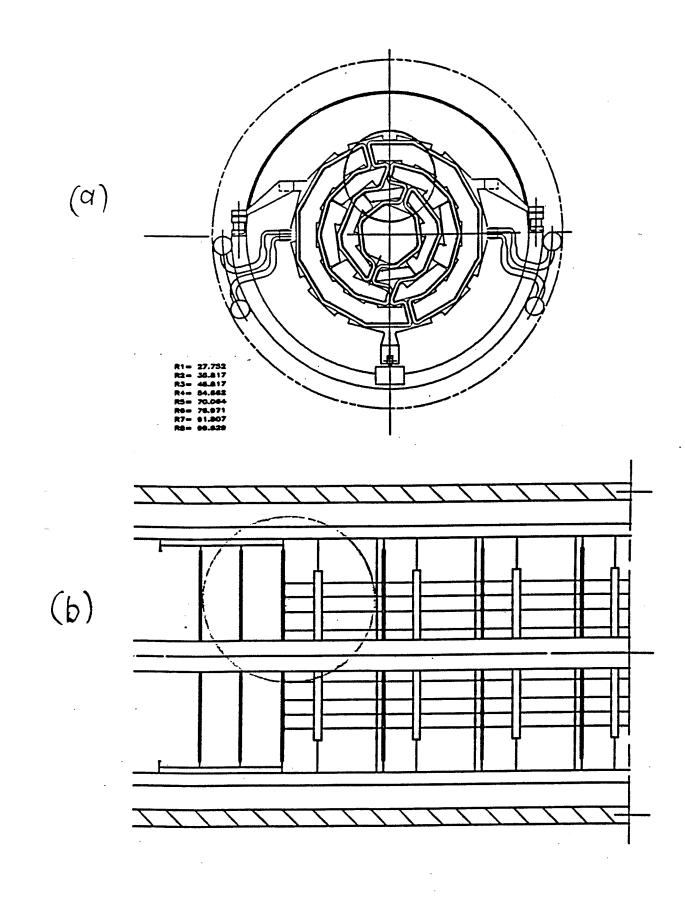

The interspersed barrel-disk design is shown in Fig. 1.3. In such a system the disk separation must be kept small to minimize extrapolation errors. However, each plane of disks also represents a dead region between the barrels which lowers the overall efficiency of the detector. Thus there is a compromise between vertex resolution at large  $\eta$  (1/disk spacing) and efficiency at small values of  $\eta$ .

This design clearly puts a premium on a minimal gap between barrel sections. In our design this gap is minimized in several ways:

1. Inboard mounting of the electronics. The readout electronics and their supports are mounted on top of the active detector surface. This means that extra inter-barrel space is not needed for "ears".

Figure 1.3: DØ silicon tracker interspersed barrel-disk design

- 2. Inboard routing of cables. Cables which supply power, control, and readout bus signals are routed to the outer radius between detector layers rather than off the ends of the ladders.

- 3. Thin disk modules. The disk detectors are designed to be as thin as possible consistent with mechanical rigidity. In these modules the electronics is mounted outboard of the silicon with flexible jumpers to bring the signals to the readout chips.

Finally, the design is constrained by the mass and funding budgets. The detector can not have an infinite length, an infinite number of layers, or an infinite number of channels. Given these onerous constraints we have chosen the following overall geometry:

- 7 barrel segments

- 4 detector layers per barrel

- 2 single-sided layers

- 2 double-sided layers

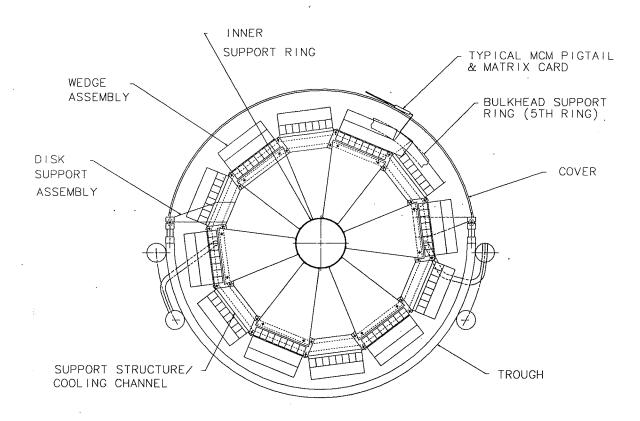

- 12 F (small diameter) double-sided disks

- 4 H (large diameter) single-sided disks

|                                                 | F     | H         | L1             | L2                   | L3        | $\mathbf{L4}$      | TOTAL |

|-------------------------------------------------|-------|-----------|----------------|----------------------|-----------|--------------------|-------|

| # detector sides                                | 2     | 1         | 1              | 2                    | 1         | 2                  |       |

| # assemblies (both sides)                       | 12    | 4         | 7              | 7                    | 7         | 7                  | 44    |

| $\frac{\pi}{R}$ (min) (cm)                      | 2.57  | 9.5       | 2.77           | 4.61                 | 6.83      | 9.16               |       |

| R (max) (cm)                                    | 9.96  | 26        | 3.58           | 5.49                 | 7.52      | 9.99               |       |

| $ z  (min) \text{ or } \langle dz \rangle (cm)$ | 6.4   | 110       | < 12 >         | < 12 >               | < 12 >    | < 12 >             |       |

| $ z  (mm) \text{ or } \langle uz \rangle (cm)$  | 54.8  | 120       | 42             | 42                   | 42        | 42                 |       |

| # ladders/assembly                              | 12    | 24        | 12             | 12                   | <b>24</b> | <b>24</b>          |       |

| $\frac{1}{2}$ Detector length (cm)              | 7.5   | 14.86     | 6              | 6                    | 6         | 6                  |       |

| Min. detector width (cm)                        | 1.673 | 2.42      | 2.115          | 3.395                | 2.115     | 3.395              |       |

| Max. detector width (cm)                        | 5.692 | 6.40      | 2.12           | 3.40                 | 2.12      | 3.40               |       |

|                                                 | 27.62 | 65.53     | 12.72          | 20.4                 | 12.72     | 20.4               |       |

| Detector area $(cm^2)$                          | 50    | 50        | 50             | 50                   | 50        | 50                 |       |

| Strip pitch $(\mu m)$                           | . 8   | 10        | 3              | 5                    | 3         | 5                  |       |

| # IC's/side                                     | . 0   | 2         | 2              | $\overset{\circ}{2}$ | 2         | 2                  |       |

| # detectors/readout unit                        | 1 12  | 2<br>48   | $\frac{2}{24}$ | 24                   | · 48      | 48                 |       |

| # detectors/assembly                            |       | 40<br>192 | 168            | 168                  | 366       | 366                | 1344  |

| # detectors (total)                             | 144   |           | 108<br>149     | 240                  | 299       | 479                | 1885  |

| Silicon mass (g)                                | 278   | 440       |                | 6854                 | 4274      | 13709              | 41222 |

| Sides×area $(cm^2)$                             | 7954  | 7528      | 2137           | 0854<br>24           | 24        | 48                 |       |

| # sets IC's/assembly                            | 24    | 24        | 12             |                      | 168       | 336                |       |

| # sets IC's                                     | 288   | 96        | 84             | 168                  |           | $\frac{350}{1680}$ | 6540  |

| # IC's                                          | 2304  | 960       | 252            | 840                  | 504       |                    | 837   |

| # kchannels                                     | 294.9 | 122.9     | 32             | 108                  | 65        | 215                | 091   |

Table 1.1: Numbers of detectors and geometric parameters of the tracker.

Table 1.1 shows the numbers of detectors and the geometric parameters of the tracker. The 12 cm long barrel segments are separated by 8 mm gaps containing F disks at |z| = 6.4 cm, 19.2 cm and 32.0 cm. Three more F disks are located at each end of the barrel at |z| = 44.8 cm, 49.8 cm and 54.8 cm, as shown in Fig. 1.3. The H disks are located at |z| = 110 cm and 120 cm.

## 1.4.2 Performance Considerations

There has been considerable study of optimum designs for tracking and vertexing systems in a collider environment [6]. The basic concerns are 1) momentum resolution, 2) vertex resolution, 3) r-z measurement, and 4) pattern recognition.

#### Momentum Resolution

Momentum resolution of the tracker is determined by the strength of the magnetic field, its radius, the accuracy of measurement of the helix, and the amount of multiple scattering. We can define an overall figure of merit as the inverse measurement error  $(1/\sigma)$  times the

field integral (BR) in the r- $\phi$  dimension times the lever arm (R), *i.e.*  $BR^2/\sigma$ . The silicon provides an accurate measurement of the track angle at small radius, but the measurement of the sagitta and outer points in the central rapidity region are performed in the fiber tracker. The silicon serves to anchor the track at the inner radius. The number and detailed location of silicon layers does not have a major effect on the momentum resolution.

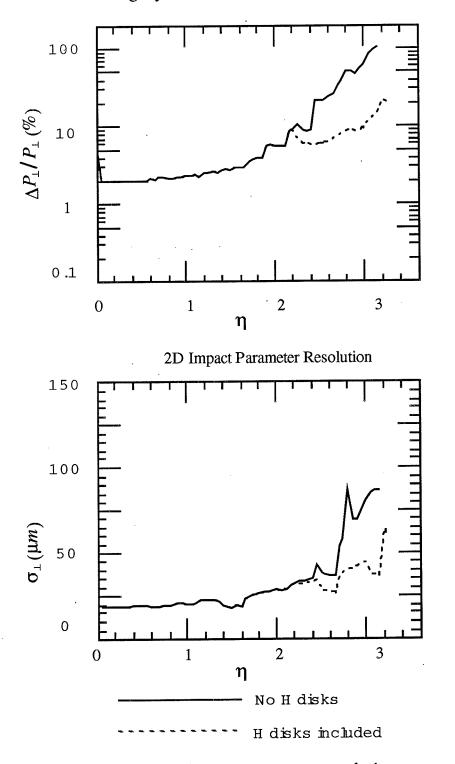

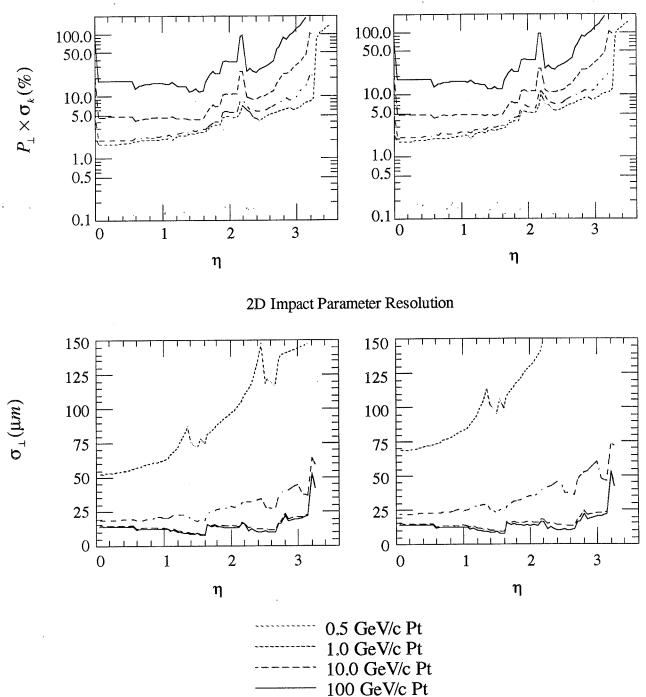

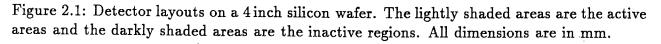

A plot of the momentum resolution as a function of  $\eta$  for a 1 GeV/c  $p_t$  track originating at z = 0 is shown in Fig. 1.4. The solid line shows the resolution for the tracker excluding the H disks. As  $\eta$  increases beyond 1.8, tracks begin to miss the last fiber tracker layer and the effective value of  $BR^2$  decreases, rapidly destroying the momentum resolution. Momentum resolution can only be maintained if the detector resolution also improves as  $1/R^2$  as  $R \to 0$ . We have attempted to preserve momentum resolution in the forward direction by adding large area "H" disks, with  $10 \,\mu$ m resolution, which cover radii less than 26 cm. These disks do not need to have low mass and can be made more cheaply than the delicate "F" disks and ladders. In the region covered by the H disks the resolution is comparable to the fiber tracker for radii  $r > \sqrt{(0.5m)^2 \times \frac{10\,\mu\text{m}}{120\,\mu\text{m}}} = 14 \,\text{cm}$ . The effect of the silicon on the resolution including the H disks is shown in the dashed line in Fig. 1.4.

#### Vertex Resolution

Vertex resolution considerations can be understood by considering a simple two layer silicon system with identical resolution at the inner and outer radii,  $r_1$  and  $r_2$ . The impact parameter resolution is given by:

$$\sigma = \sigma_{meas} \left\{ rac{\sqrt{1 + (r_1/r_2)^2}}{1 - (r_1/r_2)}

ight\}$$

A similar formula holds for disks where  $r_1$  and  $r_2$  are the radii of the first and last hits on a track passing through several disks. We see that the impact parameter resolution is dependent on the ratio of inner to outer radii of the detector. The cost depends strongly on the outer radius.

Given the above considerations we have decided on a compact system with the inner ladders as close to the beam pipe as is mechanically comfortable and with an outer radius which is consistent with deploying four layers of detectors.

Vertex resolution is also affected by the detector resolution,  $\sigma_{meas}$ . This is primarily a function of the detector strip pitch, which is constrained by existing interconnect and amplifier technology. Our strip readout pitch is chosen to be 50  $\mu$ m.

Naively the resolution is the pitch/ $\sqrt{12}$ . In a system where pulse height information is available the resolution is improved by the sharing of charge among two or more readout strips. These charge sharing effects can reduce the resolution from  $14 \,\mu\text{m}$  (*i.e.*  $50 \,\mu\text{m}/\sqrt{12}$ ) to 5–10  $\mu$ m, depending on the amount of sharing. The effective strip pitch can also be reduced by intermediate strips at smaller pitch (25  $\mu$ m) which couple capacitively to the instrumented strips.

Tracking System Pt Resolution (1 GeV/c Pt track)

#### Measurement in r-z

There are two scales relevant to the r-z measurement in the silicon detectors. The first scale is that of the secondary vertices, with impact parameters in the 100  $\mu$ m range. This can only be accomplished with detectors which incorporate large stereo angles (90° is the most straightforward). The other relevant scale is that of the primary vertex measurement. The needs here are determined by the necessity of separating multiple event vertices. This scale is in the several mm-1 cm range. In this case we only need stereo angles of a few (1-4) degrees. We note that for a 2° stereo angle in both the silicon and fiber tracker the angular resolution using the outer fiber tracker layer is about 7 mr and the resolution using the outer and inner silicon layers is about 6 mr.

The r-z resolution also can affect the lifetime, momentum, and mass resolutions of the experiment. If we measure the impact parameter only in the r- $\phi$   $(p_t)$  plane the lifetime can be written as:  $\tau = DL/\gamma c$ . Here  $DL = DL_{\perp}/\cos\theta$  where DL is the decay length,  $DL_{\perp}$  is the decay length measured in the transverse plane, and  $\theta$  is defined from the vertical axis  $(\eta = 0)$ . For  $p_{\perp} \approx m$  the lifetime error due to the r-z  $(\theta)$  measurement is always smaller than 0.4% for  $|\eta| < 1.7$ . The errors in the mass and momentum resolution are also negligible for 2° stereo angles [7].

We have chosen to implement the DØ silicon tracker barrel with small angle stereo only, providing r-z resolution at the vertex of 0.5 - 1 mm, enough to separate primary vertices from multiple events but not enough to be useful for full three dimensional secondary vertex reconstruction unless the disks are involved. Small angle stereo was chosen (and large angle stereo excluded) for several reasons:

- 1. The pattern recognition problems inherent in the extrapolation from the scintillating fiber system to the silicon tracker were such that small angle stereo planes are necessary to resolve ambiguities in the track extrapolation to the silicon. Thus the tracking system must have at least two small angle stereo planes.

- 2. The critical dimension for secondary vertices at low  $\eta$  is  $r \cdot \phi$ . Simulations showed that the high resolution  $r \cdot z$  measurement is not necessary for top physics [7].

- 3. Tracks at moderate to high values of  $\eta$  (> 1.5) would pass through many strips of large angle stereo detectors. This makes pattern recognition difficult and impairs the resolution for these tracks.

- 4. Tracks at  $|\eta| > 1.7$  will be well measured in three dimensions by the disks.

- 5. The implementation of double-sided large angle stereo barrels is technically difficult, requiring either double metalization technology on the detectors or an external fine pitch kapton or glass jumper. This was judged to be too risky.

With a 2° stereo angle and 12 cm barrels there is a triangular dead region which extends from the readout wire-bond to the end of the detector. This area can be as wide as  $12 \text{ cm} \times \tan(2^\circ) = 4 \text{ mm}$  if the wire-bonds are at the edge of the detector. These dead regions can result in a significant loss in *r-z* coverage. This problem can be dealt with either by introducing some sort of a jumper (*i.e.* double metalization as in item 5 above), or by

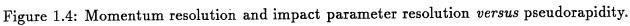

Figure 1.5: Z resolution versus disk stereo angle.

having sufficient overlap to cover the dead regions in the adjacent detector. We have chosen the latter course and in all cases the intra-layer overlap is sufficient to keep the r-z dead area to less than 0.5% of the total active area.

In contrast to the barrels, we intend to use the disks to provide full three dimensional vertex reconstruction. The current disk design, with  $\pm 15^{\circ}$  stereo double-sided detectors, was chosen after careful analysis of the tradeoff between resolution and mechanical complexity. Figure 1.5 shows the *r-z* impact parameter resolution as a function of the disk stereo angle. It is clear that one gains rapidly between 0° and 30° and rather slowly afterward. This drove us to a disk design which has sufficiently large stereo to reconstruct vertices (30°) which also fits on a single double-sided wafer, so no inter-detector wire-bonds are necessary. Tests of these detectors are discussed in Section 2.4.

#### Pattern Recognition

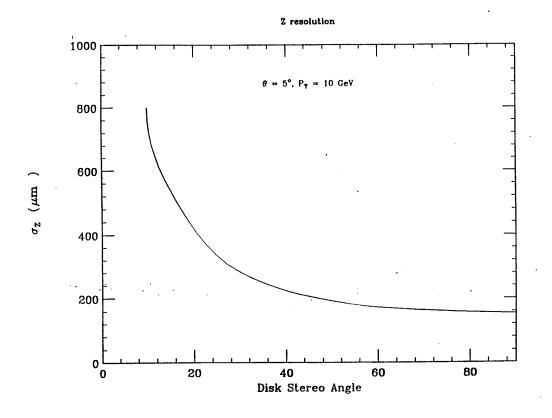

The number of track hits as a function of pseudorapidity for the upgraded tracker is shown in Fig. 1.6. Each fiber superlayer or silicon plane is counted as one hit. DØ has performed extensive studies of the pattern recognition capability of this detector [1, 2, 3, 4, 5, 6]. In these studies much of the pattern recognition is performed in the outer scintillating fiber layers and tracks are extrapolated to the silicon barrels. Studies have also been performed

Figure 1.6: Number of silicon tracker hits versus pseudorapidity.

on pattern recognition in the forward direction using the silicon disks. These results have also been satisfactory [7]. It may be useful to rotate alternate wedge detectors by 15° to break the ambiguities induced by having a number of identical views.

## **1.5 Silicon Tracker Mass Issues**

The amount of material has a dominant effect on the performance of a vertex detector. Multiple scattering in the inner layers of the detector will limit the angular resolution of tracks, affecting the accuracy with which an extrapolated impact parameter can be determined. Material will also affect momentum resolution and cause conversions, bremsstrahlung, and secondary interactions. In the DØ detector design, with short strips in both barrels and disks, the detector volume per amplifier is small. This means that there must be a great deal of attention paid to the mass of the passive elements such as cables and support structures to insure that the mass ratio of passive to active material is not so large that our physics

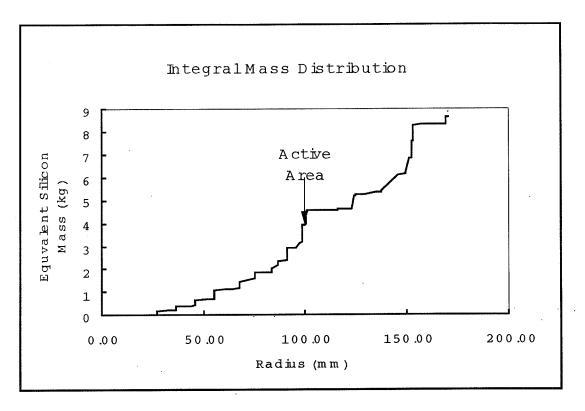

Figure 1.7: Radial distribution of equivalent silicon mass.

goals are compromised.

We have used a large spreadsheet to carefully itemize all significant contributions to the detector mass. Each block of material is characterized by its location, shape, mass, and equivalent silicon mass, *i.e.* mass of material  $\times (L_{rad}/L_{rad}(Si))$ . Table 1.2 summarizes the material contributions from various parts of the detector. The total mass of all silicon detectors is 1.44 kg. The mass of the rest of the detector including supports, cables, and utilities is 7.1 kg. The cables and support structures were considered to extend to |z| = 0.5 m for the purpose of the mass calculation.

In addition to the total mass the radial distribution must be considered to properly understand the physics consequences. Mass at small radii can destroy the impact parameter resolution for low  $p_t$  tracks by smearing the track angle by multiple scattering. Mass at large radii is less harmful. Harmful effects which are independent of radius include conversions and radiation. Figure 1.7 shows the calculated radial distribution of equivalent silicon mass. Much of the mass is concentrated beyond the 10 cm active radius of the silicon. There is a large spike at 16 cm corresponding to the support trough, cables, and matrix cards. To date our Monte Carlo studies have simply taken the active mass distribution and multiplied by factors of between 3 and 6 (Fig. 1.8). In the future we intend to use the detailed mass distribution for further studies of mass effects on detector resolution.

|                             | Mass   | Si Mass | % Mass | % Si Mass | Mass      |

|-----------------------------|--------|---------|--------|-----------|-----------|

| SUBTOTALS                   | [kg]   | [kg Si] | [%]    | [%]       | Silicon · |

| 0 1 2 3                     |        |         |        |           |           |

| Total (including 7 modules) | 14.267 | 9.801   |        |           | 6.80      |

| Detector                    | 8.169  | 5.831   | 57.26% | 59.49%    | 4.04      |

| All Modules                 | 7.192  | 5.142   | 50.41% | 52.47%    | 3.57      |

| Module:                     | 1.027  | 0.735   | 7.20%  | 7.50%     | 0.51      |

| Silicon                     | 0.190  | 0.189   | 18.46% | 25.79%    | 0.13      |

| Ladders                     | 0.167  | 0.166   | 16.21% | 22.64%    | 0.12      |

| Disks                       | 0.023  | 0.023   | 2.25%  | 3.15%     | 0.02      |

| Passive                     | 0.838  | 0.545   | 81.54% | 74.21%    | 0.38      |

| Bulkhead                    | 0.224  | 0.075   | 21.77% | 10.18%    | 0.05      |

| Water Lines                 | 0.024  | 0.017   | 2.37%  | 2.35%     | 0.01      |

| Water in Line               | 0.007  | 0.004   | 0.70%  | 0.59%     | 0.00      |

| Cable Suppor                | 0.018  | 0.016   | 1.73%  | 2.20%     | 0.01      |

| Ladders                     | 0.289  | 0.205   | 28.18% | 27.90%    | 0.14      |

| Disks                       | 0.172  | 0.115   | 16.78% | 15.59%    | 0.08      |

| Pigtails                    | 0.103  | 0.113   | 10.00% | 15.40%    | 0.08      |

| End Disks                   | 0.978  | 0.688   | 6.85%  | 7.02%     | 0.48      |

| Water Manifolds             | 0.973  | 0.641   | 6.82%  | 6.54%     | 0.44      |

| Half Cylinder               | 2.987  | 1.443   | 20.94% | 14.73%    | 1.00      |

| Half Cylinder Supports      | 0.057  | 0.095   | 0.40%  | 0.97%     | 0.07      |

| Cables                      | 1.017  | 0.933   | 7.13%  | 9.52%     | 0.65      |

| Matrix Cards                | 0.951  | 0.821   | 6.66%  | 8.38%     | 0.57      |

| Beam Pipe                   | 0.113  | 0.038   | 0.79%  | 0.39%     | 0.03      |

Table 1.2: Material contributions from silicon tracker parts.

# 3 x Silicon Mass

# 6 x Silicon Mass

Tracking System Pt Resolution

Figure 1.8: Momentum resolution versus pseudorapidity with "scaled-up" active mass distribution included.

# Bibliography

- [1] R&D and Optimization Progress Report, D0 Note 1322 (1992).

- [2] Step 1 and Beyond, D0 Note 1421 (1992).

- [3]  $D\theta_{\beta}$ , D0 Note 1733 (1992).

- [4] Magnetic Tracking, D0 Note 1933 (1993).

- [5] Electron ID, D0 Submission to the PAC (January, 1994).

- [6] S. Mishra and P. McBride, *B Physics at Hadron Colliders*, Proceedings of the 1993 Snowmass Workshop (1993).

- [7] D0 Note 1846 (1993).

# Chapter 2

# Silicon Detectors

# 2.1 Design and Specification of Silicon Detectors

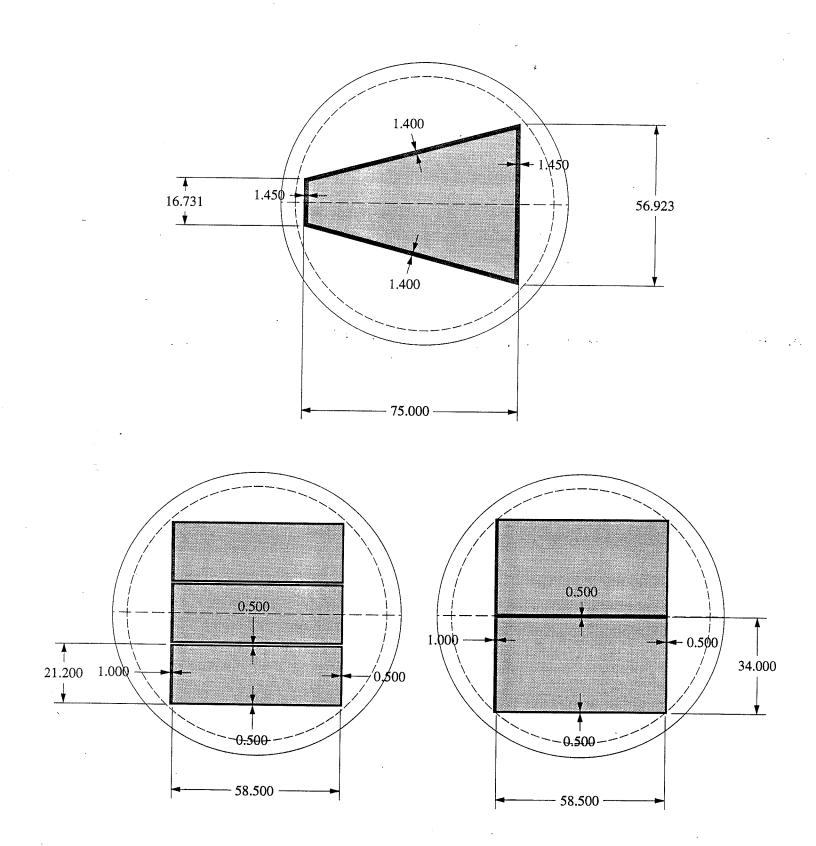

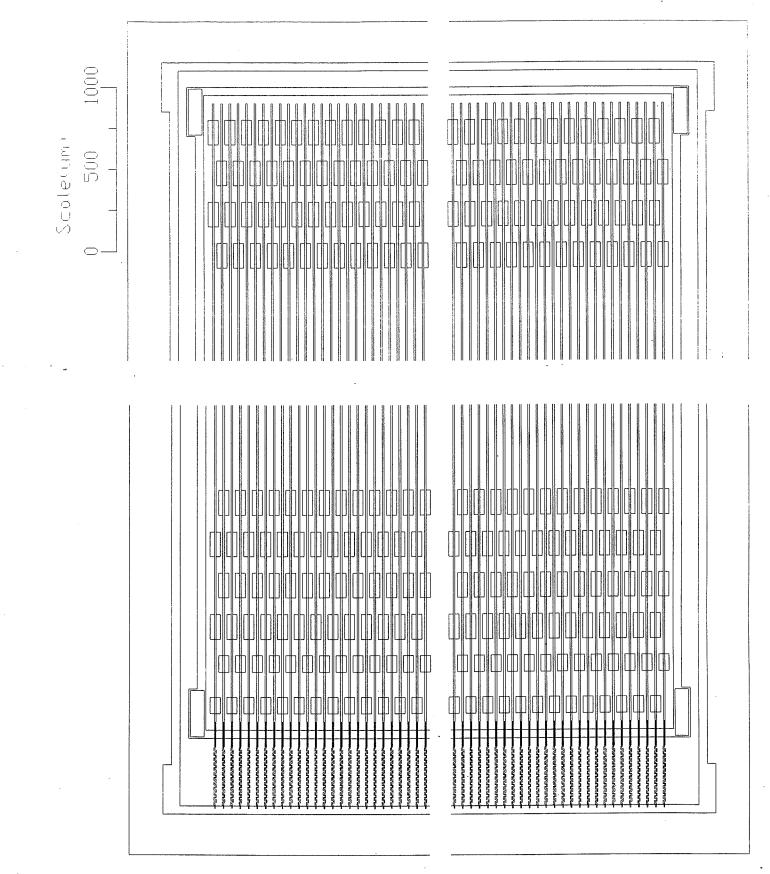

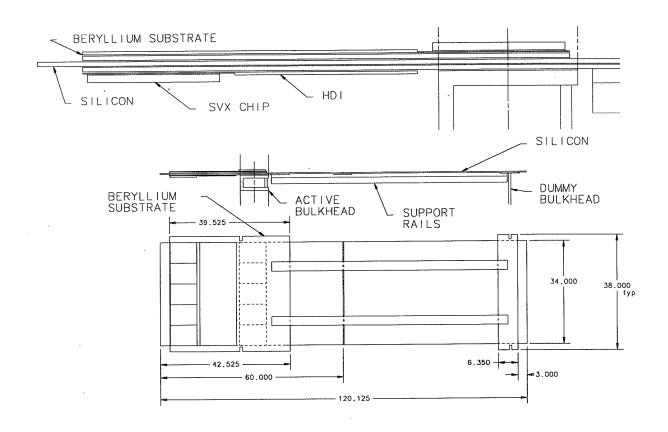

The DØ silicon tracker geometry requires three different types of silicon detectors. In the barrel there are two types: a single-sided detector with 384 strips and dimensions  $60 \text{ mm} \times 21.2 \text{ mm}$ ; and a double-sided detector with 640 strips per side and dimensions  $60 \text{ mm} \times 34.0 \text{ mm}$ . These detectors are designed to be read out by three SVX-II chips or ten SVX-II chips (five on each side) respectively. The other detector type is a double-sided wedge-shaped detector with 1024 strips on each side. Twelve of these detectors are assembled to form a complete  $360^{\circ}$  disk. The wedge detectors are read out by eight SVX-II chips on each side.

Figure 2.1 shows the layout of the barrel detectors and the wedge detector on 4 inch silicon wafers. Only one wedge detector can be accommodated on a single wafer, whereas three of the narrow barrel detectors or two of the wider barrel detectors can be fabricated on a single wafer. The detectors are arranged to fit inside a 9 cm diameter circle to optimize the yield in fabrication. The 1 cm peripheral area is used for wafer handling during processing.

The design of the H disks has not yet been finalized. Our cost estimate is based on a design where the disks are composed of 24 wedge assemblies of two detectors each. Each wedge would be read out by ten SVX-II chips. We expect to finalize the H disk design this summer with our colleagues from Moscow State University. In the remainder of this chapter we will discuss only the barrel and F disk detectors.

## **2.1.1 Detector Specifications**

The design specifications for the silicon detectors [1] are summarized in Table 2.1. The strip pitch is  $50 \,\mu\text{m}$  for all detector types. This was chosen to give good position resolution  $(\leq 10 \,\mu\text{m})$  and to match the pitch of the SVX-II readout electronics. For the double-sided detectors, stereo strips are used to give 2-dimensional hit information.

The detector specifications are designed to ensure minimum noise in the readout electronics and maximum radiation tolerance. The details of the detector design are discussed below.

(1) Size

Wafer size Thickness Flatness *wedge detectors:* Detector shape Height Base width Top width Dead regions *barrel detectors:* Detector shape Dimensions (narrow detectors) Dimensions (wide detectors) Dead regions

(2) Strip GeometryStereo angleReadout strip pitchBond pad pitch

(4) Electrical Specifications

Depletion voltage

Active area leakage current

Breakdown voltage

Guard ring leakage current

Coupling capacitance

Coupling capacitor breakdown voltage

Interstrip resistance on n-side

Polysilicon resistor value

Percentage of strips meeting specifications

Radiation hardness

4-inch 300 ± 15 μm ≤ 20 μm

Trapezoidal 75.000 mm 56.923 mm 16.731 mm 1.40 mm (sides), 1.45 mm (base, top)

Rectangular 60.000 mm × 21.200 mm 60.000 mm × 34.000 mm 0.5 mm (sides), 1.00 mm (bias end)

± 15° (wedges), 0° and 2° (barrels)

50 μm (perpendicular to strips)

51.764 μm (wedges), 50 μm (barrels)

$35 \pm 15 \text{ V}$   $\leq 120 \text{ nA/cm}^2 \text{ (measured at FDV*)}$   $> 2 \times \text{FDV (defined at 10\mu\text{A})}$   $\leq 5 \mu\text{A (measured at FDV*)}$   $\geq 25 \text{ pF/cm}$   $\geq 100 \text{ V (defined at 2nA)}$   $\geq 2 \text{ M}\Omega$   $2.0 \pm 0.5 \text{ M}\Omega$   $\geq 99.5\%$  > 3 Mrad charged particles  $> 10^{13} \text{ neutrons / cm}^2$

\* FDV = Full Depletion Voltage

Table 2.1: Design specifications for the DØ silicon microstrip detectors.

Figure 2.2: Layout of the strips on a double sided-wedge detector.

## 2.1.2 Wedge Detectors

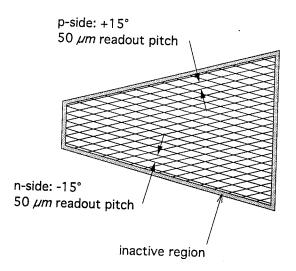

The wedge detectors are double-sided with height 7.5 cm, active area  $24.5 \text{ cm}^2$  and 1024 readout strips on each side. The readout pitch is  $50 \,\mu\text{m}$  on both sides. The strips on the p-side are at a stereo angle of  $+15^\circ$  and those on the n-side are at  $-15^\circ$ . The strip length varies across the detector, as shown in Fig. 2.2. To avoid dead regions and to aid in alignment, there is an overlap of  $707 \,\mu\text{m}$  between the active regions of neighboring wedges.

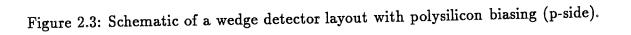

The detectors are fabricated on n-type silicon of thickness  $300 \,\mu\text{m}$  and resistivity >5 k $\Omega$ cm. They are ac-coupled to the readout electronics by capacitors integrated directly onto each strip. The capacitor is formed by a thin dielectric layer between the strip implant and the aluminum metallization. Polysilicon resistors are used to bias the strips since this technology has been shown to be radiation hard [2, 3]. Prototypes of the wedge detectors have been fabricated and tested (see Section 2.2).

Figure 2.3 shows a schematic of the p-side of the wedge detector mask layout. The  $p^+$  strips are at a pitch of 50  $\mu$ m. The strips are metallized and the bond pads are angled at 15° to allow parallel wire-bonding to the SVX-II chips. The effective bonding pitch is 51.8  $\mu$ m. On the n-side, the n<sup>+</sup> implants are at a pitch of 50  $\mu$ m. On both sides, the implanted strips are connected via polysilicon resistors to a bias line. The polysilicon resistors have a nominal design value of 2 M $\Omega$ . Two sets of bond pads, offset by 2 mm, were provided on the prototypes to allow us to support the region underneath the bond pads during ultrasonic wire-bonding.

The nominal implant strip width for the readout strips on the p-side and n-side is  $10 \,\mu$ m. This value was chosen to give a small interstrip capacitance and a reasonably large value for the coupling capacitance. The coupling capacitors are formed by growing a 200 nm silicon dioxide layer over the strip.

It is well-known that for n-type bulk silicon, the positive fixed oxide charge can create an accumulation layer at the silicon surface, causing a very low impedance path between neighboring  $n^+$  strips. To circumvent this,  $p^+$  isolation implants have been introduced between the  $n^+$  strips in the prototypes fabricated at Micron Semiconductor. The width of this im-

Figure 2.4: Cross-section of the double-sided detector design. All dimensions refer to the mask design and are in microns.

plant  $(24 \,\mu\text{m})$  was chosen to be as wide as possible to achieve a low interstrip capacitance [4]. Figure 2.4 shows a schematic cross-section through the silicon wafer transverse to the strip direction for the prototype wedge detectors. For the final detectors we may need to increase the strip width to obtain a higher coupling capacitance. In this case, the intermediate strips on the p-side would be omitted.

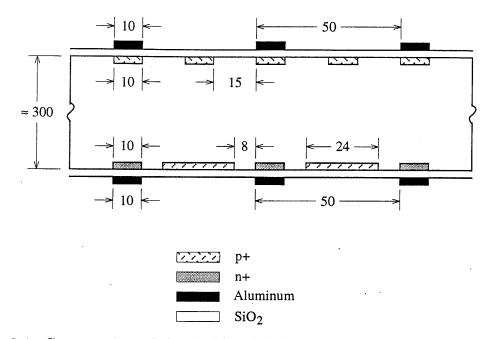

#### **2.1.3** Barrel Detectors

The barrel detectors are 6 cm long with 50  $\mu$ m readout pitch. The strips on the n-side are parallel with the p and  $\bar{p}$  beams (*i.e.* axial) and those on the p-side are at a stereo angle of 2°. Apart from the different detector shape and stereo angle, the design of these detectors is similar to that of the wedge detectors described above. A schematic mask layout for the barrel detectors is shown in Fig. 2.5.

A barrel ladder is constructed by wire-bonding two detectors together to give a total active strip length of 11.7 cm. Bond pads are therefore provided at both ends of the detector as shown in Fig. 2.5. The pads at the end of the detector containing the polysilicon biasing will be used to bond to the SVX-II readout electronics and those at the opposite end will be used for bonding to the second detector.

## 2.2 **Results from Wedge Detector Prototypes**

In this section we describe the results from measurements on the prototype wedge detectors [5]. We have concentrated our efforts on these detectors since they are more novel than

Figure 2.5: Schematic of a barrel detector layout (axial strip side).

Figure 2.6: Total detector capacitance versus bias voltage for a prototype wedge detector.

the barrel detectors. The mask designs for these detectors were done by the UC Riverside group in close collaboration with the detector manufacturers. Two sets of prototype wedge detectors have been fabricated, one set at Micron Semiconductor, UK [6] (11 detectors) and another at SINTEF SI, Norway [7] (9 detectors). Unless specifically indicated, all of the results here refer to the detectors fabricated by Micron, since these detectors met all our design specifications (Table 2.1.)

### 2.2.1 Depletion Voltages

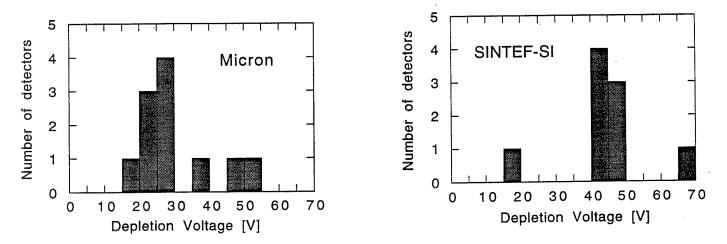

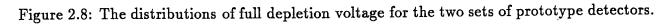

A measurement of the full depletion voltage is necessary to determine a suitable operation voltage for the detectors. Since it is desirable that all detectors in a barrel layer or F-disk have approximately the same operation voltage, we require the detector depletion voltages to be uniform to within  $\pm 15$  V.

We have determined the full depletion voltages of the prototype detectors by capacitance measurements directly on the detectors, without the need for test structures. Although the measurements show a dependence on frequency, this is well understood and we were able to extract the full depletion voltage from these measurements.

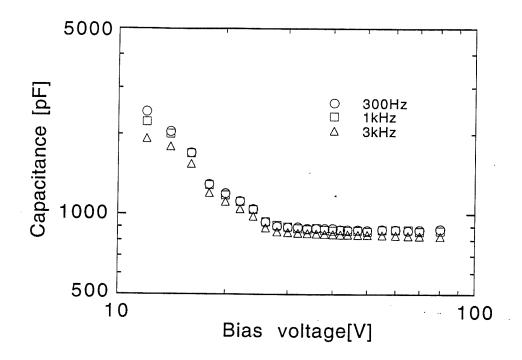

Figure 2.6 shows the measured capacitance versus bias voltage for one of the prototype wedge detectors. The data show the expected behavior

$$C \propto \frac{1}{\sqrt{V_{\text{bias}}}}$$

(2.1)

for an abrupt pn junction [8]. At full depletion the capacitance becomes roughly constant, although it continues to fall very slowly due to edge effects.

Figure 2.7: A plot of  $1/C^2$  versus bias voltage for a prototype wedge detector.

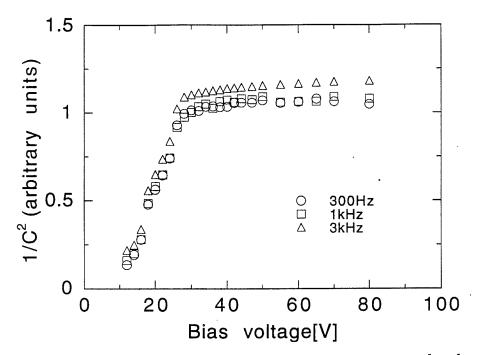

This behavior is more clearly seen if  $1/C^2$  is plotted against the bias voltage as in Fig. 2.7. Note the clearly visible change in slope at full depletion  $V_{dep}$ . The distributions of the depletion voltages for the two sets of prototype detectors are shown in Fig. 2.8.

### 2.2.2 Leakage Current and Breakdown Voltage

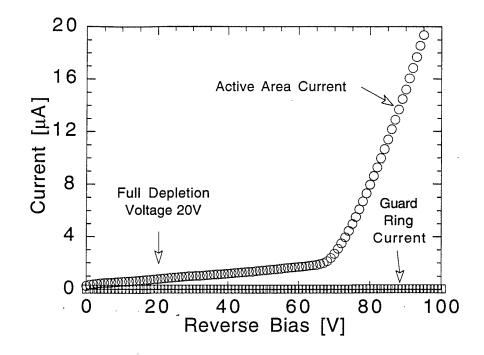

Shot noise due to the detector leakage current contributes to the overall noise of the readout electronics and should therefore be minimized in the detector fabrication process. Figure 2.9 shows a measurement of active area leakage current versus bias voltage for one of the wedge

Figure 2.9: Active area leakage current versus applied voltage.

detector prototypes. The breakdown voltage (defined at a current of  $10 \,\mu\text{A}$ ) is approximately 85 V, well above the full depletion voltage (20 V).

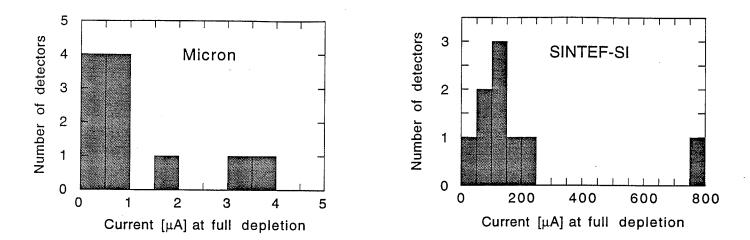

The distributions of leakage currents at full depletion for the two sets of prototype detectors are shown in Fig. 2.10. In our specifications we require that the active area leakage current per unit area be less than  $120 \text{ nA cm}^{-2}$ . For the wedge detectors this is equivalent to a total current of about  $3\mu\text{A}$ , or 3 nA per strip. The leakage current shot noise is then negligible compared with the series noise due to the detector capacitance.

A summary of the prototype measurement results is given in Table 2.2.

## 2.2.3 Coupling Capacitors

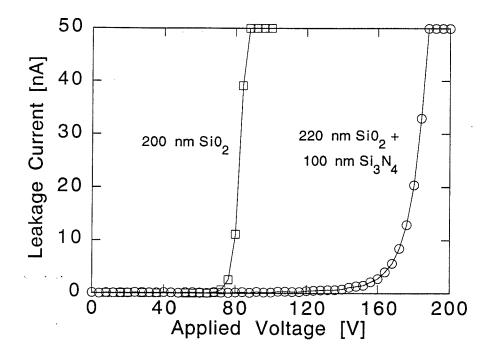

#### (a) Breakdown voltage

One of the important design parameters of the detectors is the breakdown voltage of the coupling capacitors. This must be well above the detector full depletion voltage to ensure reliable long term operation. Also, since the depletion voltage increases with time due to radiation damage, a high coupling capacitor breakdown voltage is necessary to ensure radiation hardness.

The breakdown of the coupling capacitor was measured with probes on the detector, one connecting to the aluminum strip and the other to the dc contact pad connecting to the strip implantation for the same strip. The leakage current as a function of applied voltage was measured for two types of capacitors, one with a silicon dioxide dielectric, the other with both silicon dioxide and silicon nitride, as shown in Fig. 2.11. A current limit of 50 nA

| Detector   | $V_{ m dep}$ | I @ $V_{dep}$ | $V_{ m op}$ | I @ $V_{\rm op}$ |

|------------|--------------|---------------|-------------|------------------|

|            | [V]          | $[\mu A]$     | [V]         | $[\mu A]$        |

| MSL-905-1  | 18           | 0.300         | 23          | 0.370            |

| MSL-905-9  | 35           | 0.560         | 40          | 0.590            |

| MSL-935-18 | 49           | 3.600         | 54          | 3.800            |

| MSL-935-23 | 50 ·         | 3.400         | 55          | 3.700            |

| MSL-969-02 | 29           | 0.450         | 34          | 0.500            |

| MSL-969-11 | 27           | 0.500         | 32          | 0.550            |

| MSL-969-12 | 25           | 0.460         | 30          | 0.540            |

| MSL-969-13 | 24           | 0.675         | 29          | 0.700            |

| MSL-969-15 | <b>20</b>    | 0.800         | 25          | 1.000            |

| MSL-969-16 | 28           | 0.440         | 32          | 0.450            |

| MSL-969-22 | 23           | 1.800         | 28          | 2.500            |

| SI-1024-00 | 65           | 750           | 70          | 900              |

| SI-1024-02 | 47           | 120           | 52          | 150              |

| SI-1024-15 | 18           | 0.200         | 23          | 0.280            |

| SI-1024-26 | 42           | 60            | 47          | 70               |

| SI-1024-31 | 44           | 170           | 49          | 230              |

| SI-1024-33 | 45           | 240           | 50          | 250              |

| SI-1024-41 | 47           | 120           | 52          | 140              |

| SI-1024-42 | 40           | 130           | 45          | 160              |

| SI-1024-47 | 44           | 85            | 49          | 110              |

Table 2.2: Summary of bulk test results.  $V_{dep}$  is the full depletion voltage and  $V_{op}$  is defined to be  $V_{dep}$  + 5 Volts. I @  $V_{dep}$  and I @  $V_{op}$  are the active area leakage currents measured at  $V_{dep}$  and  $V_{op}$  respectively.

Figure 2.10: The distributions of active area currents at full depletion for the two sets of prototype detectors.

was imposed to avoid damage to the capacitors. The simple silicon dioxide capacitors have a breakdown voltage of 80 V. For the final detectors we will increase this to 100 V by increasing the thickness of the oxide layer.

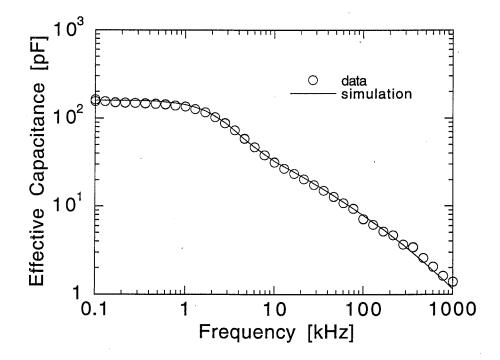

#### (b) Capacitance

To avoid loss of signal from the detector we require  $C_C \gg C_D$ , where  $C_C$  is the capacitance of the coupling capacitor and  $C_D$  is the detector strip capacitance. This requirement is a trade off with the requirement of high capacitor breakdown voltage. For the prototype wedge detectors, we used a 200 nm silicon dioxide layer as capacitor dielectric. For a 10  $\mu$ m strip width, this results in a predicted breakdown of  $\approx 100$  V and a coupling capacitance of  $\approx 17 \text{ pF/cm}$ .

The capacitance of the coupling capacitors was measured with probes on the detector, one connecting to the aluminum strip and the other to the dc contact pad which connects to the strip implantation. The capacitance is shown as a function of measurement frequency in Fig. 2.12 for a typical coupling capacitor. The decreasing effective capacitance with increasing frequency was due to the finite resistance of the strip implantation, which became significant at higher frequencies [9]. This can be well modelled using an equivalent circuit network and it is found that the true capacitance is the value at low frequency. Therefore, the coupling capacitor capacitance can be measured directly, without requiring a test structure. The measured coupling capacitance for the prototype detectors was 160 pF, *i.e.* 21 pF/cm.

### 2.2.4 Bias Resistors

Polysilicon resistor biasing was chosen since this method has been shown to be sufficiently radiation hard. The choice of resistance value is a trade off between minimizing the Johnson noise contribution of the resistor (favoring high values) and minimizing the voltage drop across the resistor due to radiation-induced leakage currents (favoring low values). A design value of  $2 M\Omega$  has been chosen. We estimate a  $2 M\Omega$  resistor will result in a noise contribution

Figure 2.11: Breakdown voltage determination for two types of coupling capacitors.

Figure 2.12: Measured coupling capacitance versus test frequency for a full length (7.5cm) strip. The solid line is a circuit model with the strip implant resistance included.

Figure 2.13: Measurement of the polysilicon resistance for a prototype wedge detector.

of  $131 e^{-1} rms$  (227  $e^{-1} rms$ ) for 132 ns (396 ns) sampling time. Since the expected noise is about 1000  $e^{-1} rms$  (disk detectors), the noise due to the bias resistor will contribute less than 2.5% to the total noise.

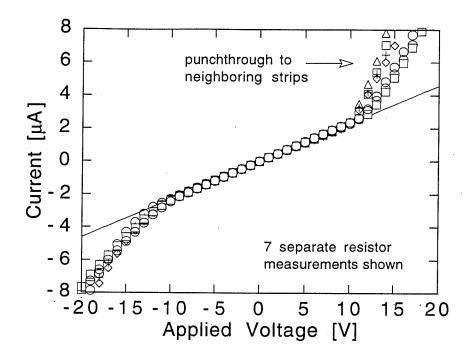

The polysilicon bias resistors were measured by probing the dc contact pads, and observing the current flowing to the bias line as a function of applied voltage. The slope of the resulting line gives the polysilicon resistance as shown in Fig. 2.13. We measured values of  $4.6 \text{ M}\Omega$  for the p-side resistors and  $3.4 \text{ M}\Omega$  for the n-side resistors. The uniformity on each side was within 3%. For the final detectors the manufacturer will be able to tune the polysilicon doping to get the correct value of  $2 \text{ M}\Omega$  on both sides. This was not possible for the prototypes because of the very small number of detectors produced.

## 2.2.5 n-side Interstrip Resistance

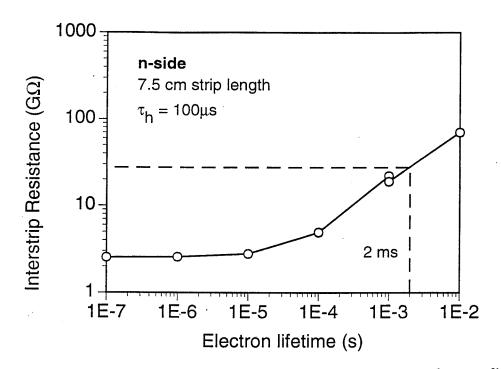

As discussed above, to obtain a high interstrip resistance on the n-side, we used a  $24 \,\mu\text{m}$  width p<sup>+</sup> isolation implant between the n<sup>+</sup> strips. To predict the interstrip resistance for this geometry we have used the simulation tools DIOS [10] and TOSCA [11]. These programs enable a complete simulation of the electrical characteristics of the detectors. Figure 2.14 shows a plot of the calculated interstrip resistance vs. electron lifetime ( $\tau_e$ ) for a fixed hole lifetime ( $\tau_h$ ) of 100  $\mu$ sec. From leakage current measurements, we have estimated the effective lifetime of the prototype detectors to be about 2 msec. The simulation then predicts an interstrip resistance of 25 GΩ.

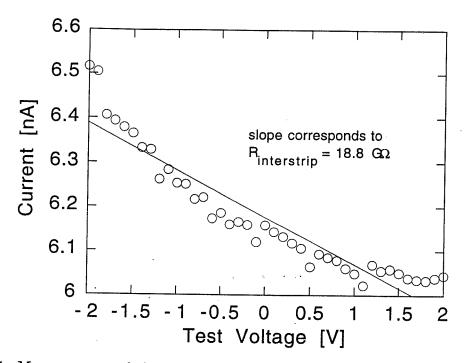

The n-side interstrip resistance for the prototype wedge detectors was measured on a probe station by contacting dc probe pads on the  $n^+$  strips. Figure 2.15 shows a result of such a measurement. The measured resistance is  $20 G\Omega$ , in good agreement with the

Figure 2.14: TOSCA simulation of n-side interstrip resistance vs. electron lifetime for the DØ prototype wedge detectors.

simulation. This demonstrates that the  $p^+$  isolation implantation results in a high n-side interstrip resistance, as expected.

#### 2.2.6 Detector Strip Capacitance

The capacitance at the input of the SVX-II is the total capacitance of one strip of the detector. Our design goal for the capacitance is  $1.6 \, pF/cm$  for the p-side and  $2.0 \, pF/cm$  for the n-side.

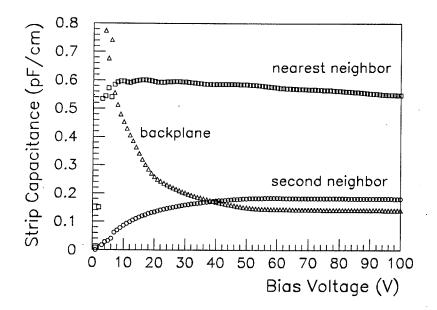

A full TOSCA simulation has been performed in order to model the total strip capacitance. The main contributions to the total capacitance are from the nearest neighbor strips, the second nearest neighbor strips and the backplane. Figure 2.16 shows these contributions as a function of bias voltage for a p-side strip with 50  $\mu$ m strip pitch simulated with TOSCA. Since there are neighbor strips on each side of the strip, the total capacitance is  $2C_1 + 2C_2 + C_b$ , where  $C_1$  is the capacitance to the nearest neighbor,  $C_2$  is the capacitance to the second neighbor and  $C_b$  is the capacitance to the backplane. From the simulations we predict a total strip capacitance of  $1.6 \,\mathrm{pF/cm}$  for the p-side and  $1.8 \,\mathrm{pF/cm}$  for the nside. Table 2.3 shows the predicted capacitances for the n-side and p-side in the disks and barrels. The highest capacitance is that of the n-side strips of the barrel ladders (21 pF). Measurements of the capacitance on prototype detectors are in progress and will soon be completed.

Figure 2.15: Measurement of the interstrip resistance on the n-side of a prototype wedge detector.

Figure 2.16: TOSCA simulation of the contributions to the p-side strip capacitance vs. bias voltage for the D $\emptyset$  prototype wedge detectors.

|        | C (pF/cm) | Barrel<br>C <sub>TOT</sub> (pF) | Disk<br>C <sub>TOT</sub> (pF) |

|--------|-----------|---------------------------------|-------------------------------|

| n-side | 1.8       | 21.0                            | $13.5\\12.0$                  |

| p-side | 1.6       | 18.7                            |                               |

Table 2.3: Total strip capacitance results from TOSCA simulations. The strip length in the barrel ladders is 11.7 cm and in the disks the maximum strip length is 7.5 cm.

# 2.3 Radiation Damage

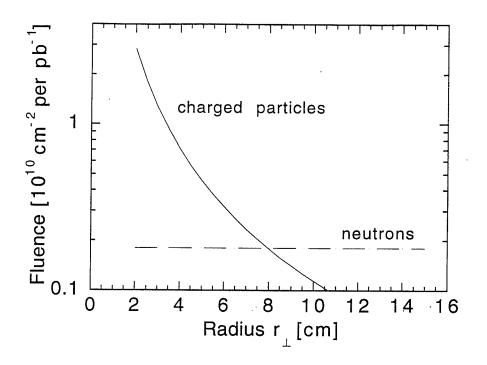

Radiation damage is a primary concern in the design of the silicon detectors. The particle fluences expected at the interaction region of DØ have been calculated in reference [12]. The flux of charged particles varies as  $r_{\perp}^2$ , where  $r_{\perp}$  is the perpendicular distance from the beam line. The flux of neutrons is roughly independent of  $r_{\perp}$ . The calculations are summarized in Fig. 2.17, which shows the expected fluence of charged particles and neutrons for  $1 \text{ pb}^{-1}$  of delivered integrated luminosity.

The important effects of radiation damage are (a) an increase in detector leakage current due to radiation induced generation-recombination centers and (b) a change in depletion voltage due to the creation of effective p-type doping centers.

#### 2.3.1 Increase in Leakage Current

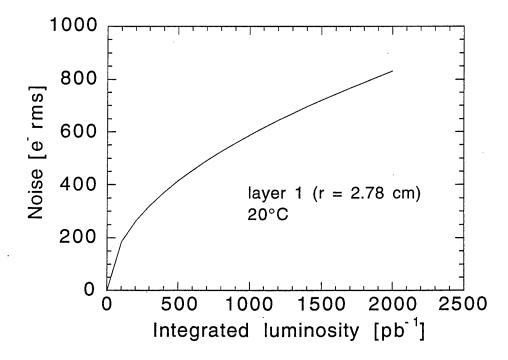

The increase in leakage current results in an increased shot noise contribution to the overall readout electronics noise. We have estimated the noise increase based on measurements of the leakage current damage constants. The worst case noise increase will be in the inner barrel layer which has a strip length of 11.7 cm and radius  $r_{\perp} = 2.78$  cm. This case is illustrated in Fig. 2.18 which shows the equivalent noise charge contribution due to leakage current as a function of delivered integrated luminosity. We have assumed an average detector temperature of 20°C for this calculation and an SVX-II sampling time of 132 ns. As can be seen, after 2000 pb<sup>-1</sup> the total noise for a barrel detector will be about 1400 e<sup>-</sup> before irradiation, the total noise after 2000 pb<sup>-1</sup> will be about 1600 e<sup>-</sup>. This increase in noise will not present a problem for operation of the detectors. In fact, as described below, the limit on the detector lifetime is due to the change of full depletion voltage.

#### 2.3.2 Change of Full Depletion Voltage

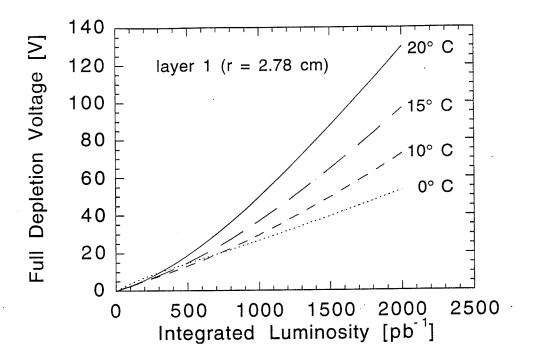

The effect of radiation damage is to create p-type centers in the bulk silicon, thereby changing the effective doping concentration. This causes type inversion of the silicon bulk from n-type

Figure 2.17: Fluence of charged particles and neutrons for  $1 \text{ pb}^{-1}$  as a function of  $r_{\perp}$ .

Figure 2.18: Contribution of radiation-induced leakage current shot noise vs. integrated luminosity for 132 ns sampling time.

Figure 2.19: Predicted full depletion voltage as a function of integrated luminosity and temperature.

to p-type, after which the full depletion voltage increases with particle fluence. This effect has been studied in detail [13] and we are able to estimate the full depletion voltage as a function of run time. Figure 2.19 shows the calculated full depletion voltage for the inner barrel ladder as a function of integrated luminosity delivered to the DØ interaction region. The behavior is temperature dependent because of the effects of "anti-annealing". If we assume that the maximum practical operating voltage is about 100 V, the maximum lifetime of the inner barrel detectors will be approximately  $1500 \text{ pb}^{-1}$  at  $20^{\circ}$ C and  $2000 \text{ pb}^{-1}$  for  $0^{\circ}$ C operation. Note that the F-disks extend to an inner radius of 2.57 cm and operate at a temperature close to  $10^{\circ}$ C. This gives a lifetime of greater than  $2000 \text{ pb}^{-1}$  for the F-disk wedge detectors.

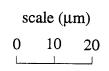

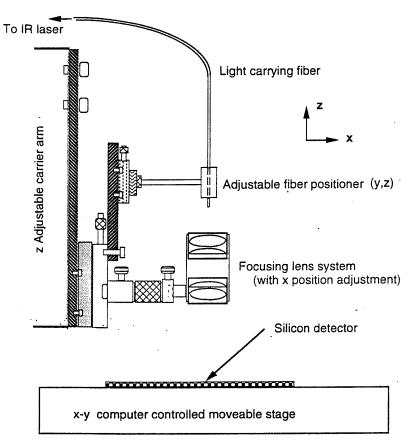

# 2.4 Plans for Production Electrical Testing

In order to ensure all detectors that are used to construct the DØ silicon tracker meet our specifications, we will carry out quality assurance (QA) measurements on detectors. Measurements of the electrical characteristics will be performed first, and measurements of the response of ladder and disk modules to a laser simulating a charged particle will be made after module assembly. In this section we describe the former QA tests.

The measurements will be done on an automated probe station read out by a Macintosh computer. Such a system has already been assembled at UC Riverside and similar systems will be duplicated at Fermilab and at Oklahoma University. The system consists of an automatic probe station, semiconductor source-measure units, a precision LCR meter and a video camera. The system is controlled by GPIB interface to a Macintosh computer. The probe station measurements will consist of a measurement of the following parameters:

- full depletion voltage

- total active area leakage current at the operating voltage

- coupling capacitor short circuits (or low breakdown voltage)

Detectors with similar full depletion voltages will be grouped together for use in the same barrel segment or F-disk. The measurement of coupling capacitor shorts is particularly important. A shorted capacitor results in an excess current into the SVX-II amplifier. This may cause saturation and affect neighboring channels. Therefore, it will be important to identify strips with shorted capacitors (or low capacitor breakdown voltage) and to avoid bonding these channels to the SVX-II readout.

The measurements described above will made on every detector. Other measurements will also be made on a subset of detectors. These include measurements of parameters which are not expected to change from wafer to wafer, but may show variations between different batches of fabrication. These parameters are:

- coupling capacitor capacitance

- bias resistor resistance

- interstrip resistance

- interstrip capacitance

The results of all QA measurements will be entered into a comprehensive database so that the parameters of any detector in the  $D\emptyset$  silicon tracker can easily be accessed.

# Bibliography

- [1] J. Ellison, Full specification for D0 silicon detectors, D0 Note 2075, January 19, 1994.

- [2] D. D. Pitzl et al., Study of Radiation Effects on AC-coupled Silicon Strip Detectors, Proceedings of the 2nd Conference on Advanced Technology and Particle Physics, Como, 1990, Nucl. Phys. B. (Proc. Suppl.) 23A (1991) 340.

- [3] H. J. Ziock et al., Tests of the Radiation Hardness of VLSI Integrated Circuits and Silicon Strip Detectors for the SSC Under Neutron, Proton and Gamma Irradiation, IEEE Trans. Nucl. Sci. NS-38 (1991) 269-276.

- [4] K. Yamamoto et al., Nucl. Instr. and Meth. A326 (1993) 222.

- [5] J. Ellison, for the DØ collaboration, Silicon Microstrip Wedge Detectors for the DØ Silicon Tracker, Proceedings of the International Symposium on Development and Application of Semiconductor Tracking Detectors, May 22-24, 1993, Hiroshima, Japan, Nucl. Instr. and Meth. A342 (1994) 33.

- [6] Micron Semiconductor, 1 Royal Buildings, Marlborough Road, Churchill Industrial Estate, Lancing, Sussex, BN15 8UN, England.

- [7] SINTEF SI, P.O. Box 124 Blindern, 0314 Oslo 3, Norway.

- [8] S.M. Sze, Physics of Semiconductor Devices, 1981, John Wiley and Sons, New York.

- [9] E. Barberis et al., Capacitances in Silicon Microstrip Detectors, Proceedings of the International Symposium on Development and Application of Semiconductor Tracking Detectors, May 22-24, 1993, Hiroshima, Japan, Nucl. Instr. and Meth. A342 (1994) 90.

- [10] R. Hünlich *et al.*, DIOS Users Guide, Institut für angewandte Analysis und Stochastik, Berlin

- H. Gajewski et al., TOSCA Users guide, Institut für angewandte Analysis und Stochastik, Berlin.

For a brief description of TOSCA see A. Bischoff et al., Breakdown protection and longterm stabilisation for Si-detectors, Nucl. Instr. and Meth. A326 (1993) 27.

- [12] J. Ellison, Radiation levels in DØ and effects on silicon detectors, D0 Note 1155, July 12, 1991.

[13] H. Ziock et al., Temperature dependence of the radiation induced change of depletion voltage in silicon PIN detectors, Nucl. Instr. and Meth. A342 (1994) 96.

# Chapter 3

# **Assembly Alignment Constraints**

## **3.1** Introduction

This section addresses the strip-position tolerances needed to ensure the ability to trigger on tracks arising from the decay of long lived particles and to ensure that the number of constants required for event reconstruction is tractable. Section 3.2 contains a discussion of the physics constraints relevant to the tolerances, and Sections 3.3 and 3.3.1 contain results for the tolerances. Details can be found in reference [1].

## **3.2** Physics Constraints

The main criterion used to constrain the position tolerances is that misalignment effects should be negligible in comparison with intrinsic system resolution. The relevant resolution depends on which phase of data-taking and analysis is under consideration. The trigger-level resolution is set by the size of the interaction region, whereas the resolution scale for event reconstruction is set by the impact parameter of tracks arising from the decay of long-lived particles. Each of these is motivated in the following paragraphs.

The position of the interaction point during Run II will be known to between 20  $\mu$ m and 50  $\mu$ m in the plane transverse to the beam direction, and the angle of the beam with respect to the nominal direction will be known to 100  $\mu$ rad. Because the silicon trigger is to be based on detecting tracks from particles decaying outside of the beam envelope, knowledge of the beam position sets the level below which misalignment effects can be ignored. It is also likely that only partial track-reconstruction will be available to measure the interaction position, emphasizing further the need to limit misalignment effects to less than the beam size.

The main physics goal associated with the silicon detector is tagging the presence of particles containing b-quarks. This will be done either by identifying tracks having a large impact parameter in the plane perpendicular to the beam or by detecting detached vertices arising from the decay of the long-lived mesons and baryons. We thus take the fundamental alignment limit at the event reconstruction level to be the impact parameter resolution in the plane perpendicular to the beam. Monte Carlo studies indicate an impact parameter resolution for high-momentum tracks of roughly 20  $\mu$ m for silicon strips having a 50  $\mu$ m pitch.

In order to assess the impact of detector misalignments, we consider the change in the

| Misalignment            | Tolerance           | Tolerance            |

|-------------------------|---------------------|----------------------|

| Source                  | (Entire Det.)       | (Ladder Segment)     |

| Lateral Shift (ends)    | $25\mu{ m m}$       | $25\mu{ m m}$        |

| <b>Radial</b> Expansion | $170\mu{ m m}$      | $170\mu{ m m}$       |

| $\operatorname{Tilt}$   | $60\mu\mathrm{rad}$ | $420\mu\mathrm{rad}$ |

| Ladder Rotation         | ·                   | $670\mu\mathrm{rad}$ |

Table 3.1: Misalignment values corresponding to the maximum allowed coherent variation for the case in which only global position corrections are available. The half length used in computing the angular requirements is 6 cm for a ladder, and 40 cm for the complete detector. The values in the line labeled "Lateral Shift" and the line labeled "Tilt" are related via Shift = (Tilt) × (half length).

mean of the impact parameter distribution for high-momentum tracks when the detector is moved from its nominal position. Four types of motion give rise to significant effects:

- Coherent lateral shifts of ladders at fixed radius.

- Coherent radial shifts corresponding to changes in the effective radii.

- Coherent tilts of the detector with respect to the beam.

- Angular rotation of one ladder with respect to others. The rotation considered is about the axis perpendicular to the plane formed by the strips in a detector.

We note that although global coherent lateral shifts do not directly affect the alignment criteria, the results obtained are directly applicable to e.g. coherent tilts.

# 3.3 Tolerances Relating to the Trigger System

As discussed in Section 3.2, the trigger-level constraints arise from the knowledge of the beam position. We thus demand that misalignments bias the mean impact parameter by less than  $25\,\mu\text{m}$ , a value equal to half of the beam position error. Two sets of tolerances are derived. The first set is based on the assumption that the only position corrections available to the trigger will be translations of the entire detector. The second assumes the positions of individual ladders can be corrected in real time. Both scenarios assume that no angular corrections are available. Tables 3.1 and 3.2 summarize the tolerances on strip position. The numbers given are absolute upper limits on *coherent* effects. The distributions of impact parameter shifts arising from random effects must have R.M.S. values no larger than  $\sqrt{n} \times$  (*coherent maximum*) on any given quantity. Here, *n* is the number of ladders traversed by a given particle. Based on the current geometry,  $\overline{n} \approx 6$ , giving  $\sigma_{\text{random}} < 2.5 \times$  (*coherent maximum*).

| Misalignment<br>Source  | Tolerance<br>(Ladder Segment)      |  |

|-------------------------|------------------------------------|--|

| Lateral Shift (ends)    | $25\mu{ m m}$                      |  |

| <b>Radial</b> Expansion | Correctable to within $170  \mu m$ |  |

| Wafer Tilt              | $420\mu{ m m}$                     |  |

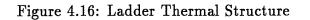

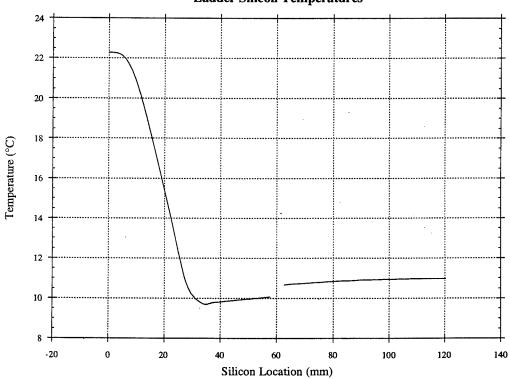

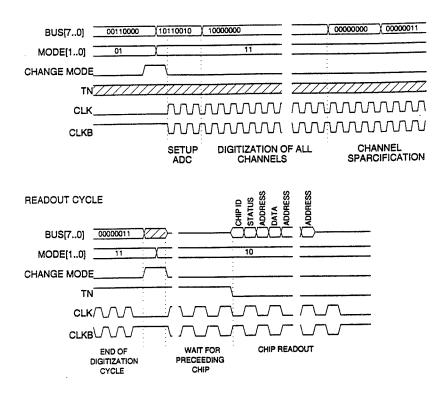

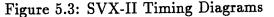

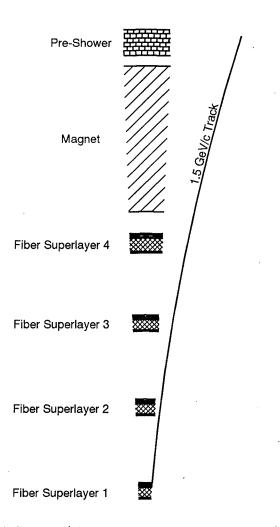

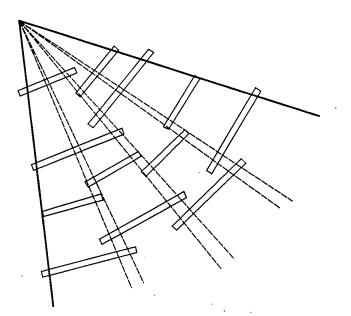

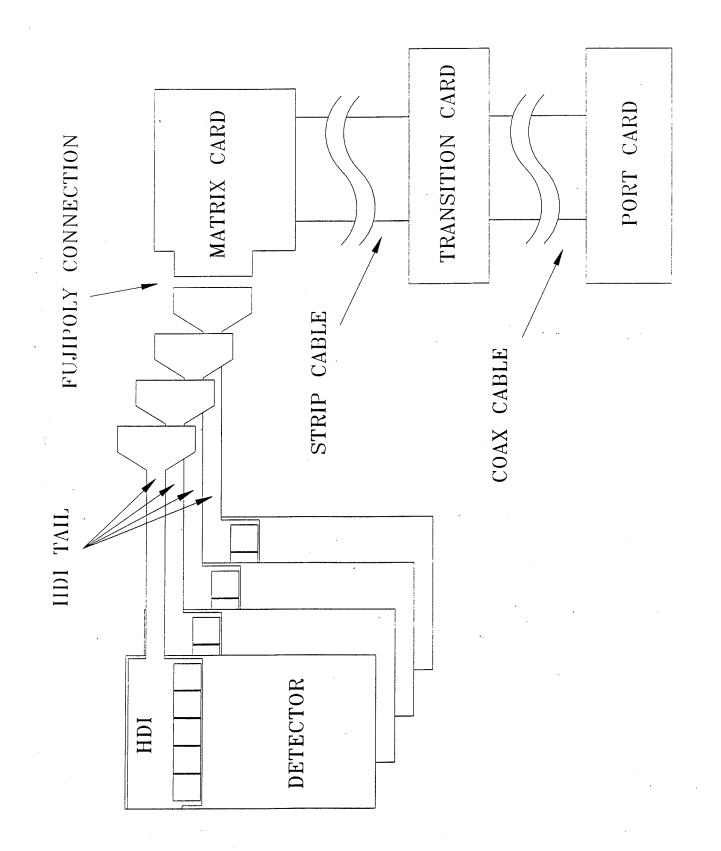

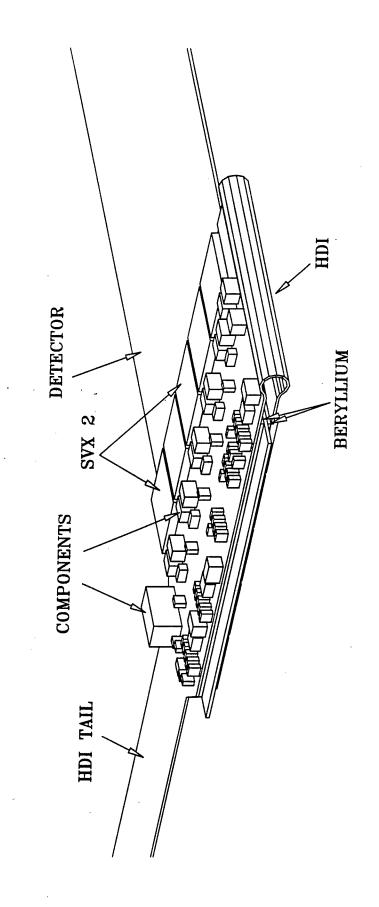

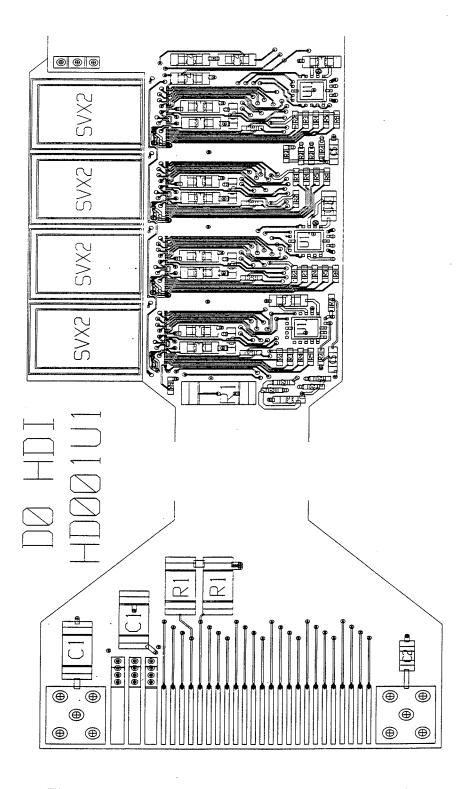

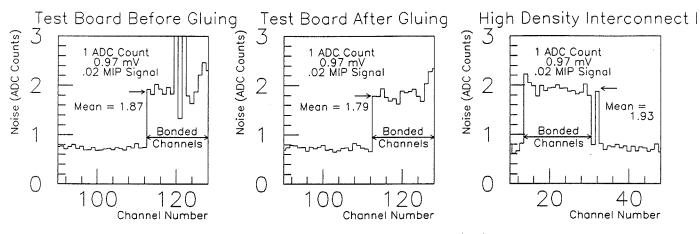

| Wafer Rotation          | $670\mu\mathrm{rad}$               |  |